Manufacturing method of a semiconductor integrated circuit device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as charge escape

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

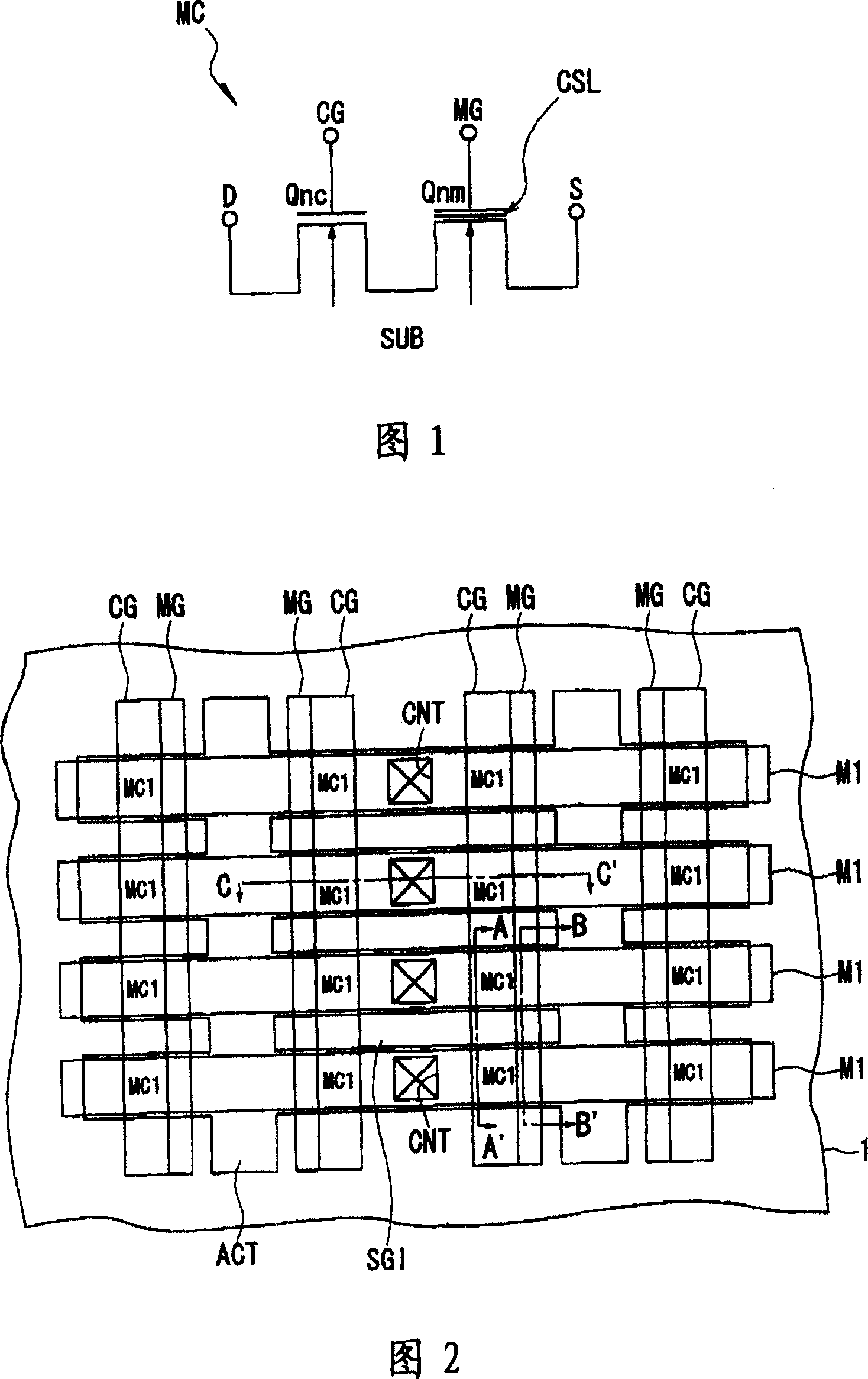

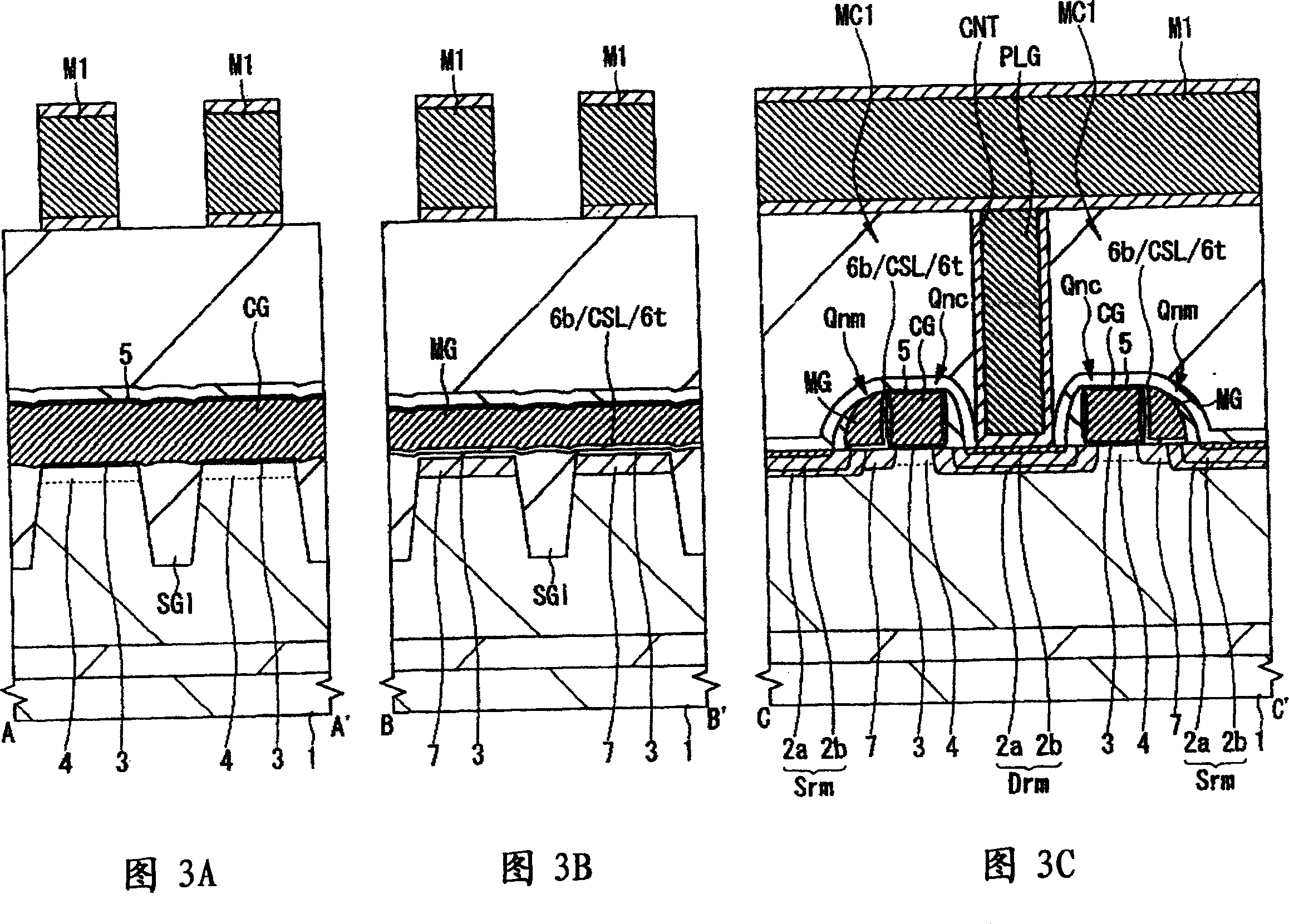

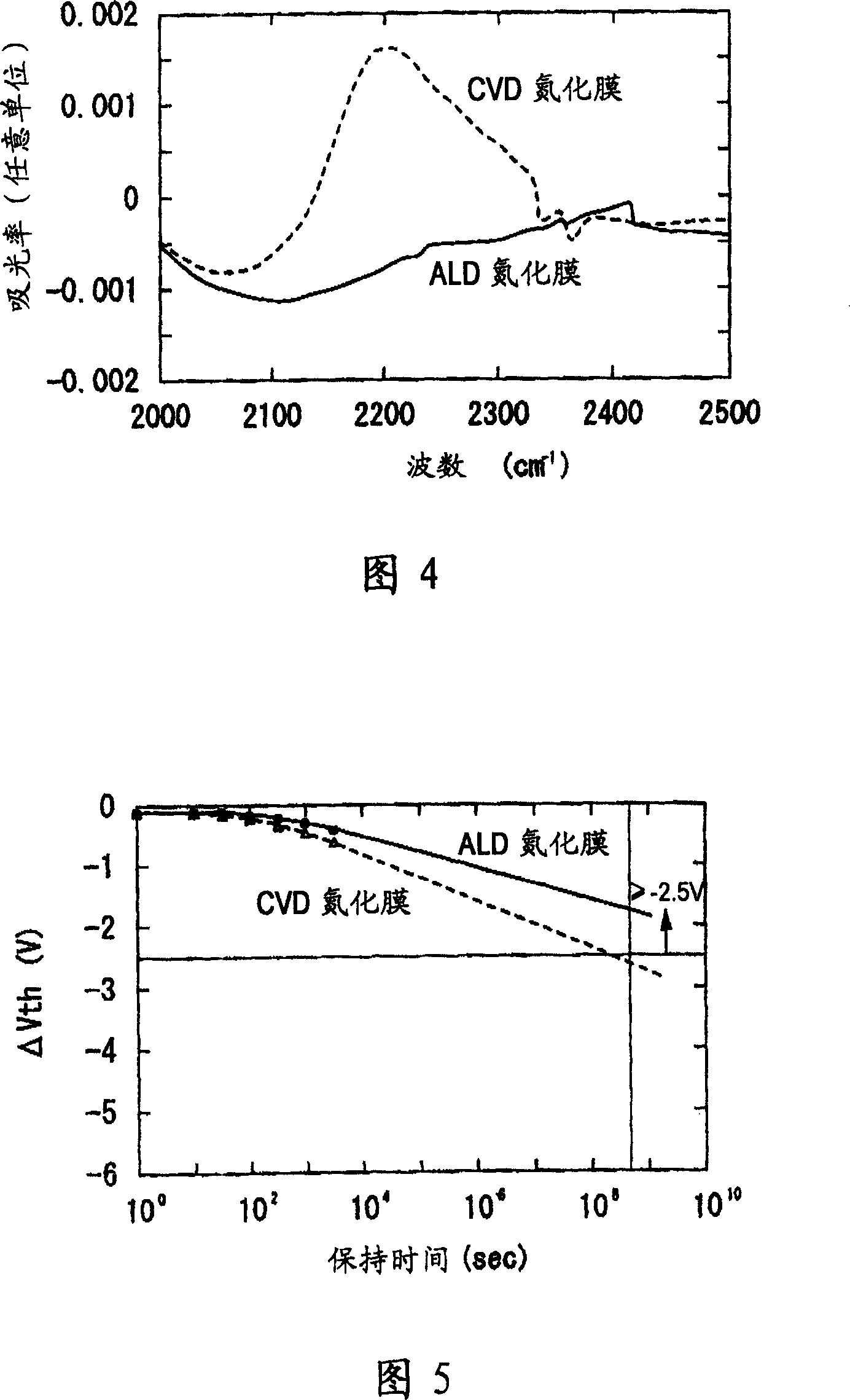

[0060] FIG. 1 shows a circuit diagram of a MONOS type memory cell.

[0061] The memory cell MC has, between the drain electrode D and the source electrode S, an nMISFET (first field effect transistor, hereinafter simply referred to as nMIS for selection) Qnc for memory cell selection, and an nMISFET (second field effect transistor for selection) Qnc for memory cells, for example. Field-effect transistors, hereinafter referred to only as nMIS for memory) Qnm 2 transistors. The nMISQnc for selection has a control gate electrode CG, and the nMISQnm for memory has a memory gate electrode MG and a charge storage layer CSL.

[0062] When performing a data readout operation, for example, about 1.0V is applied to the drain electrode D of the selected memory cell, about 1.5V is applied to the control gate electrode CG, and about 1.5V is applied to the source electrode S of the selected memory cell MC. For example, 0 (zero) V is applied to the memory gate electrode MG and the substrate...

Embodiment approach 2

[0094] In Embodiment 2, an example in which the present invention is applied to a memory cell of the memory gate electrode-on-type will be described. FIG. 16 shows an example of a basic device cross-section of a memory cell in which a channel is cut along a direction intersecting the memory gate electrode MG (direction C-C' in FIG. 2 ). In Embodiment 1, two memory cells in the C-C' direction are shown, but in this embodiment, only one memory cell is shown for simplification of description.

[0095] The memory cell MC2 with the memory gate electrode on top has a planar structure substantially the same as that of the memory cell MC1 in Embodiment 1, but has a cross-sectional structure in which a part of the memory gate electrode MG is placed between the control gate electrode CG. On one side, insulation of the control gate electrode CG and the memory gate electrode MG is formed by the insulating film 18 made of silicon oxide or the like, the insulating films 6b, 6t, and the char...

Embodiment approach 3

[0103] In Embodiment 3, an example in which the present invention is applied to a control gate electrode-on-type memory cell will be described. FIG. 21 shows a cross-sectional view of the main part of the memory cell, and FIG. 22 shows the basic device of the memory cell in which the channel is cut along the direction (DD' line of FIG. 21 ) crossing the memory gate electrode. An example of a section.

[0104] In active region ACT on the main plane of substrate 1, nMISQnc for selection and nMISQnm for memory of memory cell MC3 are arranged. On the main plane of the substrate 1 between the drain region Drm and the source region Srm of the memory cell MC3, the control gate electrode CG of the selection nMISQnc and the memory gate electrode MG of the memory nMISQnm extend adjacently, and the control A part of the gate electrode CG is located on the side of the memory gate electrode MG. In addition, similarly to the memory cell MC1 in Embodiment 1 described above, in the extendin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More