Method for finishing hard mask layer, method for forming transistor grids, and stack structure

A technology of hard mask layer and stacked structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve the problem of poor gate structure, distorted pattern of hard mask layer 108, damage to process flow and results, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

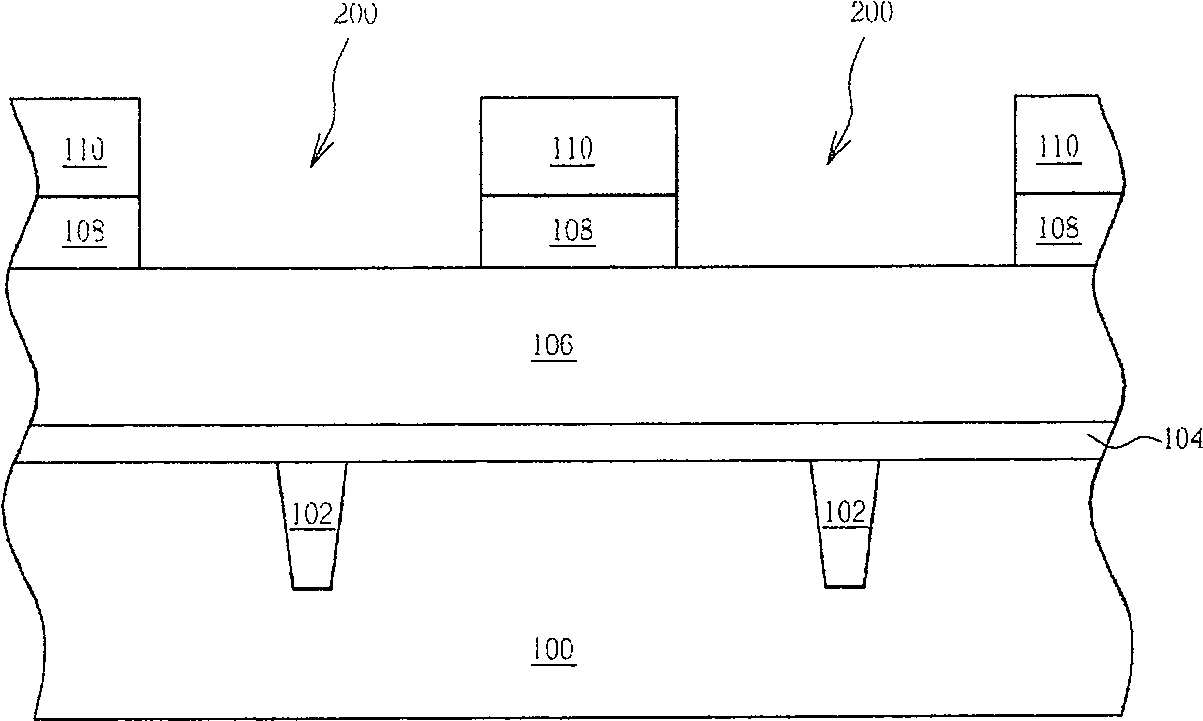

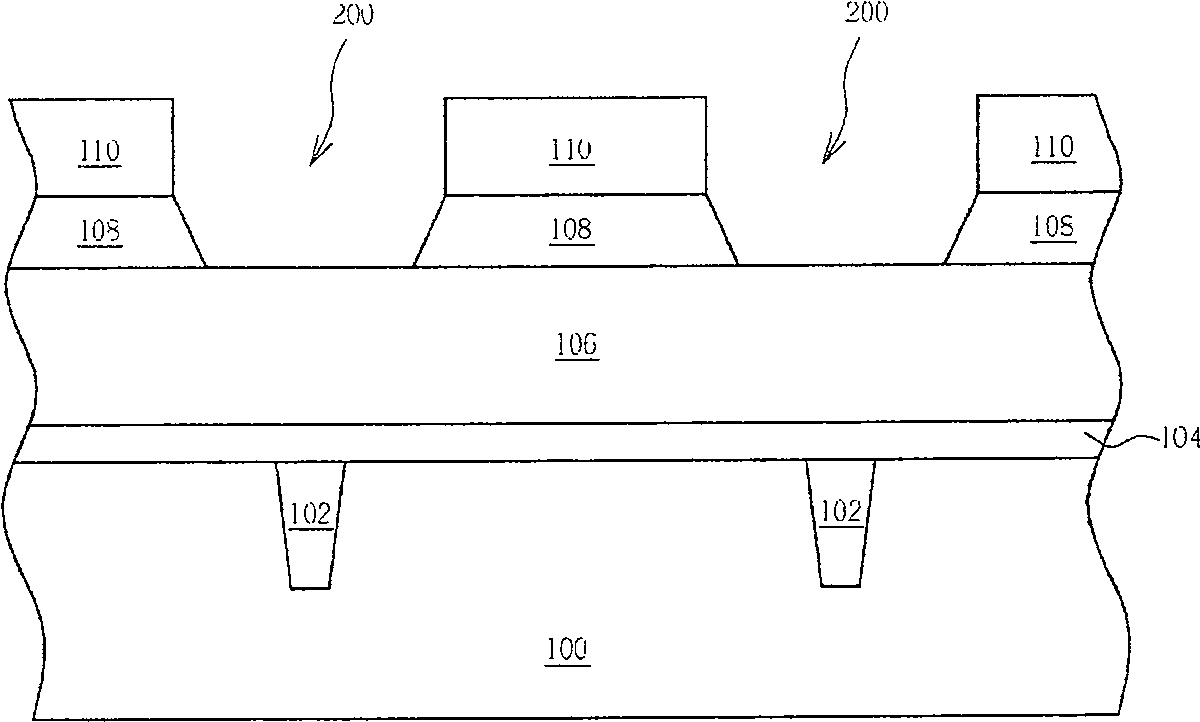

[0038] Please refer to Figure 4 to Figure 10 . Figure 4 to Figure 10 It is a schematic diagram of the process of forming the gate of the metal oxide semiconductor transistor according to the present invention. Please refer to Figure 4 , providing a substrate 400, generally made of single crystal silicon, or silicon on insulation (SOI), or other semiconductor materials that can be used in this technology, such as: strained silicon (strained silicon), strained insulating layer Strained silicon-on-insulator, silicon-germanium, strained silicon-germanium, silicon-germanium on insulator, germanium, strained germanium ( strained germanium), germanium oninsulator (GeOI), strained germanium on insulator, strained semiconductor, compound semiconductor, compound semiconductor and Multilayer semiconductor (multi-layerssemiconductor) instead.

[0039] Substrate 400 includes several silicon dioxide (SiO 2 ) or a low-k dielectric material such as a shallow trench isolation (shallow ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More