Stacked wafer for 3-D integration

A technology of stacking wafers and wafers, which is applied in the manufacture of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., and can solve problems such as complex connections

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

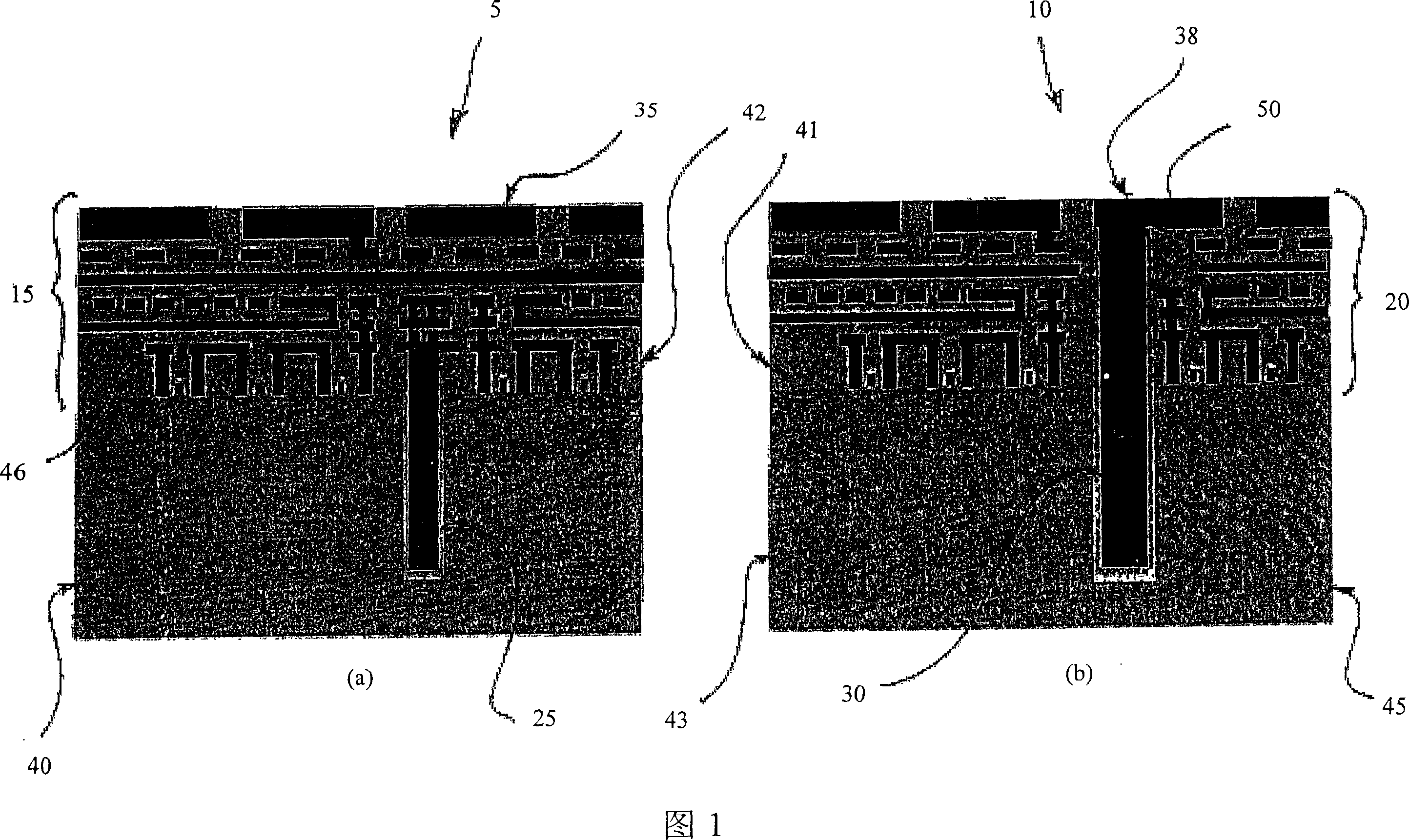

[0048] Figures 1a and 1b show two embodiments of the invention both comprising IC layered CMOS process wafers. IC layers 15 , 20 have been formed in dielectric layers 41 , 42 and together on silicon substrates 40 , 45 . The outer surface of the wafer 5, 10 has copper pads 35, 38 embedded in the surface of the dielectric.

[0049] The main point of difference between the embodiments of FIGS. 1 a and 1 b is the arrangement of the vertical connectors 25 , 30 . In the case of FIG. 1a, the vertical connectors have been embedded in the wafer 5 before the formation of the first IC layer 46 (Metal-1). Figure 1 b has the vertical connector 30 embedded in the wafer 10 after the integrated circuit layer 20 is placed, but before the copper pads 38 are placed. In fact, the present invention is not dependent on any particular location or stage of formation of the vertical connectors 25, 30, which may be placed before any IC metal layers (eg, Metal-1 through Metal-6 of FIG. 1).

[0050] T...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More