Silicon chip shallow plow groove isolation etching method

A technology of shallow trenches and silicon wafers, applied in the manufacture of electrical components, semiconductor/solid-state devices, circuits, etc., can solve the problems of high price of CH2F2 gas, complicated tail gas treatment process, and increased consumption cost, and achieve low cost and step-by-step Less, smooth transition effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

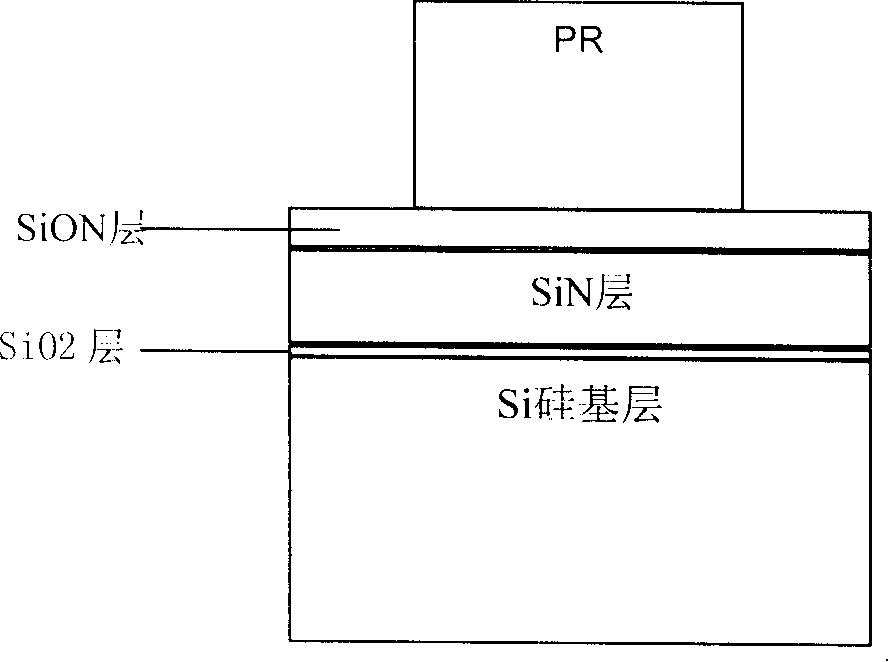

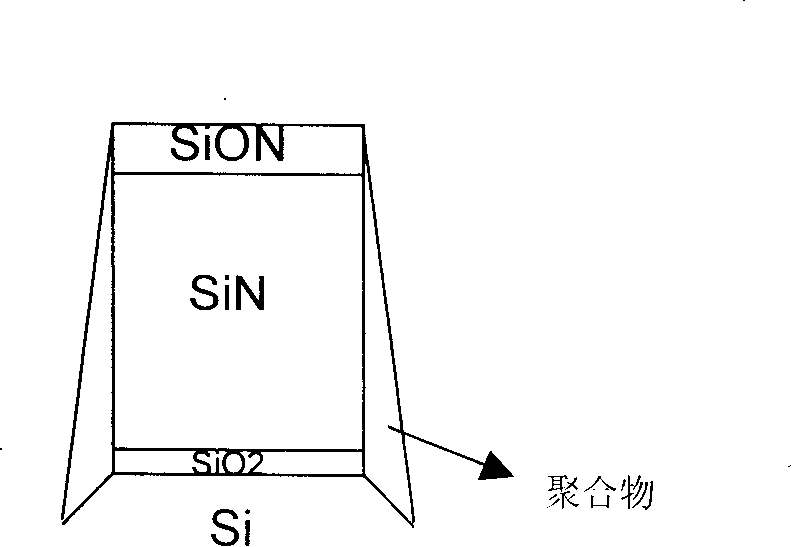

[0035] The method for silicon wafer shallow trench isolation etching of the present invention is mainly used for etching trenches on silicon wafers, such as figure 1 As shown, the silicon wafer is a multi-layer structure, including a silicon upper layer and a silicon base layer, and an oxide layer is arranged between the silicon upper layer and the silicon base layer. The silicon upper layer here mainly includes a SiON (hard mask) layer and a SiN layer. There is an SiO2 oxide layer between the silicon upper layer and the silicon base layer. In the process of performing shallow trench isolation etching on the semiconductor silicon wafer, it is necessary to form a smooth upper part at the junction of the SiO2 layer and the silicon base layer on the side wall of the trench. The rounded corners are conducive to the release of stress and avoid the generation of parasitic conductive channels in the semiconductor silicon wafer.

[0036] The method for silicon wafer shallow trench iso...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More