Wafer-grade chip packaging process and chip packaging structure

A chip packaging structure, wafer-level chip technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems affecting the path of external incident light signals, optical signal distortion, residual air bubbles, etc. To achieve the effect of protecting the photosensitive area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

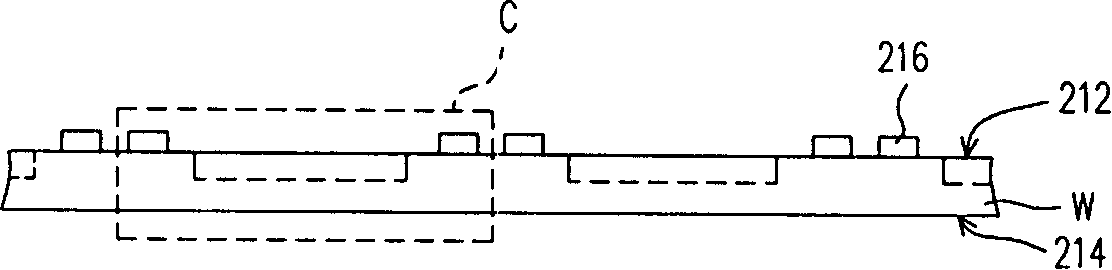

[0022] Figure 2A to Figure 2F A schematic side view of a wafer-level chip packaging process according to an embodiment of the present invention is shown. The wafer-level chip packaging process of this embodiment includes the following steps. First, please refer to Figure 2A , providing a wafer W. The wafer W includes a plurality of chip units C, and the wafer W has an active surface 212 and an opposite back surface 214 . Each chip unit C has a plurality of pads 216 on the active surface 212, and the material of the pads 216 includes aluminum.

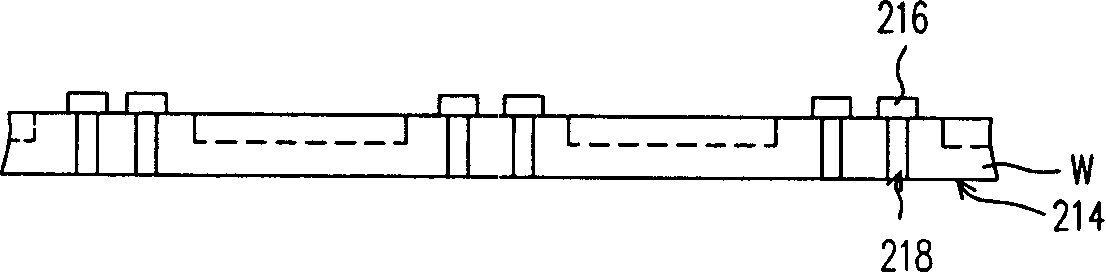

[0023] Next, please refer to Figure 2B , forming a plurality of through holes 218 under the pads 216 . In this embodiment, the method of forming the through holes 218 includes etching, for example, using a laser to etch from the backside 214 of the wafer W to the pads 216 .

[0024] Next, please refer to Figure 2C The conductive material M is filled in these through holes 218, and the conductive material M in each through hol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More