Semiconductor integrated circuit interlinkage structure interstitial copper-plating method and structure

A technology of interconnection structure and integrated circuit, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as poor gap filling characteristics and gaps, and achieve the effect of improving device yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] According to the present invention, techniques for fabricating integrated circuits are provided. More specifically, the present invention provides methods and devices for fabricating metal interconnect structures with improved interstitial properties. By way of example only, the invention has been applied to copper metal structures, such as dual damascene structures for advanced signal processing devices. It should be recognized, however, that the invention has broader applicability. For example, the invention may be applied to microprocessor devices, memory devices, application specific integrated circuit devices, and various other interconnect structures.

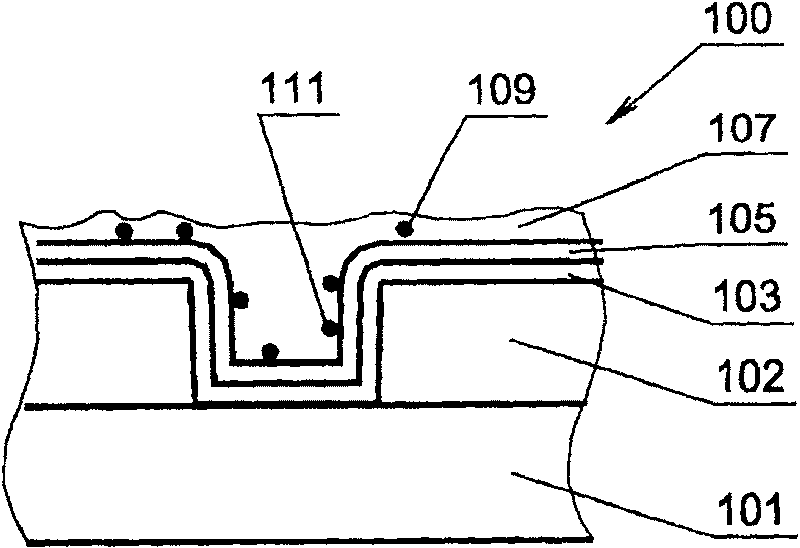

[0015] figure 1 is a simplified cross-sectional view of the interconnect structure of a conventional copper interconnect. As shown, device 100 includes a substrate 101, which is a silicon substrate. Above the substrate is an interlayer dielectric layer 102 . A contact structure is formed inside the dielectric ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More