Manufacturing method of grid dielectric layer and grid

A gate dielectric layer and manufacturing method technology, which is applied in the field of semiconductor manufacturing, can solve the problems of semiconductor device stability and electrical performance degradation, dense silicon oxide layer insulation capacity degradation, uniformity deterioration, etc., to achieve stable and consistent electrical characteristics , high carrier mobility and turn-on sensitivity, good uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

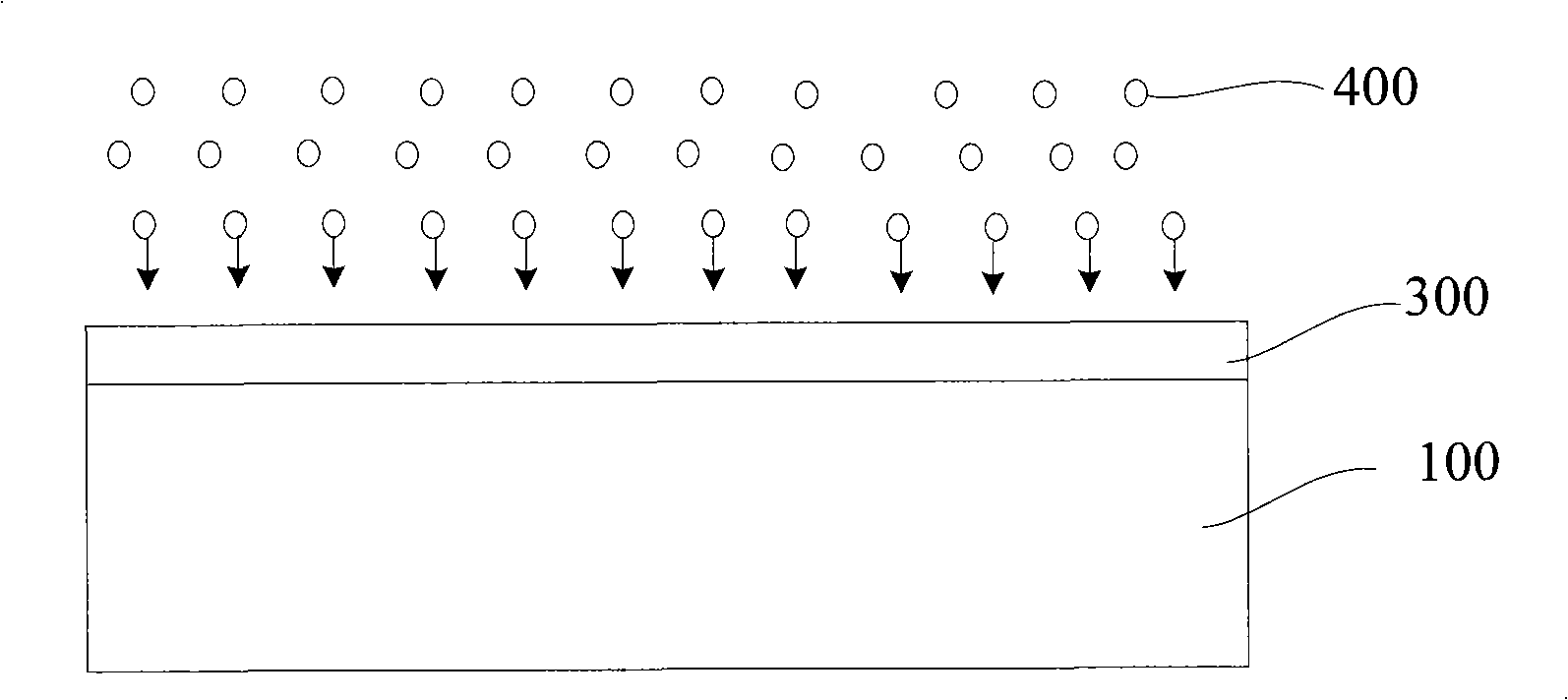

[0039] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0040] With the development of semiconductor manufacturing technology, the size of the gate is getting smaller and smaller, and the operating voltage acting on the gate also needs to be reduced accordingly. In order to ensure the fast response characteristics of the formed semiconductor device, the thickness of the corresponding gate dielectric layer Thinning is also required as gate dimensions continue to decrease. Generally speaking, the ratio of the size of the gate to the gate dielectric layer corresponding to the gate is about 45 to 50, which means that when the gate size is reduced to 65nm or even smaller, the gate dielectric layer corresponding to the gate The thickness of the layer should be less than 1.5 nm. This is a big challenge to the existing process for forming the gate dielectric layer. The invention provides a method for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More