Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as difficulty in suppressing short-channel effects of devices, lack of impurities, and degradation of input/output device life, so as to reduce heat load Jet injection effect, optimized performance, and the effect of not degrading short channel characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

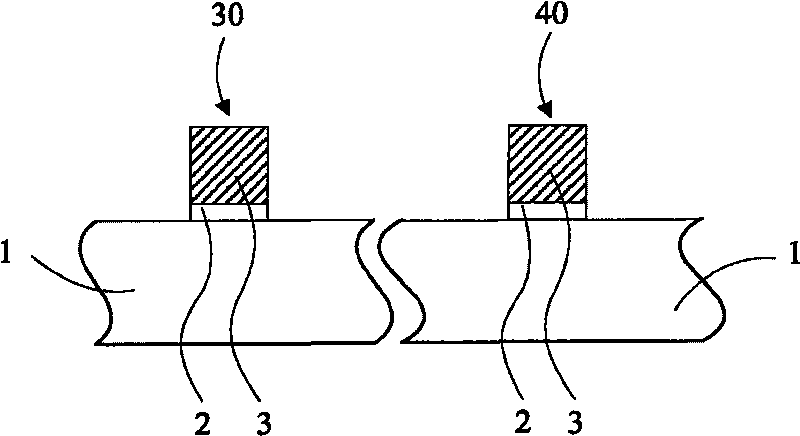

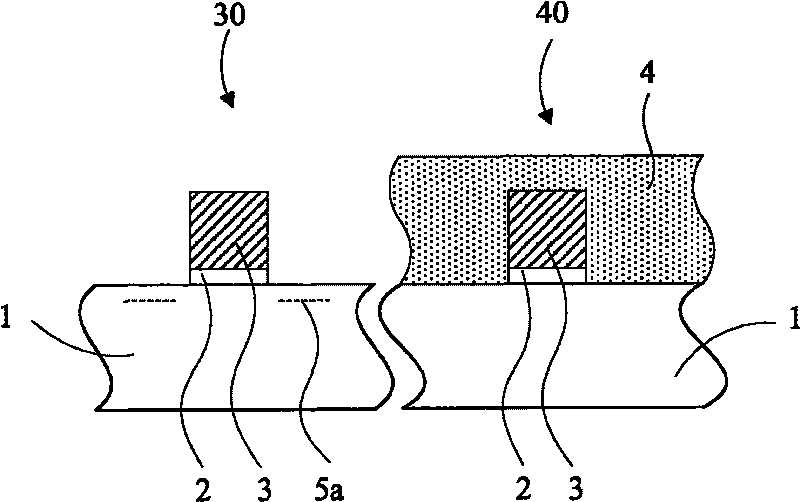

[0048] This embodiment provides a method for manufacturing a semiconductor device, refer to the attachment Figure 14 As shown in the process flow chart, it includes the following steps: step S200, a semiconductor substrate is provided, the semiconductor substrate includes a core device area and an input / output device area, the core device area and the input / output device area are both formed on the semiconductor substrate The gate dielectric layer and the gate located on the gate dielectric layer; step S210, using the gate as a mask, perform the first ion implantation in the semiconductor substrate in the core device area; step S220, perform sharp annealing, Low-doped source and drain regions are formed in the semiconductor substrate on both sides of the gate dielectric layer in the core device region; step S230, using the gate as a mask, perform a second ion implantation into the semiconductor substrate in the input / output device region Step S240, perform rapid thermal anneali...

Embodiment 2

[0093] This embodiment provides a method for manufacturing a semiconductor device, including the following steps:

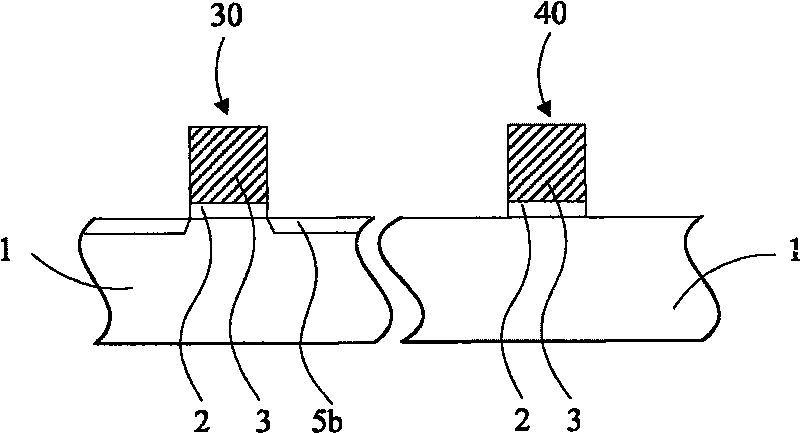

[0094] In step S300, a semiconductor substrate is provided. The semiconductor substrate includes a core device area and an input / output device area. A gate dielectric layer and a gate dielectric layer are formed on the semiconductor substrate in the core device area and the input / output device area. The gate on the layer has a first spacer formed on the gate dielectric layer of the core device area and the sidewall of the gate;

[0095] Step S310, using the first spacer as a mask, perform the first ion implantation into the semiconductor substrate in the core device area;

[0096] Step S320, performing sharp annealing to form low-doped source and drain regions in the semiconductor substrate on both sides of the first spacer in the core device region;

[0097] Step S330, using the gate as a mask, perform a second ion implantation into the semiconductor substrate in the in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More