Method for eliminating probe needle track bias

A technology of probes and stitches, which is applied in the field of eliminating the offset of probes and stitches in wafer acceptance testing, can solve the problems of electrical parameter measurement results errors, scrapping of 25 wafers, and offsets, etc., to improve The effects of measuring accuracy, eliminating stitch deviation, and avoiding scratches

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described below in conjunction with specific embodiments and accompanying drawings.

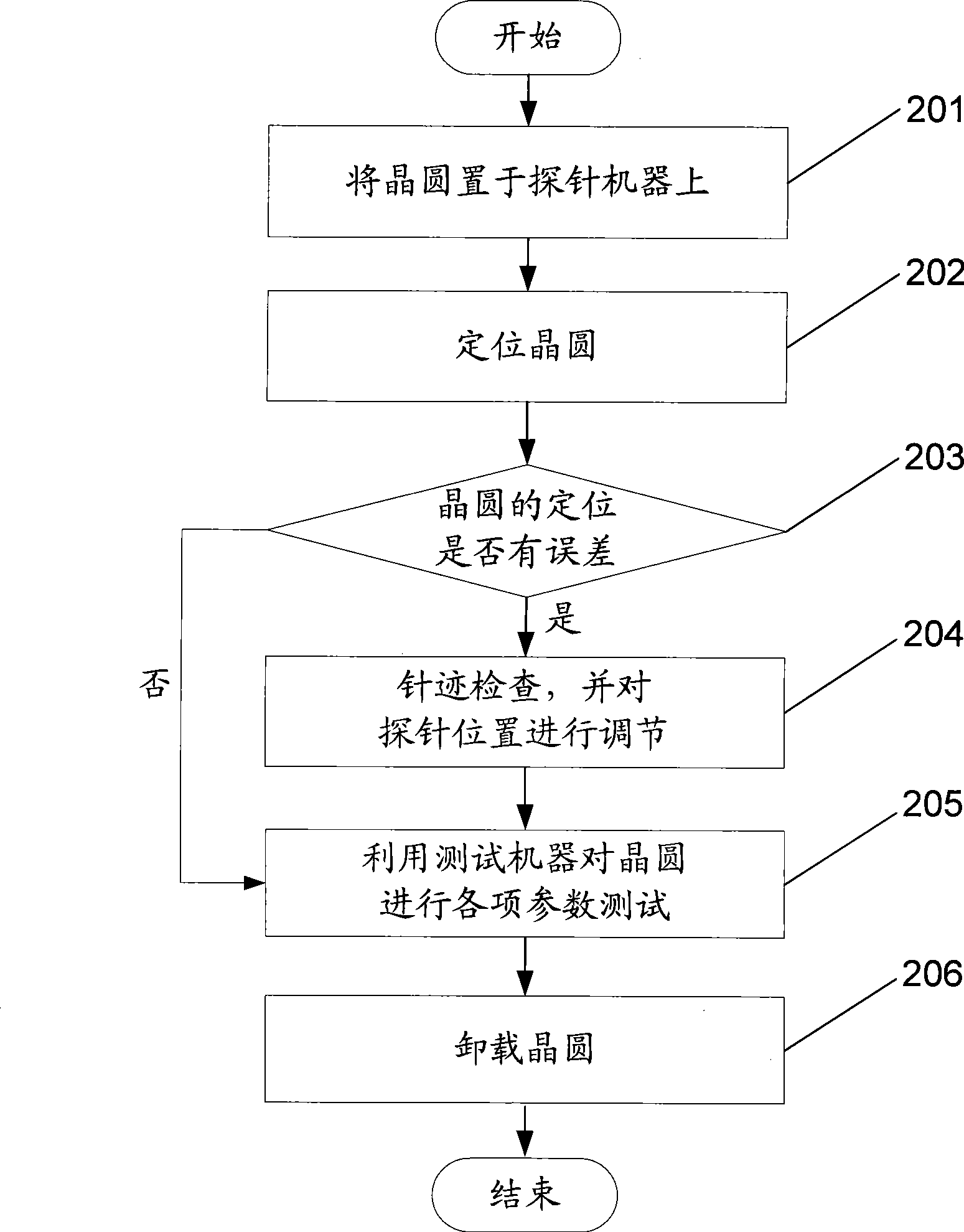

[0036] figure 2 It is the WAT flowchart of the present invention. The test steps for each wafer are as follows:

[0037] 201) placing the wafer on the probe machine (Prober);

[0038] 202) Alignment wafer;

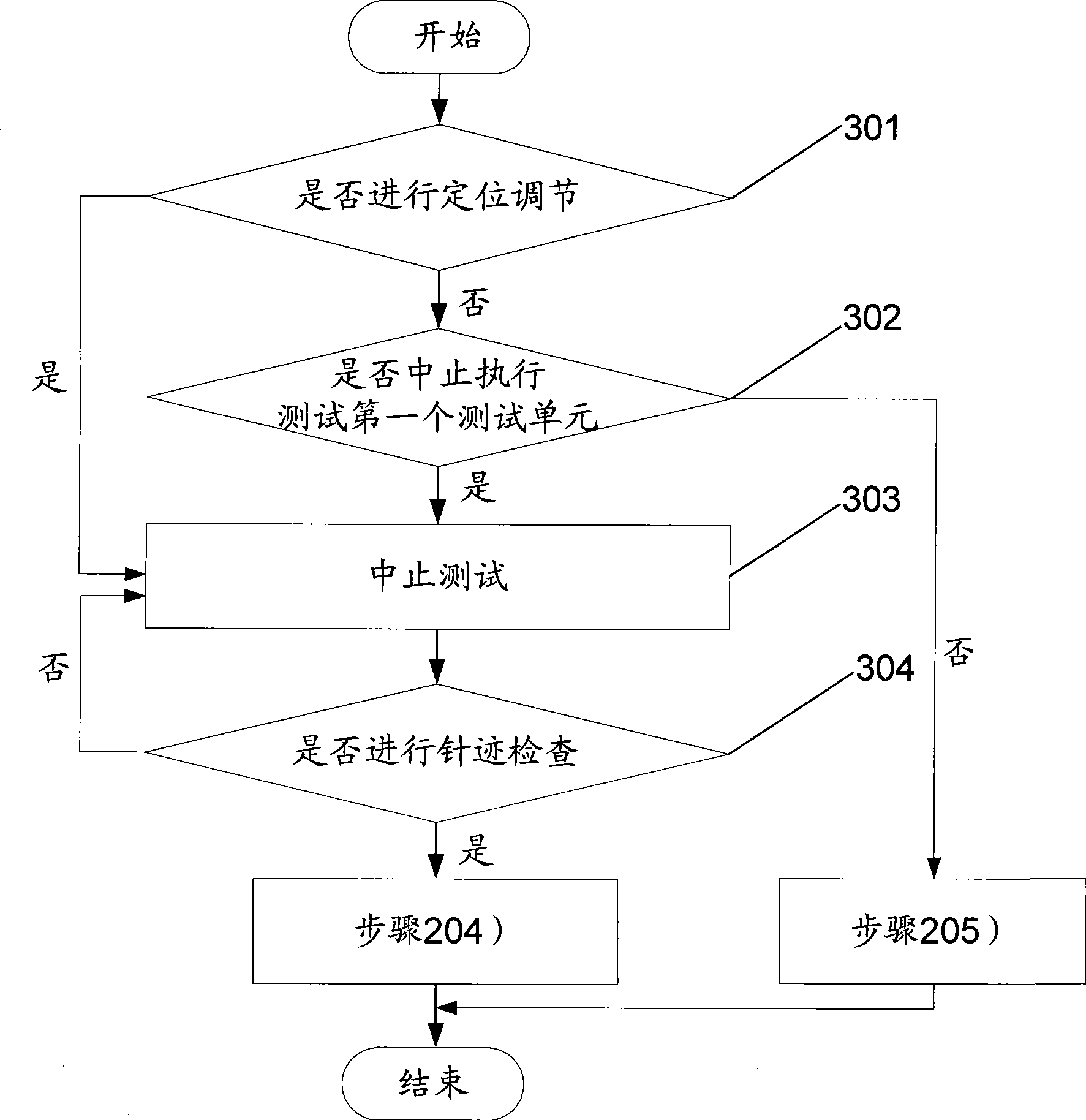

[0039] 203) Determine whether there is an error in the positioning of the wafer, if there is an error, perform step 204); if there is no error, perform step 205);

[0040] 204) Stitch checking, and adjusting the position of the probe;

[0041] 205) using a tester (Tester) to perform various parameter tests on the wafer;

[0042] 206) Unloading the wafer.

[0043] The method of the present invention monitors the wafer positioning through the microscope (Camera) of the probe machine, and if the wafer positioning is correct, then perform step 205), that is, the testing steps for each wafer are consistent with the steps of the prior art, If...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More