Charge trapping memory cell with high speed erase

A charge capture and storage unit technology, applied in electrical components, circuits, electrical solid devices, etc., can solve problems such as limiting device operating variables, and achieve the effect of excellent data retention capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0075] Propose below according to preferred embodiment of the present invention, and supplement with Fig. 1 to Figure 15 as a detailed description of the invention.

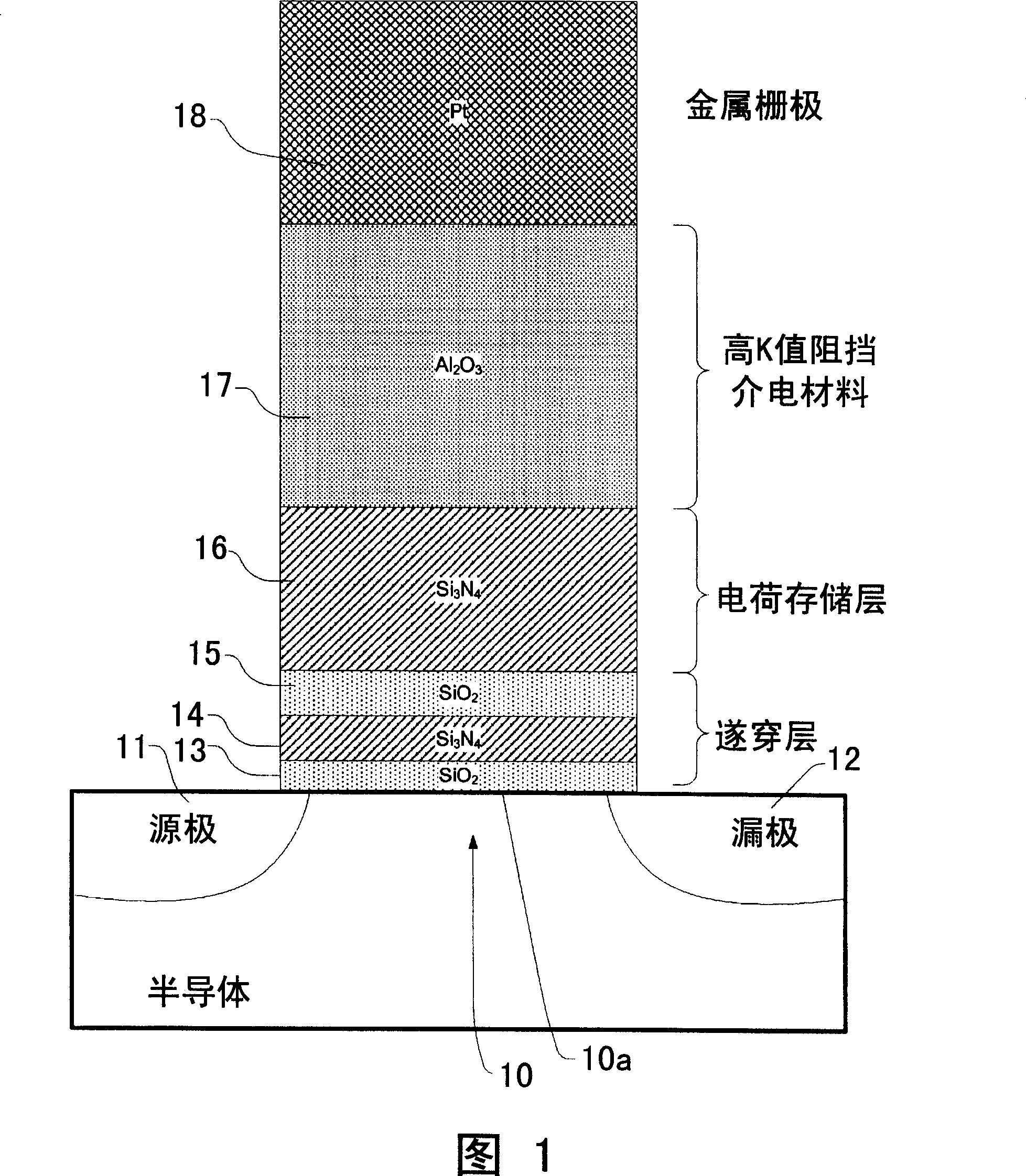

[0076] FIG. 1 is a schematic diagram of a charge trapping memory cell using a high-k blocking dielectric layer and a bandgap-engineered tunneling dielectric layer. The memory cell includes a channel 10 , a source 11 and a drain 12 in a semiconductor substrate. The source 11 and the drain 12 are adjacent to the channel 10 .

[0077] In this embodiment, the gate 18 includes platinum with a work function of about 8 electron volts (eV). In a preferred embodiment, the gate 18 is made of metal or metal compound, such as platinum, tantalum nitride, aluminum or other metal or metal compound gate material, preferably a material with a work function higher than 4.5 eV. A variety of high work function materials that may be suitable for use here as gate terminals are described in the above-mentioned US Patent No. 6,912,1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More