Time clock generating circuit and design method

A technology of clock generation circuit and design method, applied to electrical components, single output arrangement, devices that give pulses at different times, etc., can solve the problems of increasing chip manufacturing cost, large chip area, increasing circuit power consumption, etc., to achieve The effect of improving performance, reducing production cost, and reducing chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

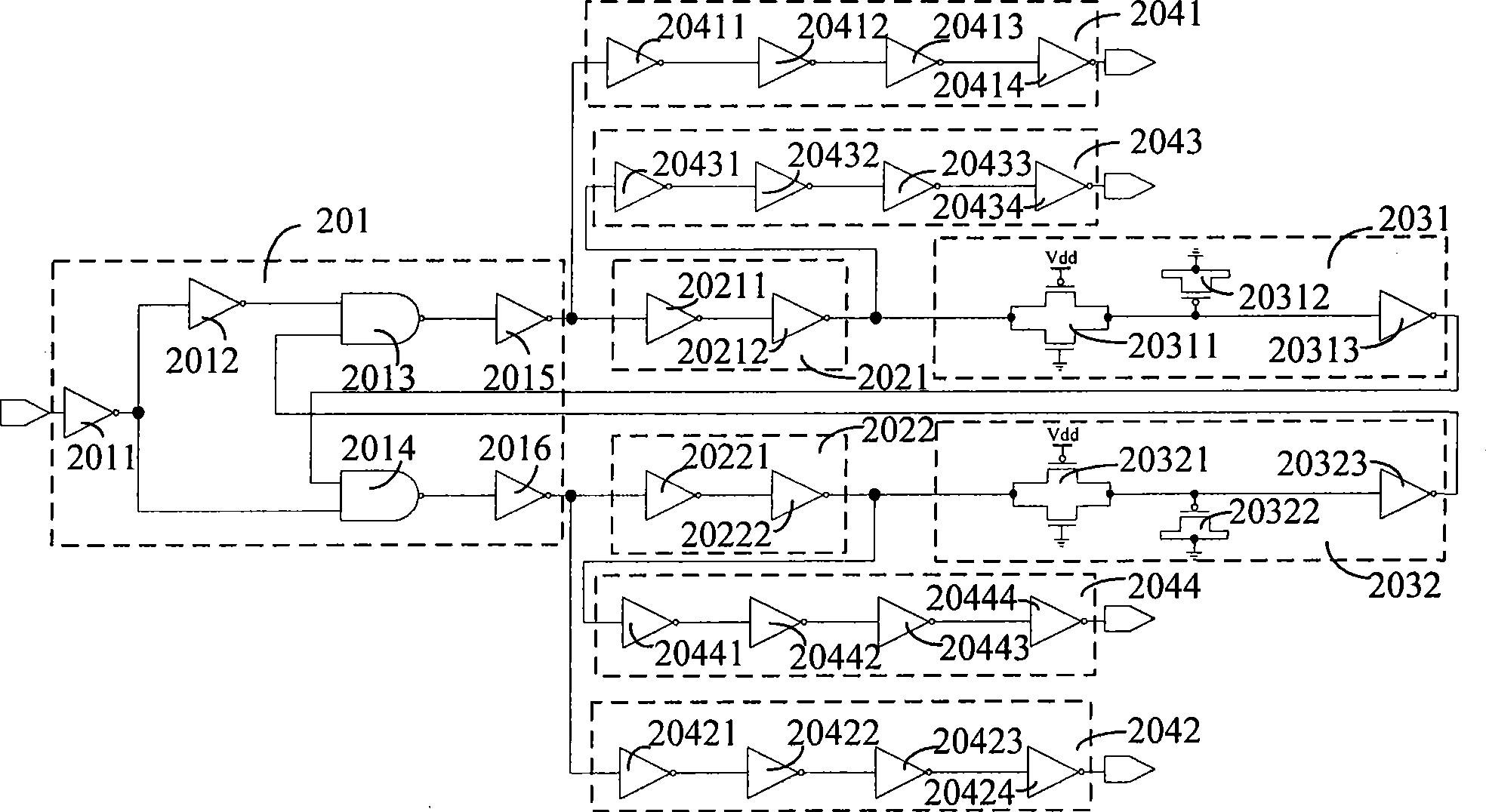

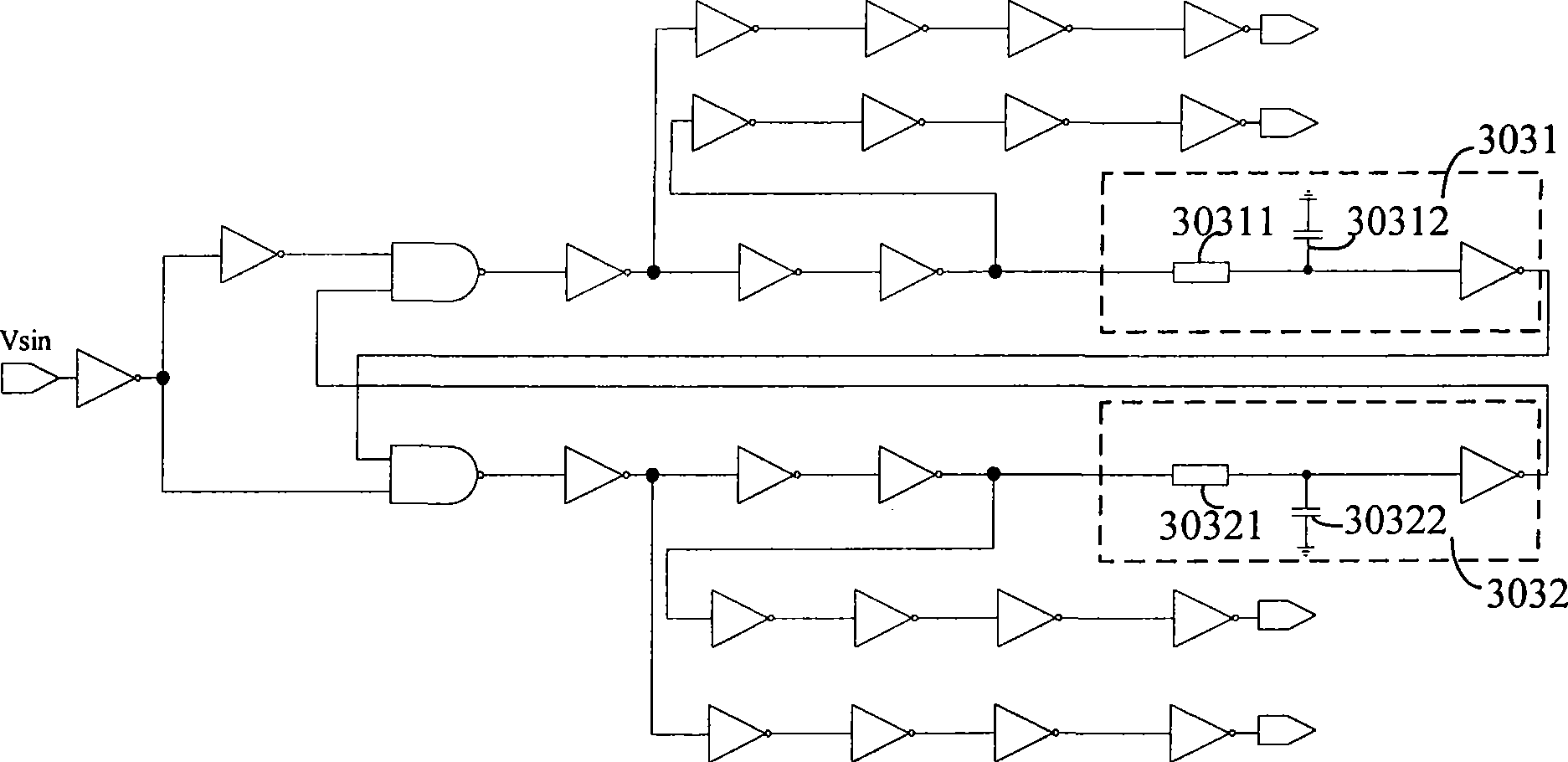

[0037] The present invention is based on the existing clock generating circuit, through a transmission gate composed of a CMOS transistor connected in series and a PMOS transistor instead of a plurality of large-sized CMOS transistor inverters in the delay module of the clock circuit to form a low-pass RC The circuit realizes the delay function in the process of generating the clock signal.

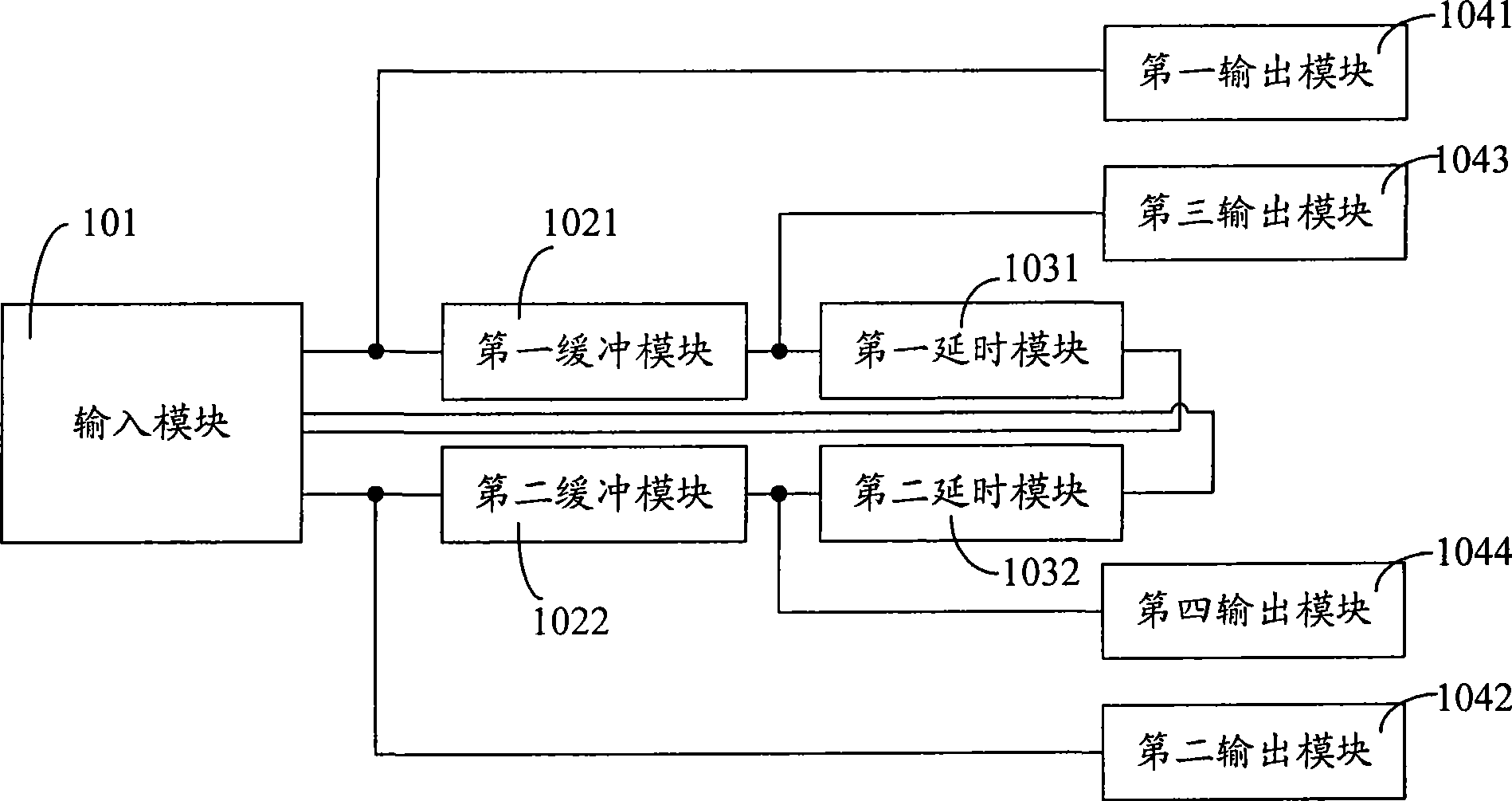

[0038] figure 1 It is a structural block diagram of a clock generation circuit in a specific embodiment of the present invention, the clock generation circuit includes an input module 101, a first buffer module 1021, a second buffer module 1022, a first delay module 1031, a second delay module 1032 and a first An output module 1041 , a second output module 1042 , a third output module 1043 , and a fourth output module 1044 . in,

[0039] An input module 101, configured to generate a first clock signal and a second clock signal;

[0040] The first buffer module 1021 is configured to gen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More