Software and hardware cooperating design method for arithmetic acceleration

A technology of software-hardware collaboration and design methods, applied in computing, special data processing applications, instruments, etc., can solve problems such as insufficient optimization of the system, inability to achieve hardware scale and performance, loss of high-level comprehensive fineness, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

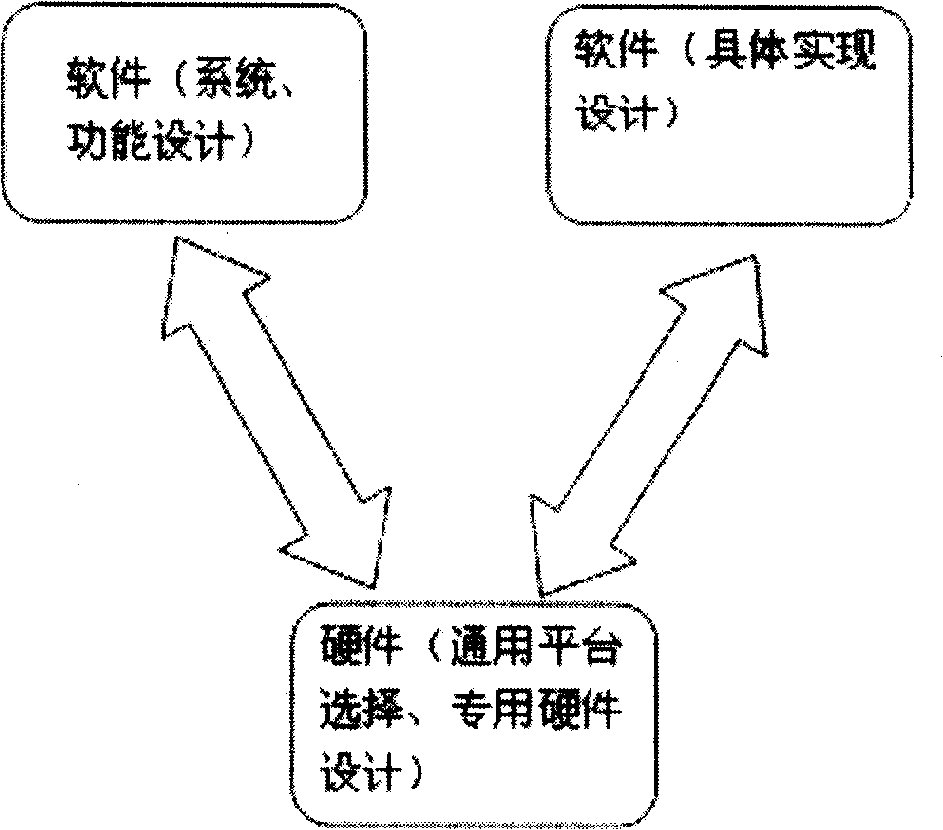

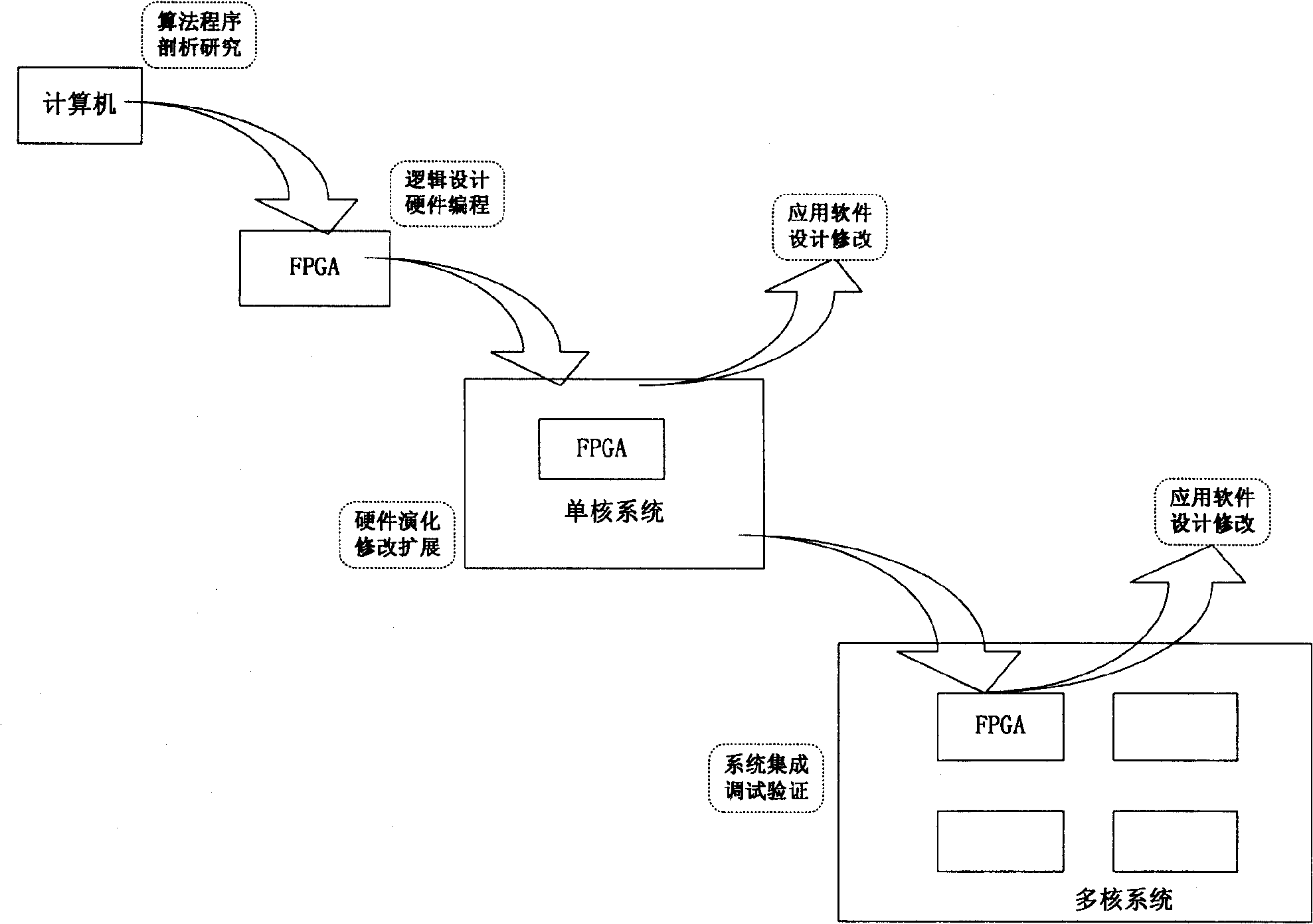

[0047] See figure 1 , figure 2 , image 3 , Figure 4 , Figure 5 , Image 6 As shown, an algorithm-accelerated software-hardware collaborative design method of the present invention, the specific implementation steps of the method are as follows:

[0048] Step 1: Algorithm and software static analysis. The mathematical principle of the algorithm can be verified by software such as Matlab, and then converted into an executable language such as C language to be realized on a PC or a special target hardware platform (such as an embedded device).

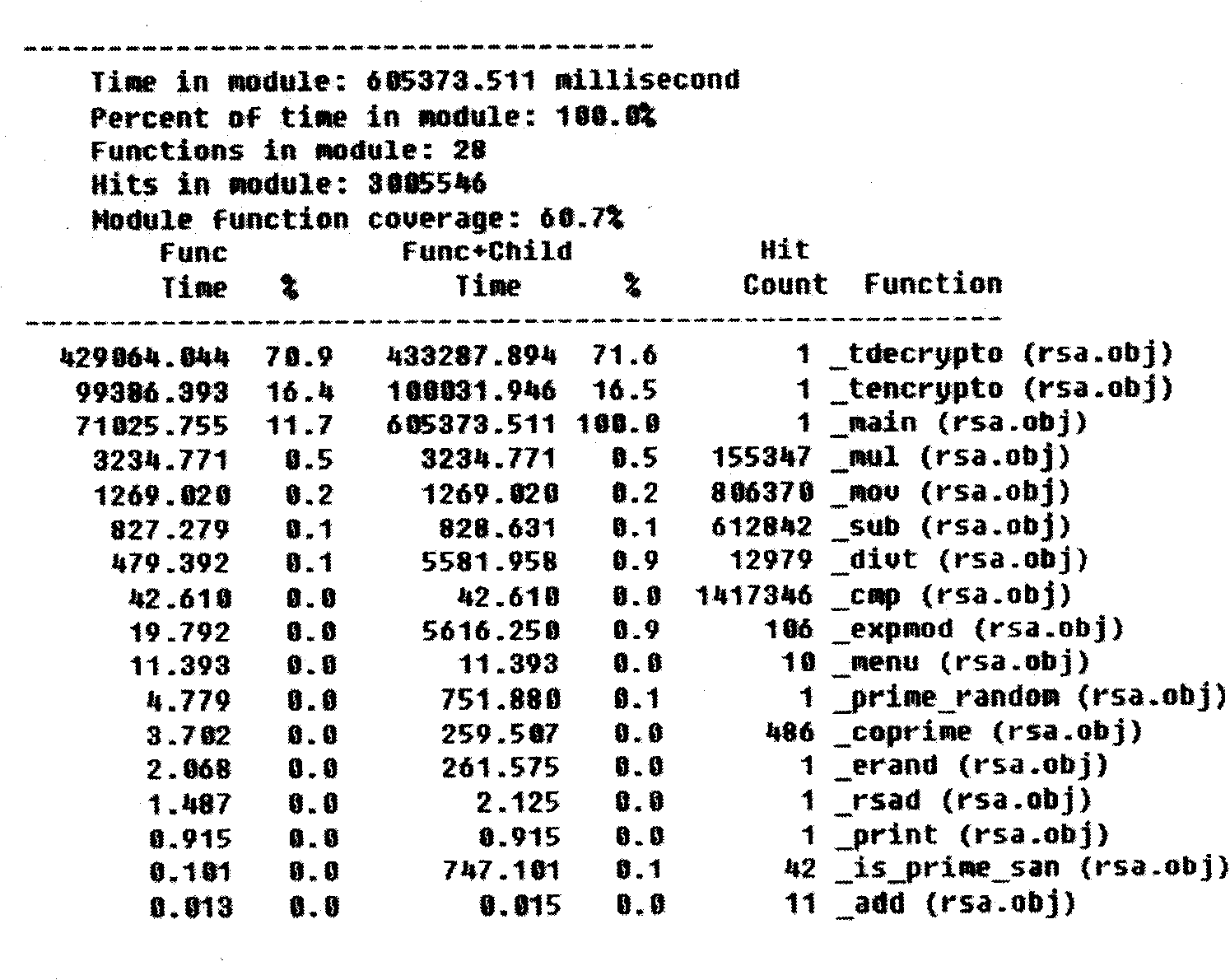

[0049] Step 2: Use software analysis tools to conduct dynamic measurement and analysis of software operation, and obtain basic data diagrams of software operation. The software tool that this step needs has the quantify in the IBM Rational suite that generates function call graph; Generate function running time and access times (as image 3 ) analysis (profile) software, such as VC profile under the Windows environment Visual C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More