Active element array substrate and manufacturing method therefor

A technology of array substrates and active components, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems affecting photosensitive characteristics, photocurrent attenuation, reduction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

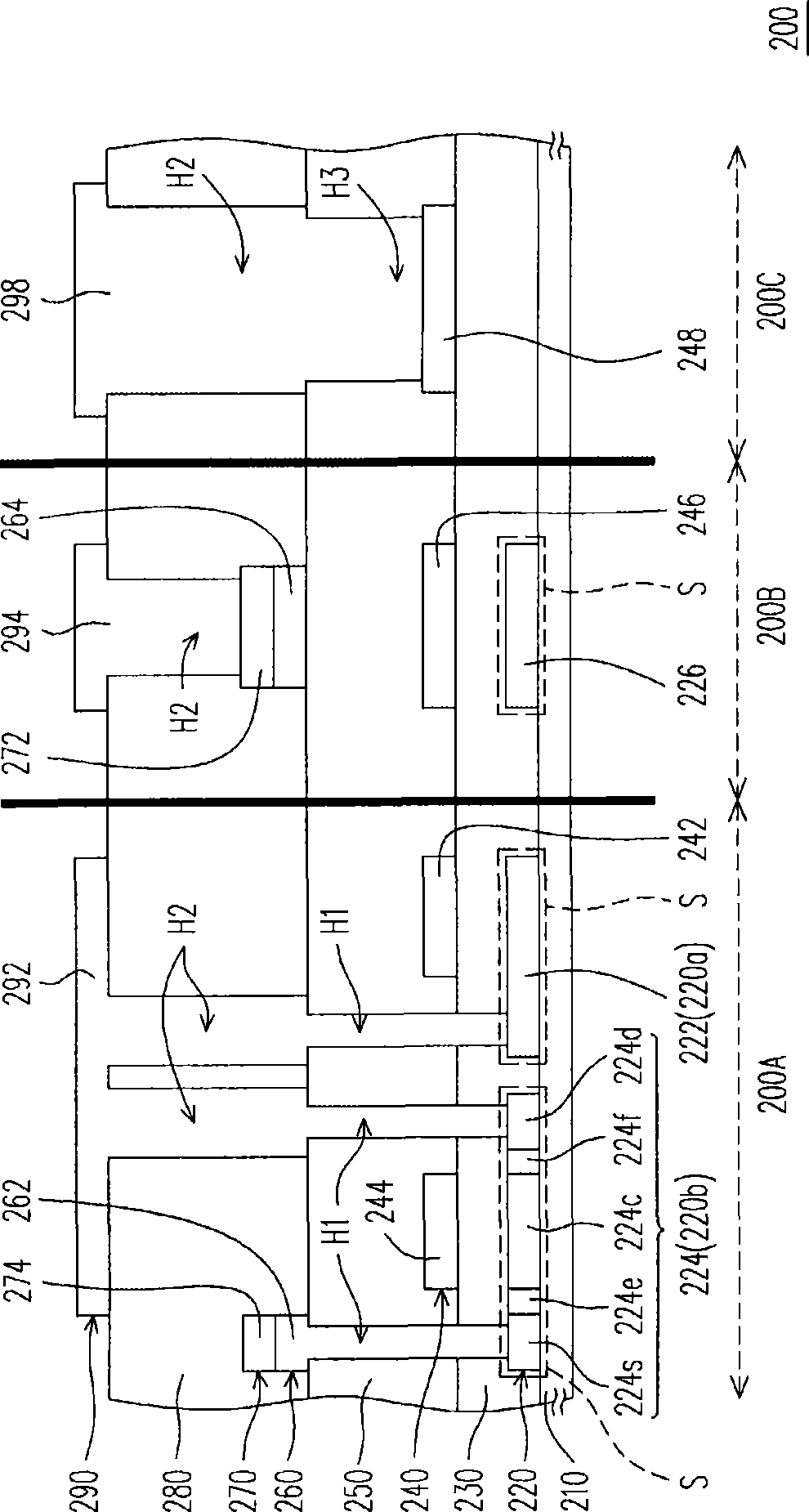

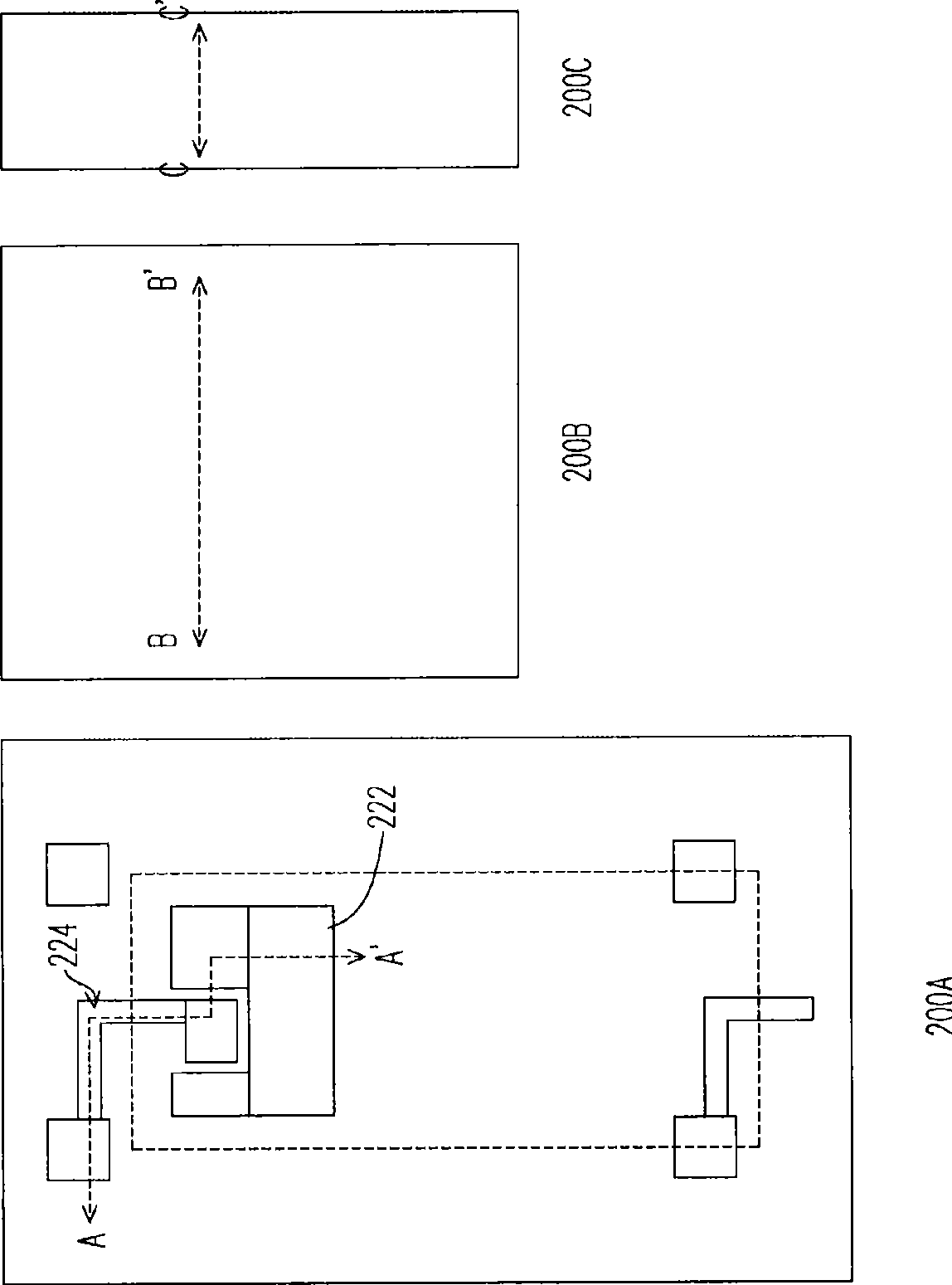

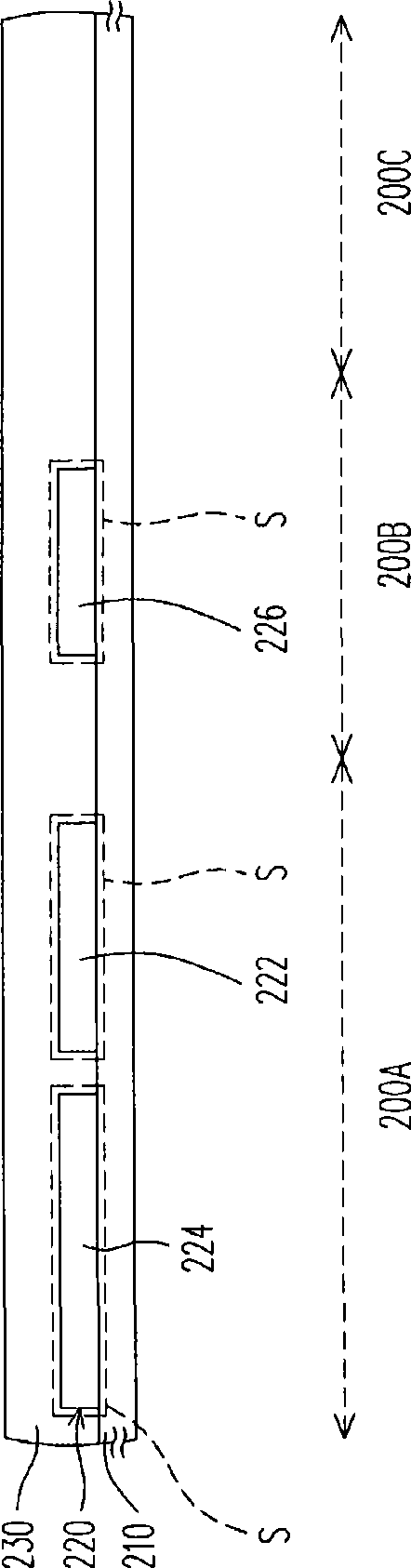

[0123] figure 1 It shows an active device array substrate according to the first embodiment of the present invention, in which, in order to make the diagram expression more concise, there may be a plurality of components in the figure 1 Only one may be shown to represent. Moreover, for the convenience of description, the active element array substrate can be divided into figure 1 The pixel area 200A, the sensing area 200B and the bonding pad area 200C in the. The pixel area 200A has an active element for controlling the display state, and in this embodiment, the active element in the pixel area 200A can be combined with a storage capacitor to provide a better display effect.

[0124] Please refer to figure 1 , the active element array substrate 200 includes a substrate 210, a first patterned semiconductor layer 220, a gate insulating layer 230, a first patterned conductor layer 240, a first dielectric layer 250, a second patterned conductor layer 260, a second patterned Th...

no. 2 example

[0146] image 3 An active device array substrate according to a second embodiment of the present invention is shown. Please refer to image 3 The active device array substrate 300 of this embodiment is similar to the active device array substrate 200 of the first embodiment, but compared with the first embodiment, in the active device array substrate 300 of this embodiment, the pixels located in the pixel area 200A The electrode 292 is indirectly electrically connected to the first patterned semiconductor layer 220 through the first patterned conductor layer 240 and the second patterned conductor layer 260 , for example.

[0147]In detail, compared with the first embodiment, the first patterned conductor layer 240 of the active device array substrate 300 further includes a bridge electrode 249 located in the pixel region 200A. At the same time, the contact conductor 262 of the active device array substrate 300 fills the first contact window H1 and is respectively in contact ...

no. 3 example

[0156] Figure 5 An active device array substrate according to a third embodiment of the present invention is shown. Please refer to Figure 5 The active device array substrate 400 of this embodiment is similar to the active device array substrates 200 and 300 of the foregoing embodiments, but compared with the foregoing embodiments 200 and 300, in the active device array substrate 400 of this embodiment, the pixel area 200A, the third patterned conductor layer 290 serving as the pixel electrode 292 is electrically connected to the first patterned semiconductor layer 220 through some of the second contact windows H2 and the second patterned conductor layer 260 . Moreover, the second patterned semiconductor layer 270 of this embodiment further includes a plurality of pseudo-semiconductor layers 274 located on the contact conductor 262, wherein the size of some of the pseudo-semiconductor layers 274 is, for example, substantially equal to the size of the contact conductor 262, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More