Thin-film transistor and display device

一种薄膜晶体管、非晶半导体的技术,应用在晶体管、电固体器件、半导体器件等方向,能够解决没确立等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

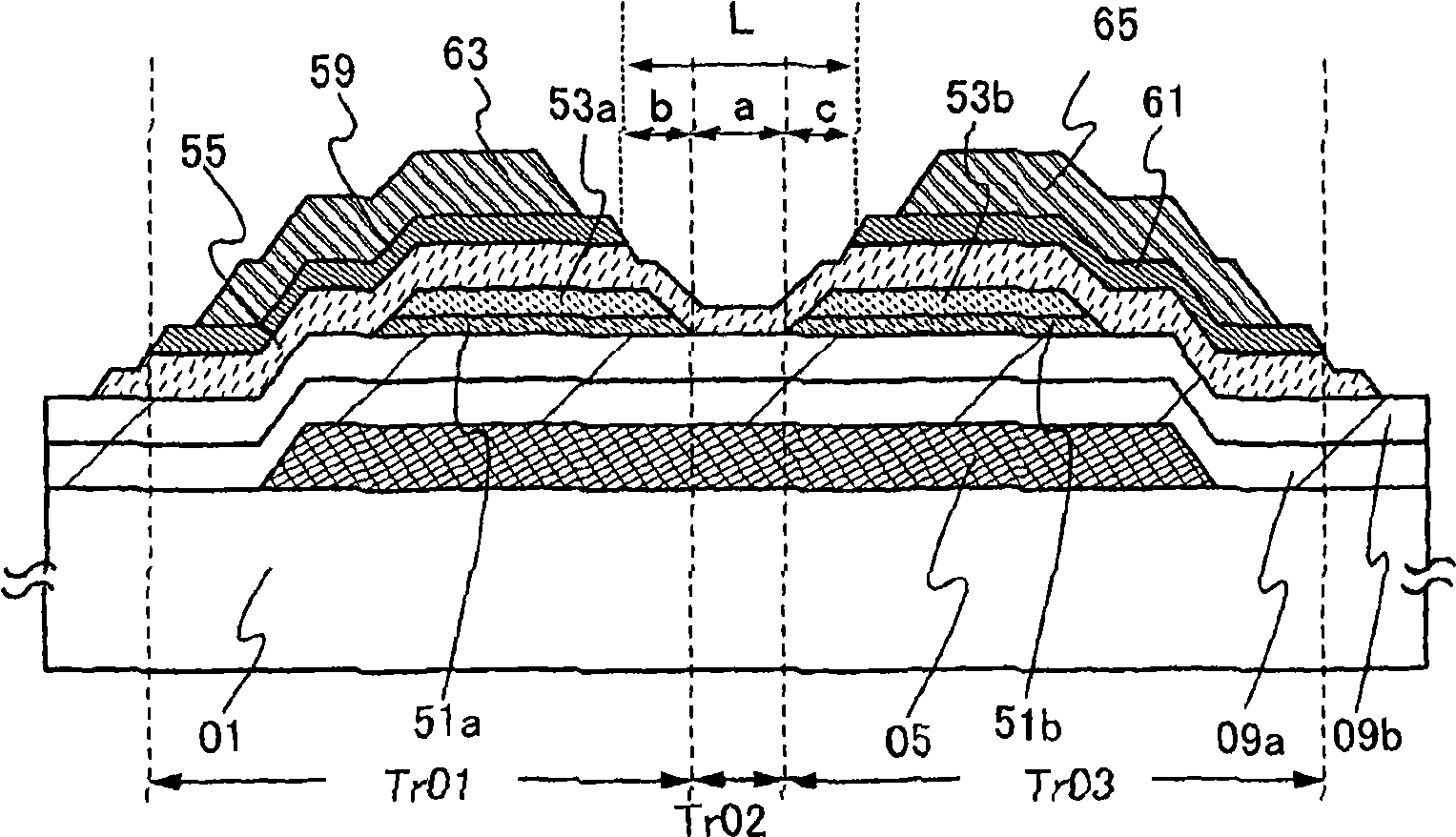

[0057] Here, refer to Figures 1A to 1C The structure of a thin film transistor is described, the cut-off current is lower than that of the thin film transistor with the microcrystalline semiconductor layer in the channel formation region, and its working speed and conduction current are higher than those of the thin film transistor with the amorphous semiconductor layer in the channel formation region.

[0058] exist Figure 1A In the thin film transistor shown, a gate electrode 05 is formed on a substrate 01, gate insulating layers 09a and 09b are formed on the gate electrode 05, and separated conductive layers 51a and 51b are formed on the gate insulating layer 09b. , and separate buffer layers 53a and 53b are formed on the conductive layers 51a and 51b. The buffer layers 53a and 53b substantially overlap the conductive layers 51a and 51b. In addition, an amorphous semiconductor layer 55 covering the side surfaces and upper surfaces of the conductive layers 51a and 51b an...

Embodiment approach 2

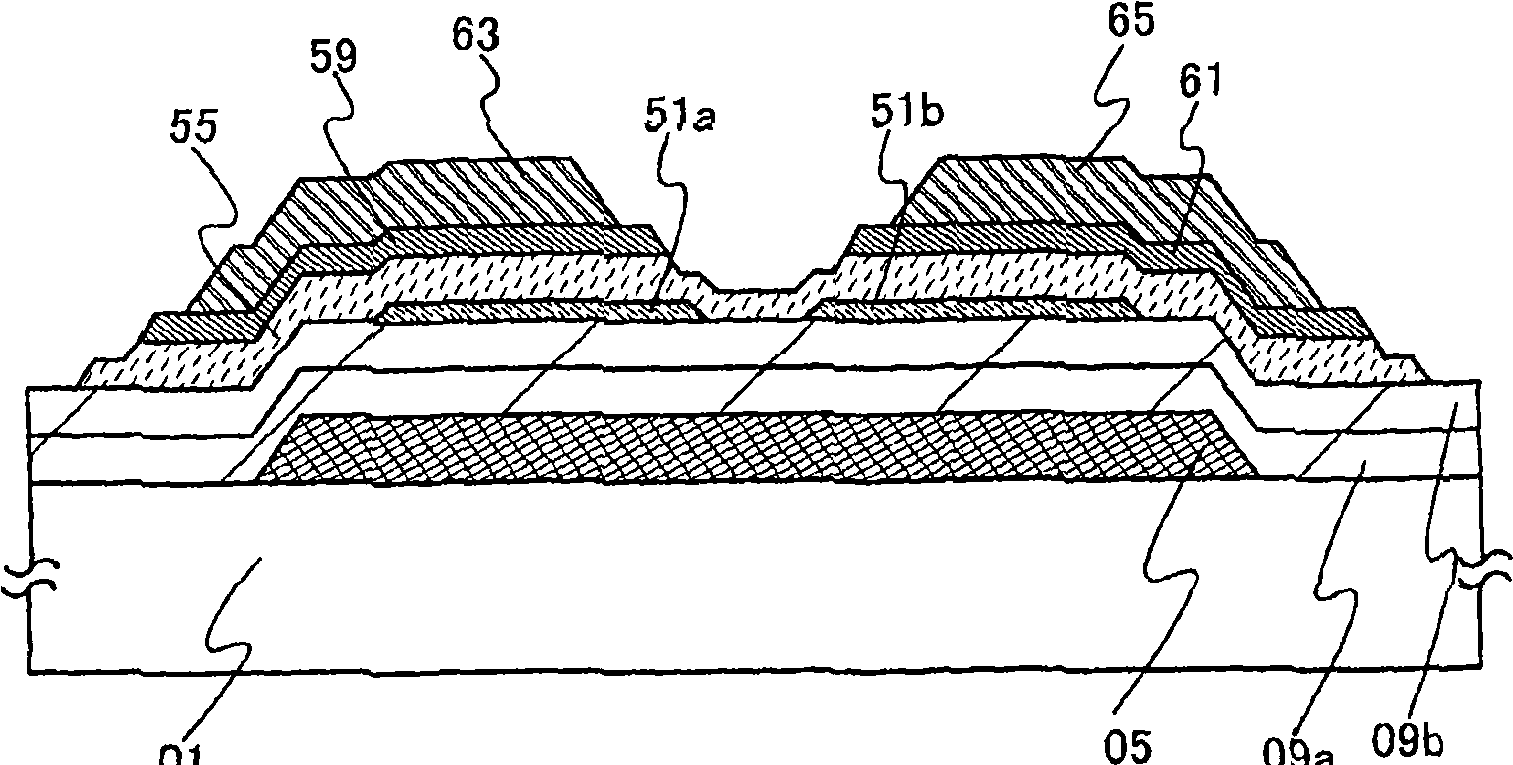

[0102] In this embodiment, refer to figure 2 Other shapes of the conductive layers 51a and 51b and the buffer layers 53a and 53b are shown.

[0103] figure 2 The shown thin film transistor is a thin film transistor in which the buffer layers 53c and 53d are respectively formed inside the separated conductive layers 51c and 51d in its cross-sectional structure, that is, the buffer layers 53c and 53d are formed with an area smaller than that of the conductive layers 51c and 51d. And the thin film transistors of the conductive layers 51c and 51d are partially exposed from the buffer layers 53c and 53d. By adopting this structure, when the conductive layers 51c and 51d are microcrystalline semiconductor layers, metal silicide layers or metal layers, the contact conduction can be improved by using the microcrystalline semiconductor layers, metal silicide layers or metal layers as crystal growth nuclei. The crystallinity of the amorphous semiconductor layer 55 of the layers 51c ...

Embodiment approach 3

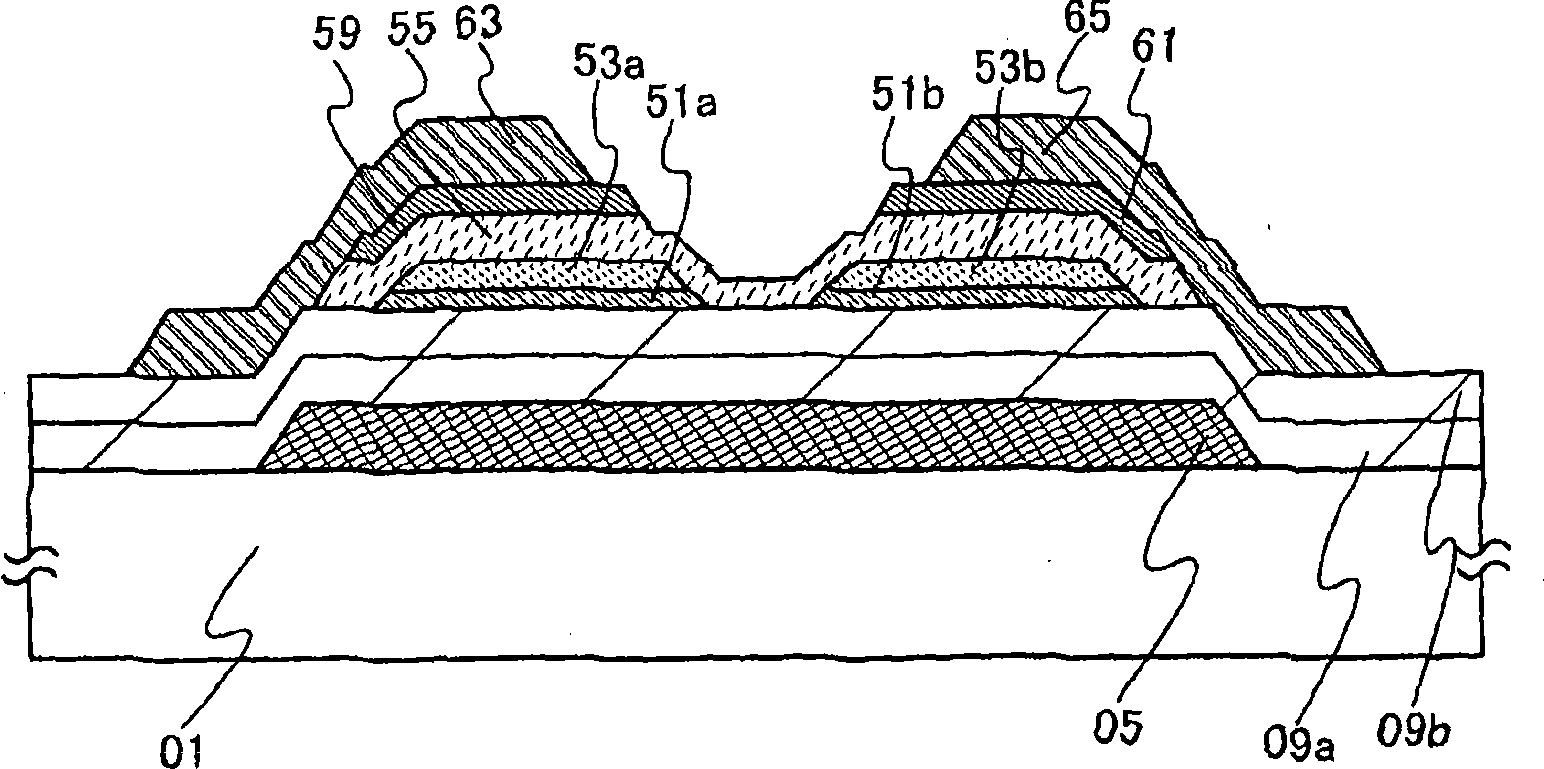

[0107] In this embodiment, refer to Figure 3A and 3B Other ways of showing buffer layers. The present embodiment is characterized in that the buffer layers 52a and 52b are formed of insulating layers.

[0108] exist Figure 3A In the thin film transistor shown, a gate electrode 05 is formed on a substrate 01, gate insulating layers 09a and 09b are formed on the gate electrode 05, and separated conductive layers 51a and 51b are formed on the gate insulating layer 09b. , and separate buffer layers 52a and 52b are formed on the conductive layers 51a and 51b. The buffer layers 52a and 52b substantially overlap the conductive layers 51a and 51b. Furthermore, an amorphous semiconductor layer 55 is formed to cover the side surfaces and upper surfaces of the conductive layers 51a and 51b and the buffer layers 52a and 52b. A pair of impurity semiconductor layers 59 and 61 to which an impurity element imparting one conductivity type is added is formed on the amorphous semiconducto...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical conductivity | aaaaa | aaaaa |

| electrical conductivity | aaaaa | aaaaa |

| particle diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More