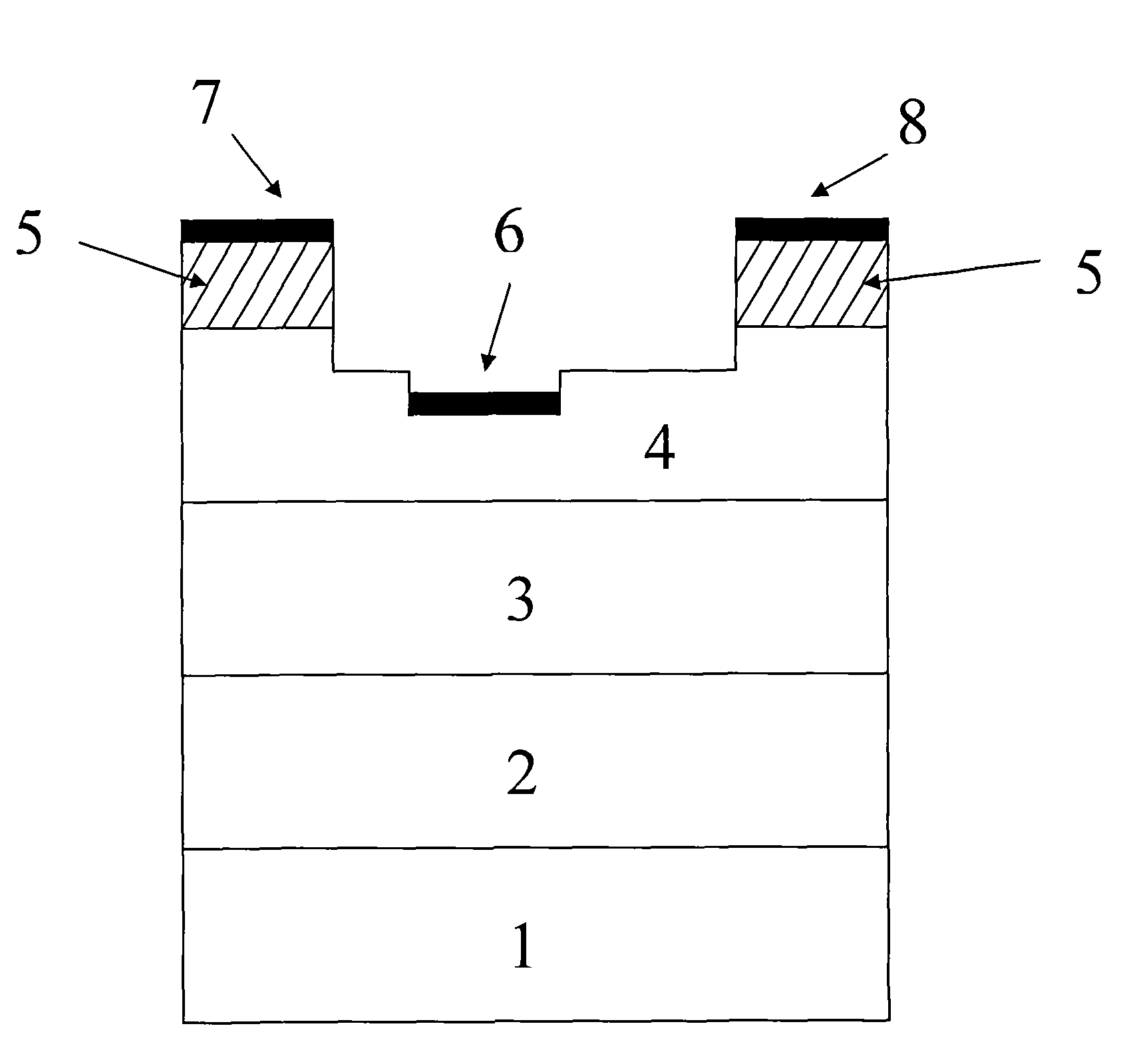

Metal-semiconductor field effect transistor and production method thereof

A field-effect transistor and manufacturing method technology, applied in the manufacture of high-frequency and high-power integrated circuits, the field-effect transistor field, can solve the problems of reduced leakage current, reduced electron mobility, trap effect, etc., so as to reduce the contact area, improve the Control ability, the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

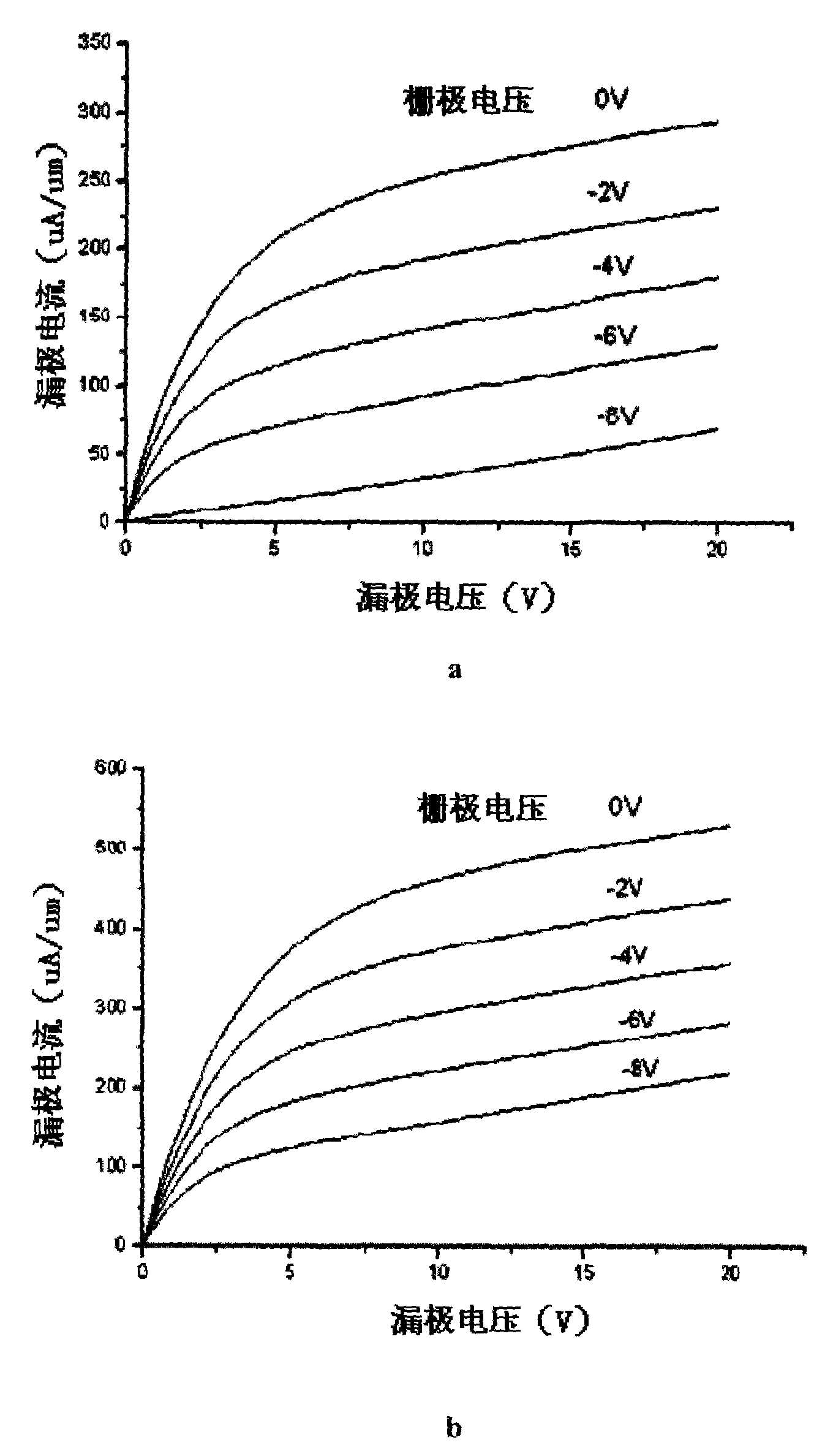

Embodiment 1

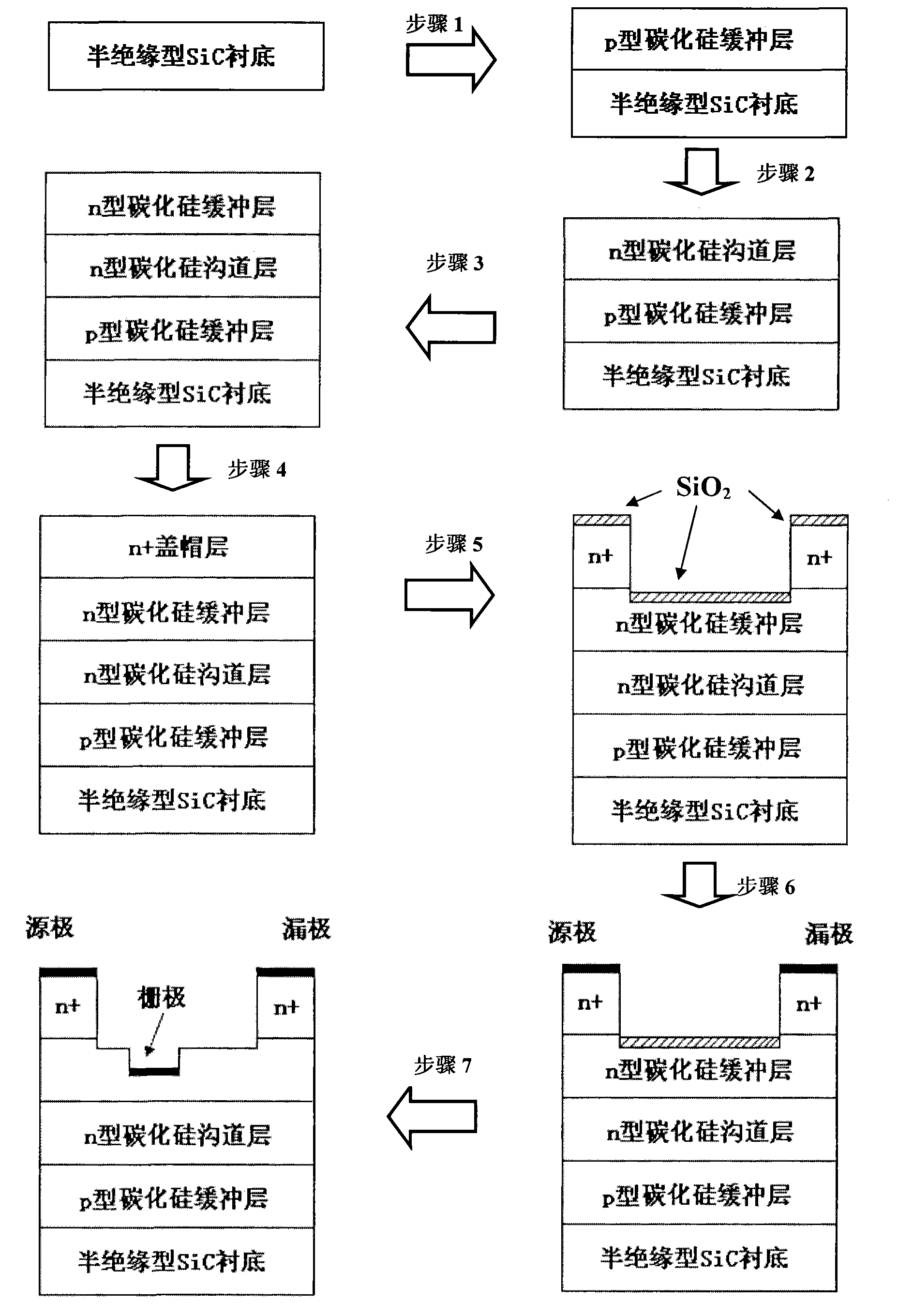

[0030] Embodiment 1, the specific process of making the device of the present invention is as follows:

[0031] Step 1, epitaxially growing a p-type silicon carbide buffer layer.

[0032] On a semi-insulating silicon carbide substrate, a layer of p-type doping is epitaxially grown with a concentration of 1.4×10 15 cm -3 , a p-type epitaxial buffer layer with a thickness of 0.50 μm.

[0033]Step 2, epitaxially growing an n-type silicon carbide channel layer.

[0034] On the p-type silicon carbide buffer layer, a layer of n-type doping is epitaxially grown with a concentration of 3.4×10 17 cm -3 , n-type silicon carbide channel layer with a thickness of 0.26 μm.

[0035] Step 3, epitaxially growing an n-type silicon carbide buffer layer.

[0036] On the n-type silicon carbide channel layer, a layer of n-type doping is epitaxially grown with a concentration of 1.4×10 15 cm -3 , an n-type silicon carbide buffer layer with a thickness of 0.10 μm.

[0037] Step 4, epitaxial...

Embodiment 2

[0049] Embodiment 2, the specific process of making the device of the present invention is as follows:

[0050] Step 1, epitaxially growing a p-type silicon carbide buffer layer.

[0051] On a semi-insulating silicon carbide substrate, a layer of p-type doping is epitaxially grown with a concentration of 1.0×10 15 cm -3 , a p-type epitaxial buffer layer with a thickness of 0.80 μm.

[0052] Step 2, epitaxially growing an n-type silicon carbide channel layer.

[0053] On the p-type silicon carbide buffer layer, epitaxially grow a layer of n-type doping with a concentration of 4.0×10 17 cm -3 , n-type silicon carbide channel layer with a thickness of 0.20 μm.

[0054] Step 3, epitaxially growing an n-type silicon carbide buffer layer.

[0055] On the n-type silicon carbide channel layer, epitaxially grow a layer of n-type doping with a concentration of 1.0×10 15 cm -3 , an n-type silicon carbide buffer layer with a thickness of 0.05 μm.

[0056] Step 4, epitaxially grow...

Embodiment 3

[0068] Embodiment 3, the specific process of making the device of the present invention is as follows:

[0069] Step 1, epitaxially growing a p-type silicon carbide buffer layer.

[0070] On a semi-insulating silicon carbide substrate, a layer of p-type doping is epitaxially grown with a concentration of 2.0×10 15 cm -3 , a p-type epitaxial buffer layer with a thickness of 0.60 μm.

[0071] Step 2, epitaxially growing an n-type silicon carbide channel layer.

[0072] On the p-type silicon carbide buffer layer, a layer of n-type doping is epitaxially grown with a concentration of 1.0×10 17 cm -3 , n-type silicon carbide channel layer with a thickness of 0.40 μm.

[0073] Step 3, epitaxially growing an n-type silicon carbide buffer layer.

[0074] On the n-type silicon carbide channel layer, a layer of n-type doping is epitaxially grown with a concentration of 2.0×10 15 cm -3 , an n-type silicon carbide buffer layer with a thickness of 0.15 μm.

[0075] Step 4, epitaxia...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More