Ultrahigh-speed comparator with low offset

An ultra-high-speed comparator technology, applied in instruments, multiple input and output pulse circuits, analog/digital conversion, etc., can solve problems affecting the accuracy of comparators, limiting the application of CMOS latch comparators, and large offset voltages. Achieve the needs of good design, meet the needs of design, and improve the effect of speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028]In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the embodiments of the present invention will be further described in detail below in conjunction with the embodiments and the accompanying drawings. Here, the exemplary embodiments and descriptions of the present invention are used to explain the present invention, but not to limit the present invention.

[0029] At first, the technical term involved in the present invention is explained:

[0030] PMOS: P-channel metal oxide semiconductor FET, P-channel metal oxide semiconductor field effect transistor;

[0031] NMOS: N-channel metal oxide semiconductor FET, N-channel metal oxide semiconductor field effect transistor.

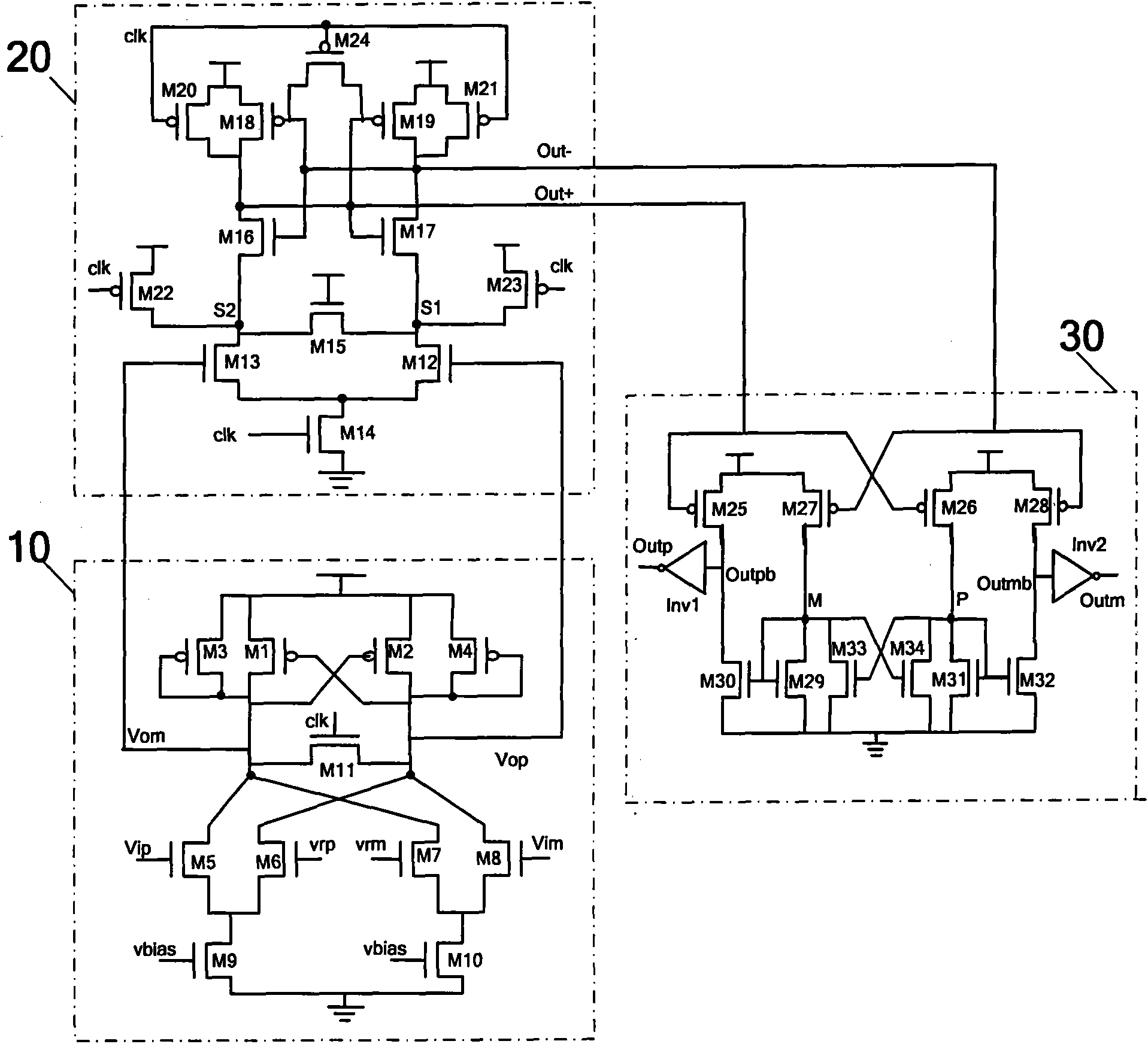

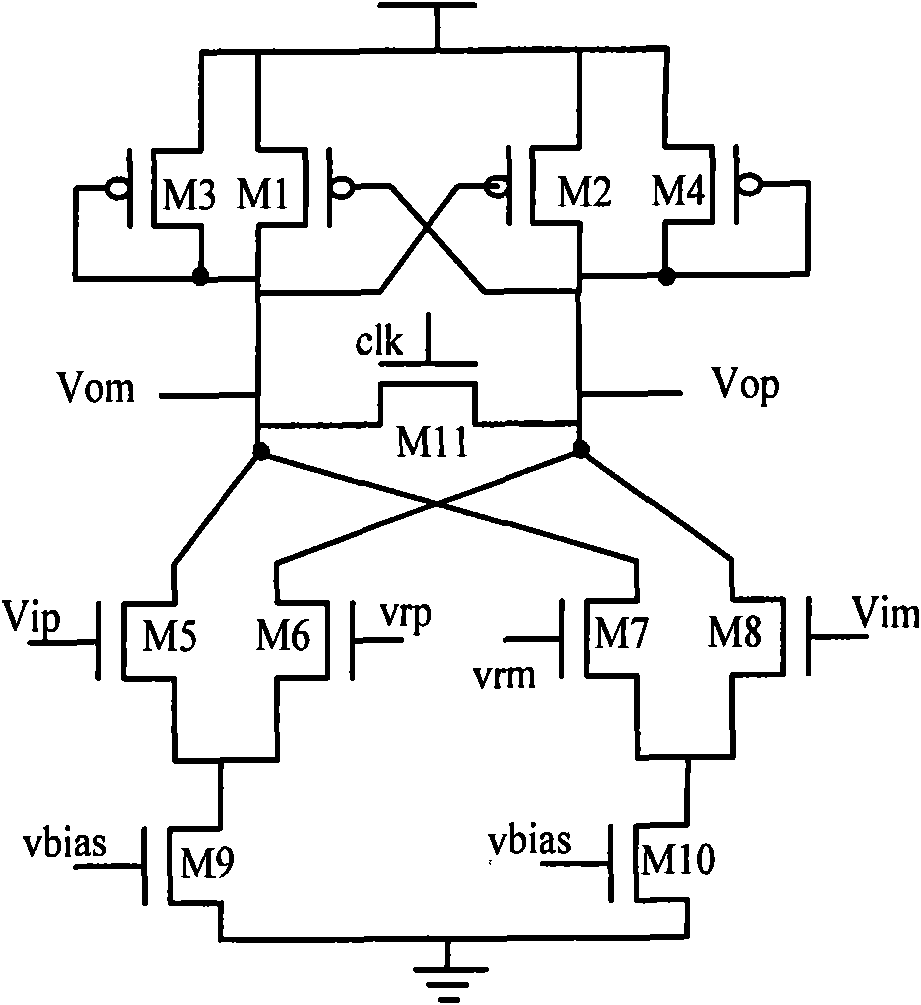

[0032] see figure 1 , is a functional structural block diagram of an ultra-high-speed comparator in an embodiment of the present invention. As can be seen from the figure, the ultra-high-speed comparator includes a sequentially connecte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More