Method and device for forming vertical through hole in semiconductor

A vertical through-hole and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of inflexible process and non-vertical side wall, and achieve flexible process, vertical side wall, improved integrity and Effect of insulating properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

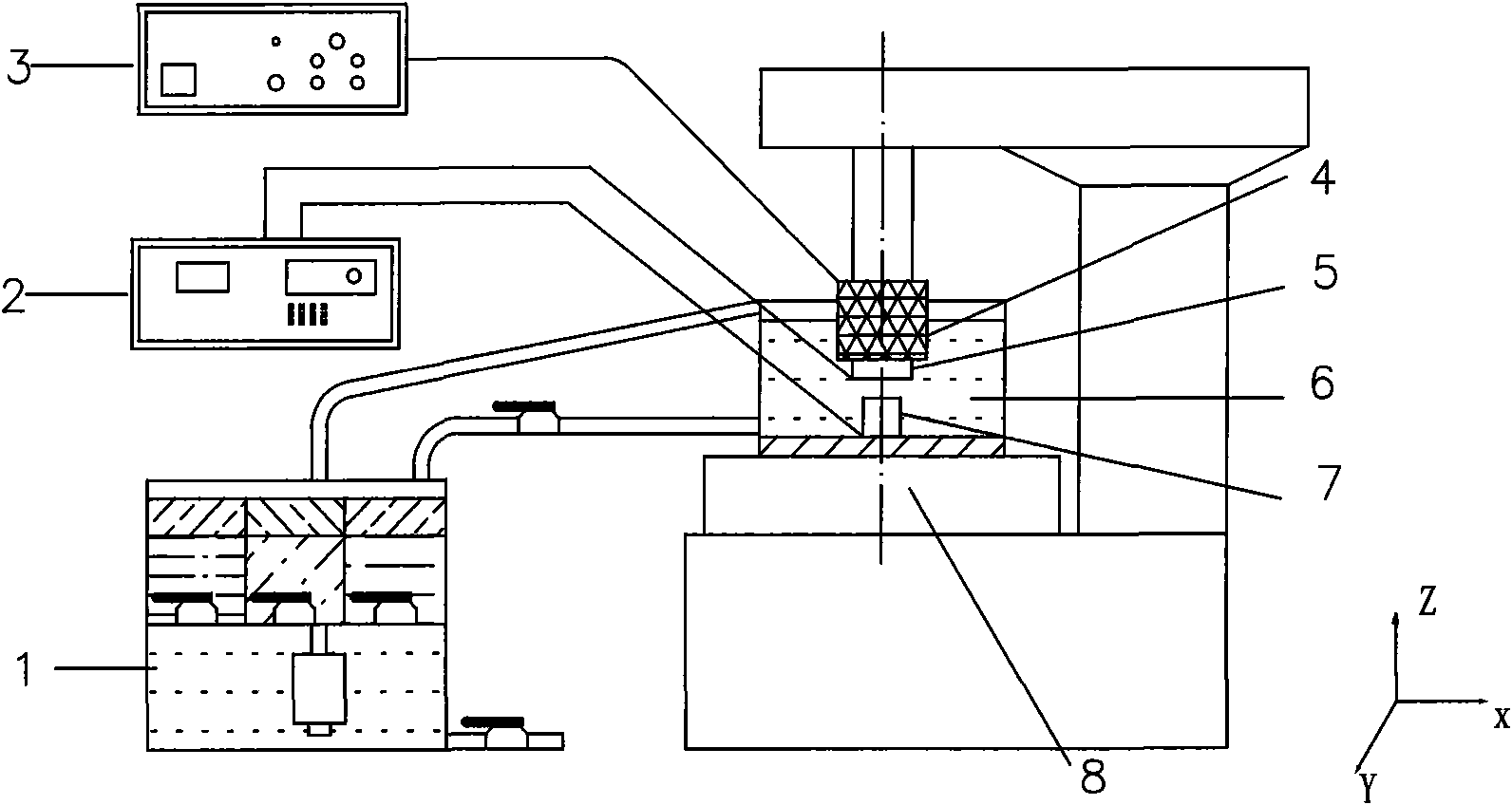

[0026] Take the vertical via hole processing of single crystal silicon material as an example:

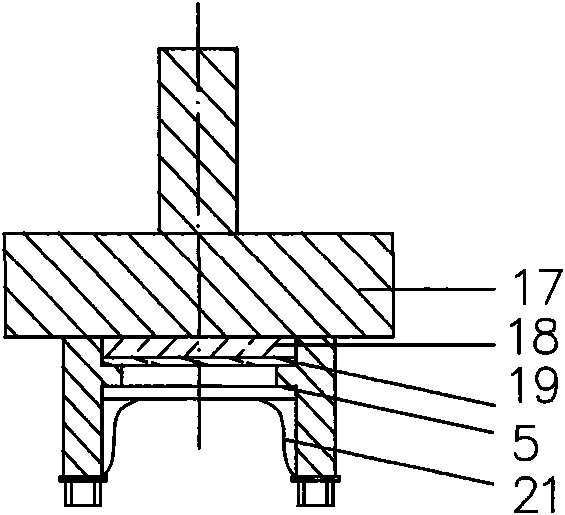

[0027] In the micro-EDM process, the micro-energy pulse power supply 2 strictly controls the single-pulse discharge energy (<50μJ) and its inter-electrode distribution to ensure sub-micron discharge gaps and realize semiconductor materials (resistivity <100Ω cm). Micro-etching and micro-electrodes are less and loss-free, and the positioning accuracy and feed resolution of the micro-electrodes are guaranteed through the three-coordinate sub-micron motion control platform 8, and semiconductor through holes are processed.

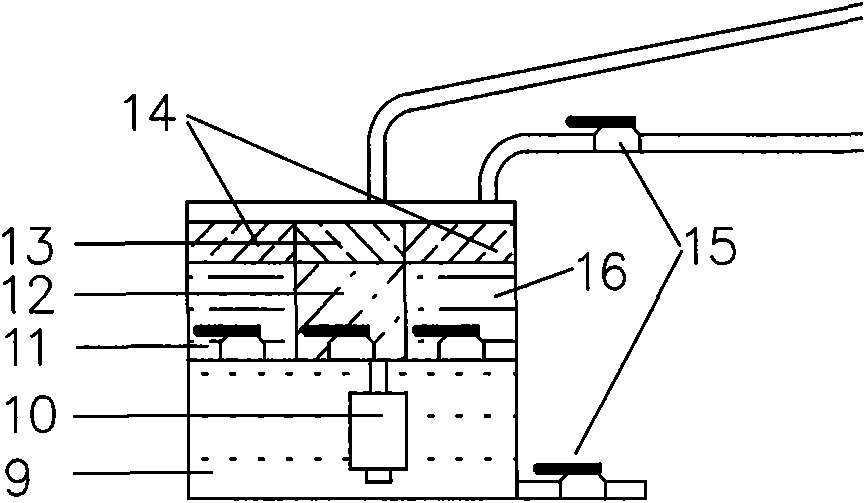

[0028]In order to improve the product removal status in the process of semiconductor vertical through-hole processing, on the one hand, measures such as the sub-micron working feed rate and rapid retraction of the inverted semiconductor workpiece 5 and the tool electrode 7 are adopted to reduce the phenomenon of short-circuit and arcing; on the other hand, By addin...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More