SRAM dual-position unit wiring method

A wiring method and bit cell technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of increasing the coupling capacitance of surrounding wiring and increasing the resistance of its own wiring, so as to improve the working characteristics and reduce the Coupling capacitors, the effect of reducing resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

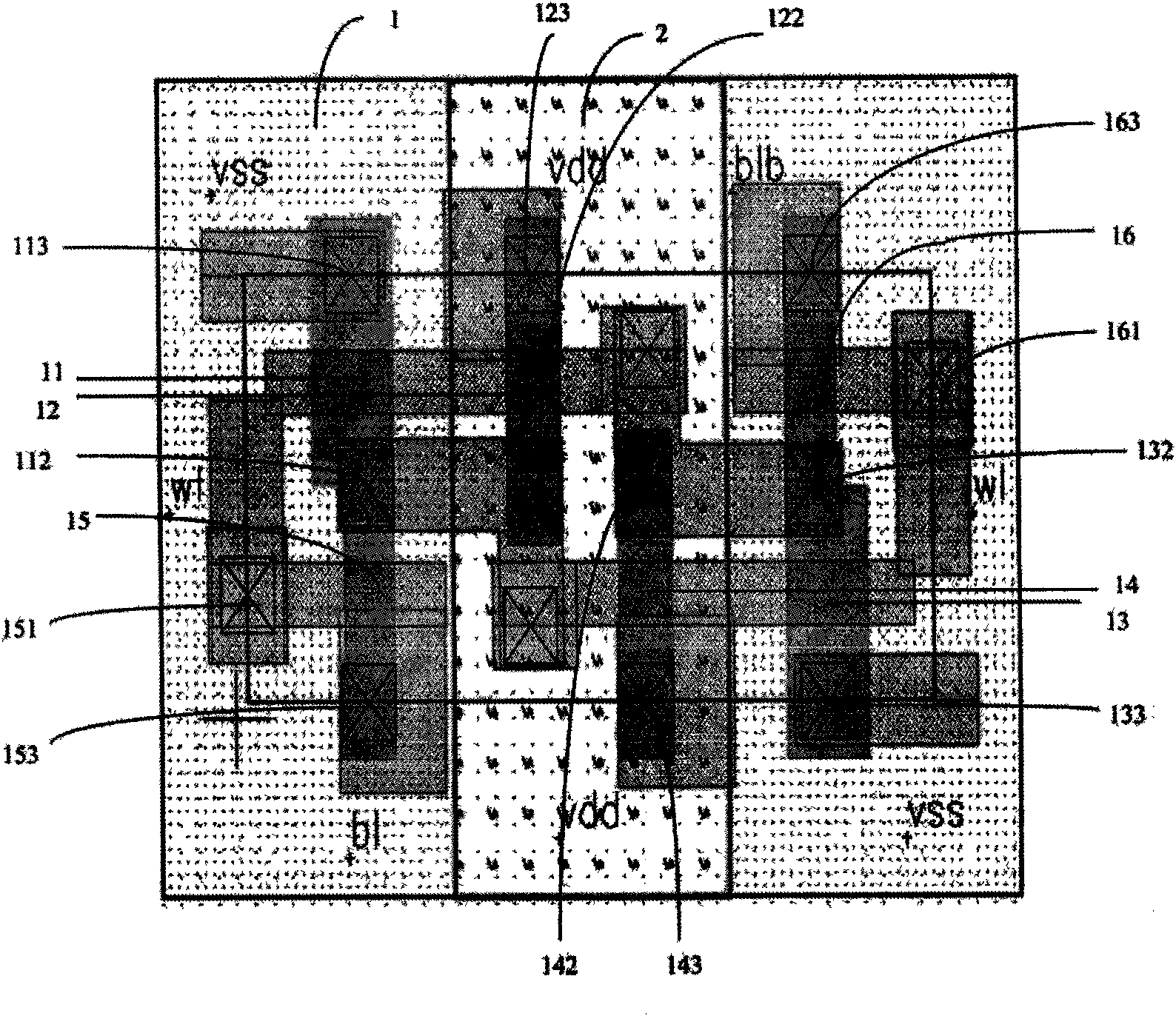

[0018] In order to make the purpose and features of the present invention more comprehensible, the specific implementation manners of the present invention will be further described below in conjunction with the accompanying drawings.

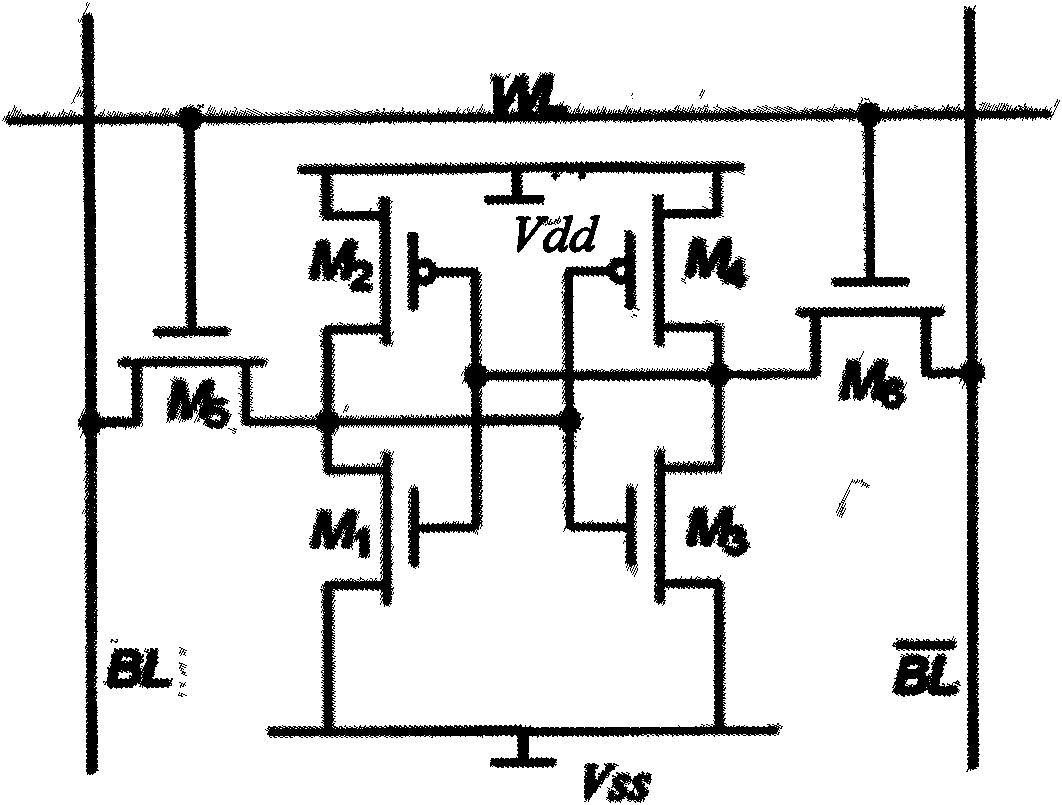

[0019] It has been mentioned in the background technology that in the layout of the existing 2x2SRAM cell, the bit lines BL and BLb use higher-level Metal3 for wiring, which not only increases the resistance on its own wiring, but also increases the connection with the surrounding wiring. Coupling capacitors reduce the operating characteristics of the SRAM.

[0020] The core idea of the present invention is that the bit lines BL and BLb are wired using lower-level Metal2, and the word line WL is wired using Metal3, thereby greatly reducing the parasitic resistance and capacitance of the bit lines BL and BLb, and improving the performance of the SRAM. working characteristics.

[0021] Figure 6 For the present invention in such as figure 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More