Rapid locking method for full digital phase-locked loop

An all-digital phase-locked loop, fast locking technology, applied in the direction of automatic power control, electrical components, etc., can solve the phase-locked loop deterioration phase-locked loop output clock jitter performance phase-locked loop system stability, phase-locked loop locking time Not ideal, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

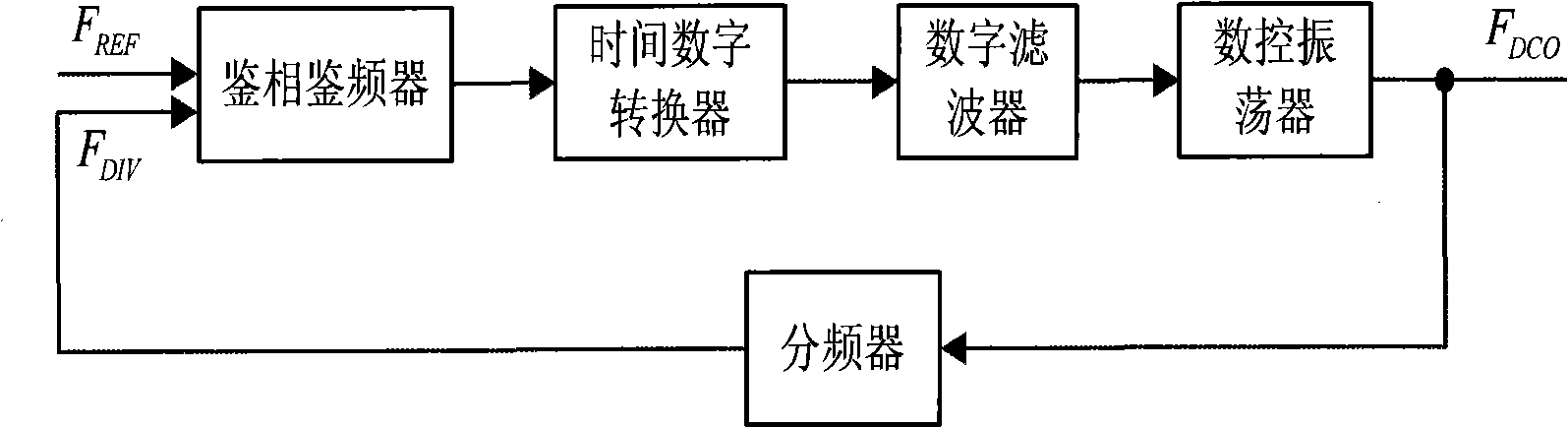

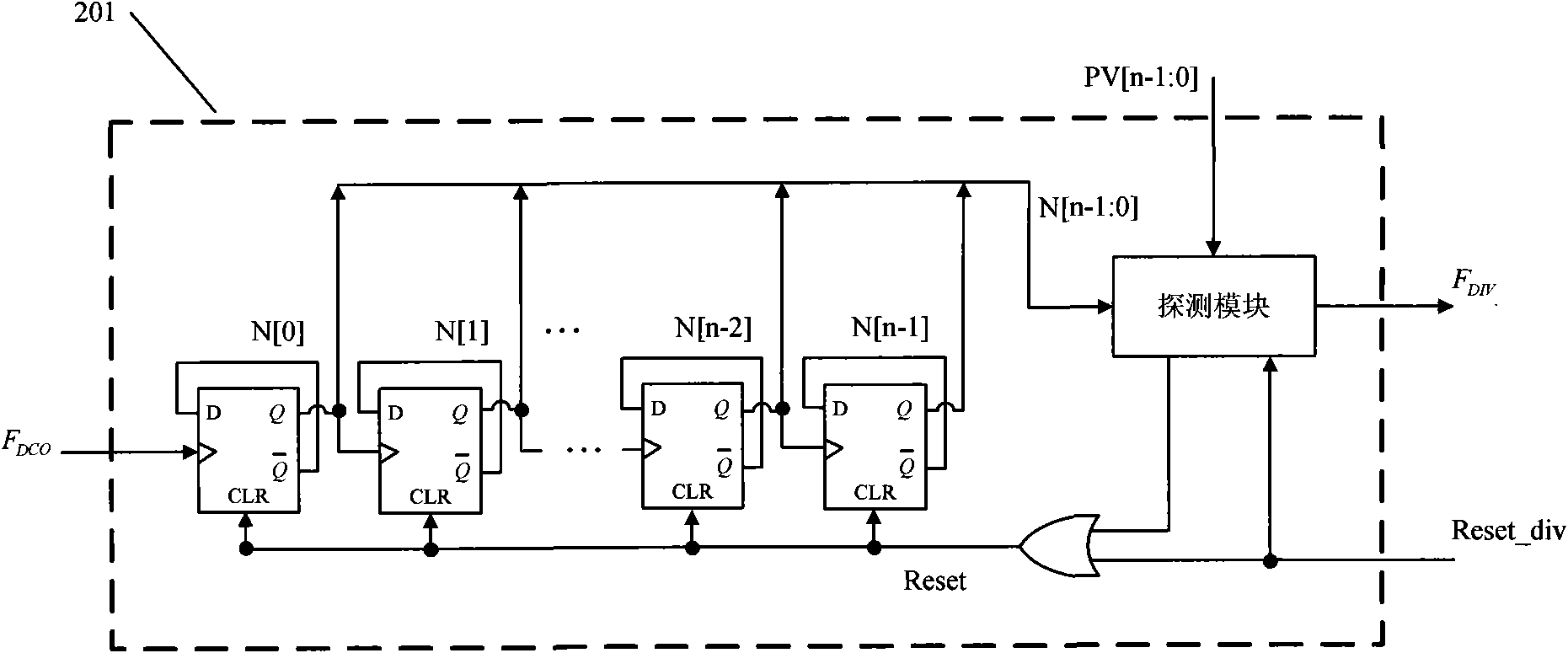

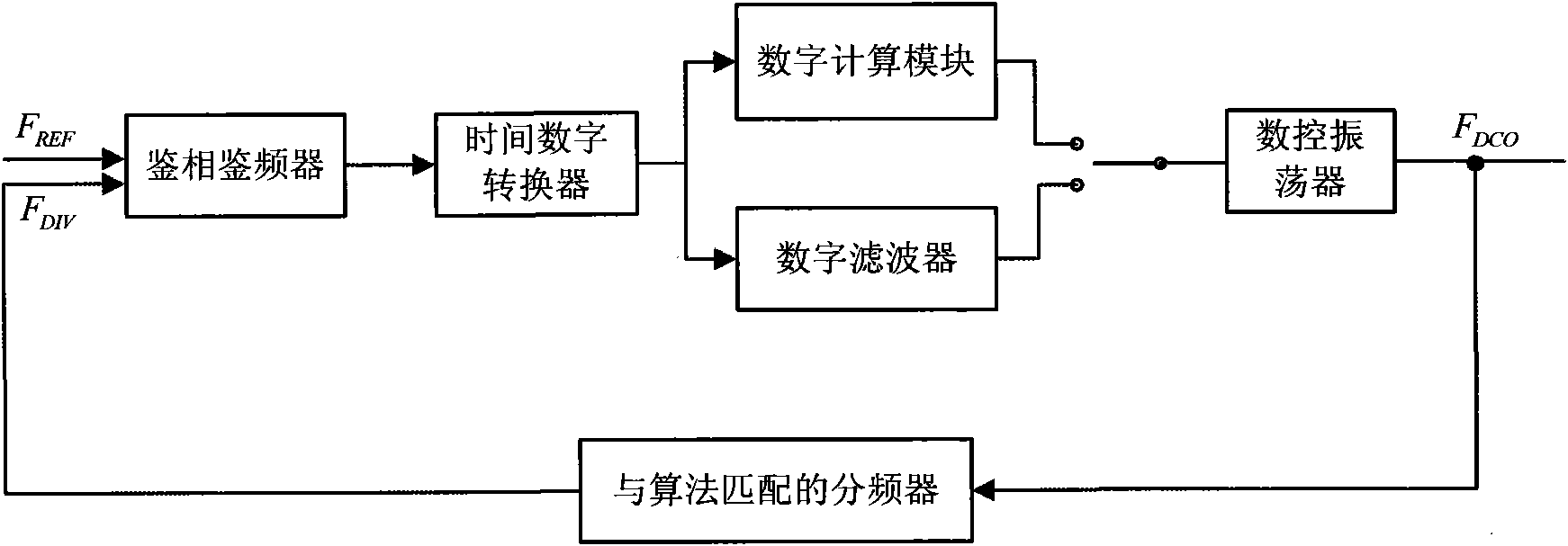

[0052] see image 3 , the all-digital phase-locked loop of the fast frequency capture algorithm proposed by the present invention is provided with two loops of fast frequency capture and phase locking, and the two loops work alternately. First, the frequency capture is completed by the fast frequency capture loop, and then by A phase-locked loop completes precise locking. Among them, the fast frequency capture loop includes a phase frequency detector, a time-to-digital converter, a digital filter, a digital calculation module, a digitally controlled oscillator and a frequency divider that matches the algorithm. When the phase-locked loop is just working, the phase detector detects the phase difference, the time-to-digital converter converts the phase difference into a digital signal, and the digital calculation module generates the control wo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More