Method for forming flash memory grid electrode and flash memory

A memory gate and flash technology, applied in the direction of electric solid-state devices, semiconductor devices, transistors, etc., can solve the problem of reducing the electrical performance of the control gate, and achieve the effect of preventing the decline of electrical performance and eliminating sags

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

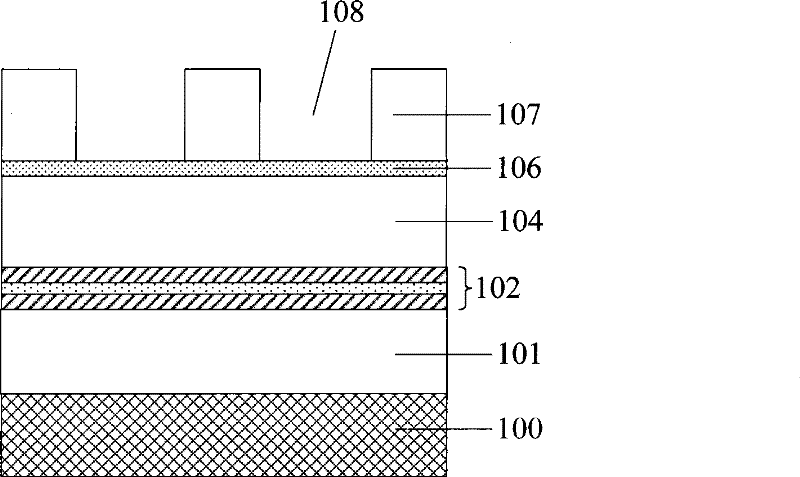

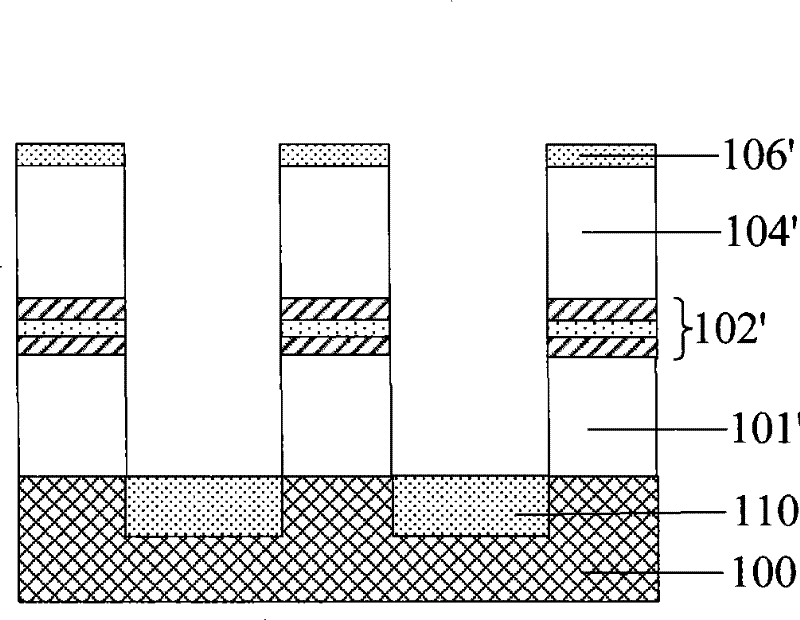

[0023] The inventors found that if figure 2 As shown, since the existing flash memory gate structure is a stacked structure of the floating gate 101' and the control gate 104' sandwiching the inter-gate dielectric layer 102'. The main material for forming the floating gate 101' and the control gate 104' is polysilicon. Therefore, during the process of etching to form the floating gate 101', the sidewalls of the unprotected control gate 104' must be eroded by the plasma as an etchant. Although plasma etching is anisotropic etching, the etching rate in the direction parallel to the substrate 100 is much smaller than that in the direction perpendicular to the substrate 100 . However, as the size of the flash memory device gradually decreases, the aspect ratio of the trenches between the gates gradually increases, and the plasma contacts the sidewalls of the control gate 104' relatively more, so the plasma has more contact with the control gate 104'. The erosion of the sidewall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More