Fully-automatic aligning high-pressure N-shaped DMOS device and manufacturing method thereof

A self-aligned, N-type technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as difficult to obtain, never had self-aligned drain applications, small on-resistance, etc. Achieve the effect of breaking through the limitation of process size, reducing size, and reducing on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

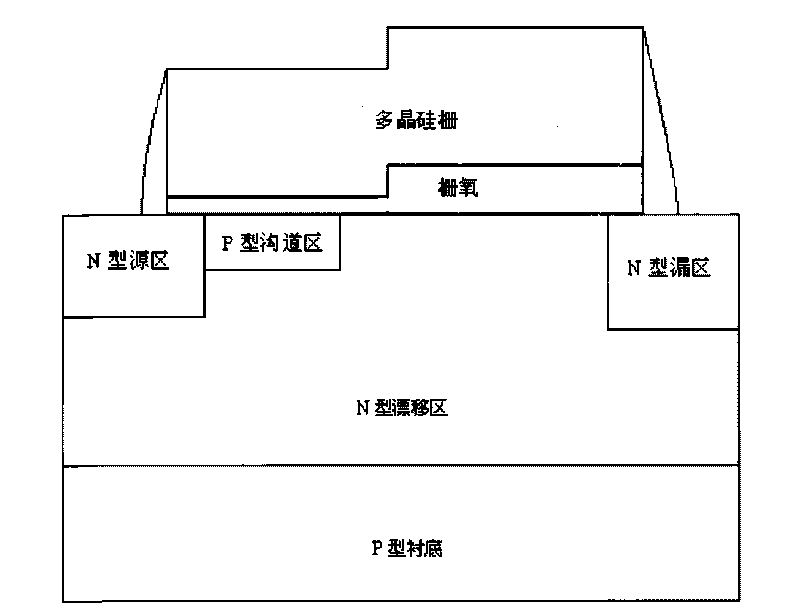

[0025] The key to the method for making a fully self-aligned N-type DMOS device in the BCD process flow of the present invention is to use a fully self-aligned process to realize the N-type DMOS device, so that the tertiary photoelectric process of the channel, the drift region and the drain is omitted. engraving, and finally realize the minimization of device size.

[0026] The process of the specific implementation of the method of the present invention is:

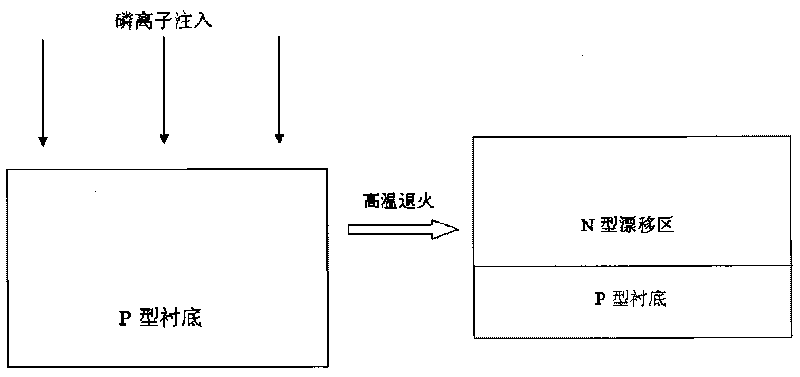

[0027] Step 1, see figure 2 As shown, high-energy phosphorus ion implantation is performed on the entire N-type DMOS device region on the P-type substrate, and high-temperature annealing is performed to finally form an N-type drift region on the P-type substrate. Phosphorus ion implantation dose at 1×10 13 cm -2 to 2×10 13 cm -2 , the implantation energy is 1000keV to 2000keV, the annealing temperature is 1500°C to 1800°C, and the annealing time is 1 hour to 3 hours.

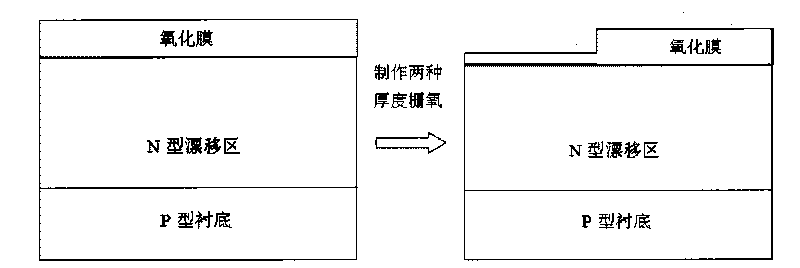

[0028] Step two, see image 3 As shown, a f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More