Chip scale package structure of CMOS (complementary metal-oxide-semiconductor) image sensor and packaging method

An image sensor and chip-level packaging technology, which is applied in the semiconductor field, can solve the problems of a large number of connecting wires, affecting the freedom of connecting wire layout, and it is difficult to reduce the packaging area, so as to improve efficiency and reduce defect dislocations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

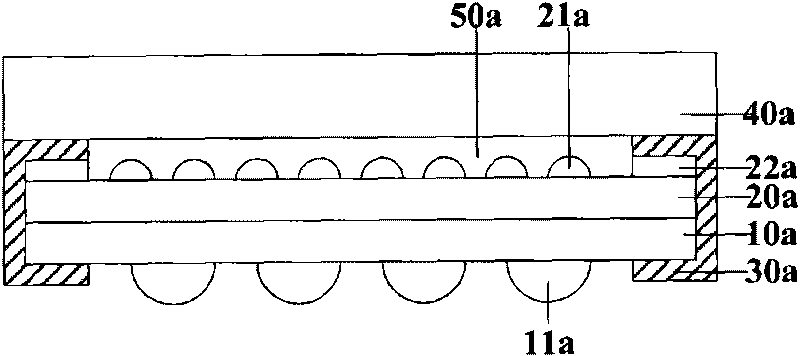

[0016] The first embodiment of the present invention provides a chip-level packaging method for a CMOS semiconductor image sensor, including providing a semiconductor substrate, forming a photoelectric conversion layer in the semiconductor substrate, forming a wiring layer on the surface of the photoelectric conversion layer, and the wiring layer Discrete connection pads are formed on the surface; an adhesion layer is formed on the surface of the wiring layer, and the adhesion layer covers the connection pads; a supporting layer is formed on the surface of the adhesion layer; the semiconductor substrate is thinned until the photoelectric conversion layer is exposed, and the photoelectric conversion layer The pixel elements distributed in an array and the connecting layer between the pixel elements are formed on it, the height of the connecting layer is higher than that of the pixel elements; a light-transmitting layer is formed on the connecting layer, and the light-transmitting...

no. 2 approach

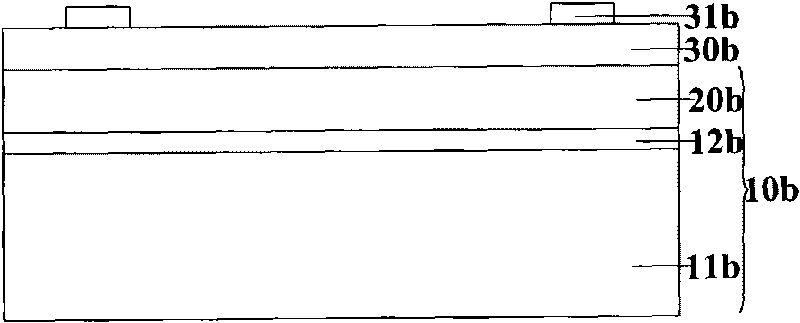

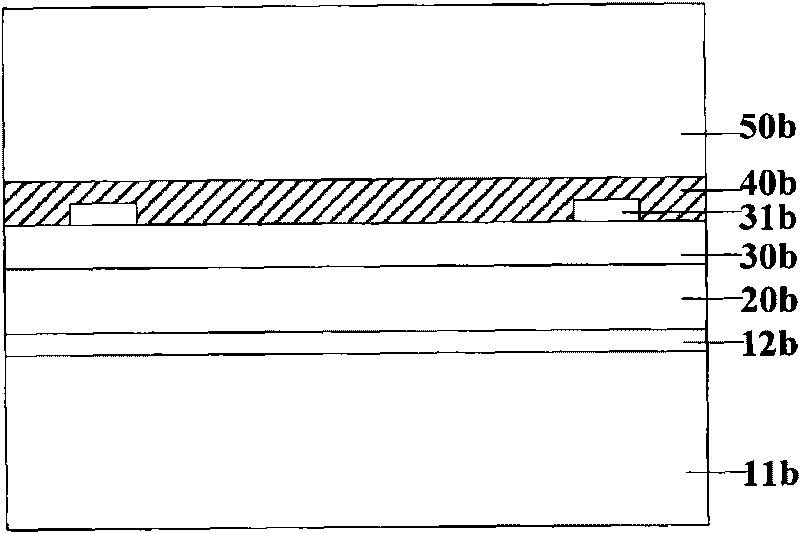

[0039] The second embodiment of the present invention provides a chip-level packaging method for a CMOS semiconductor image sensor, including providing a semiconductor substrate, forming a photoelectric conversion layer in the semiconductor substrate, forming a wiring layer on the surface of the photoelectric conversion layer, and the wiring layer Discrete connection pads are formed on the surface; an adhesion layer is formed on the surface of the wiring layer, and the adhesion layer covers the connection pads; a supporting layer is formed on the surface of the adhesion layer; the semiconductor substrate is thinned until the photoelectric conversion layer is exposed, and the photoelectric conversion layer The pixel elements distributed in an array and the connection layer between the pixel elements are formed on it, and the height of the connection layer is higher than the pixel elements; a light-transmitting layer is formed on the connection layer, and the light-transmitting la...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More