High-spectrum image dimensionality reduction chip

A hyperspectral image and dimensionality reduction technology, applied in the field of image processing, can solve the problems of no real-time processing, no real-time dimensionality reduction processing of hyperspectral images, and achieve high module utilization efficiency, low research and development risk, and short development cycle. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

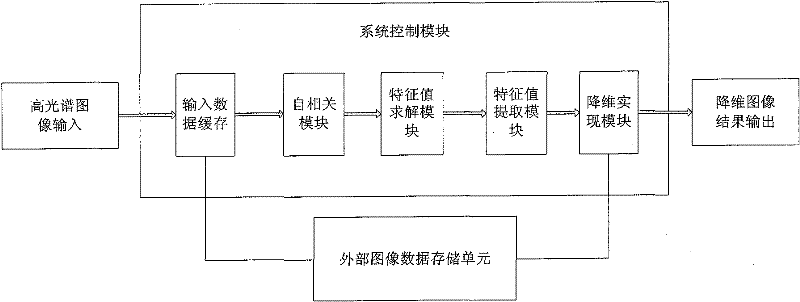

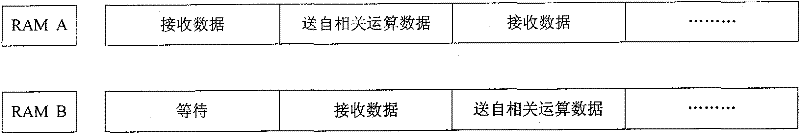

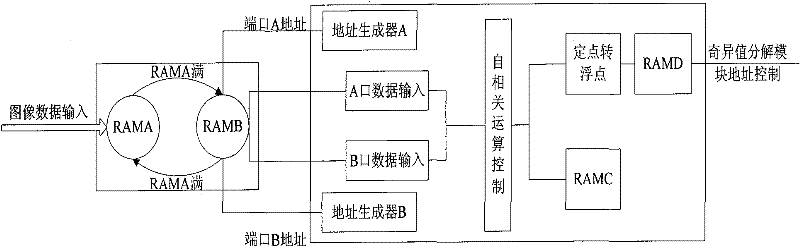

[0021] see figure 1 System-on-a-chip structure diagram. In this embodiment, the Vertix5 series experiment board of Xilinx Company is used to design, simulate and verify the dimensionality reduction chip. The whole chip system can be divided into five modules: system control module, autocorrelation module, eigenvalue solving module, eigenvalue extraction module, and dimension reduction realization module. Due to the massive amount of hyperspectral image data, there is not enough storage unit inside the FPGA to store the entire hyperspectral image, so an additional storage unit needs to be added externally, and a data input buffer needs to be added at the front end of the image transmission to make the hyperspectral image The image data is output to subsequent modules in the form of block matrix. The divided modules are independent of each oth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More