Epitaxy method for improving 4H-SiC basal plane dislocation conversion rate

A technology of basal plane dislocation and conversion rate, applied in the field of microelectronics, can solve the problems of reduced basal plane dislocation conversion rate, reduced device reliability, unclear growth mechanism, etc., to improve the conversion rate, simplify the process, and shorten the preparation. effect of cycles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

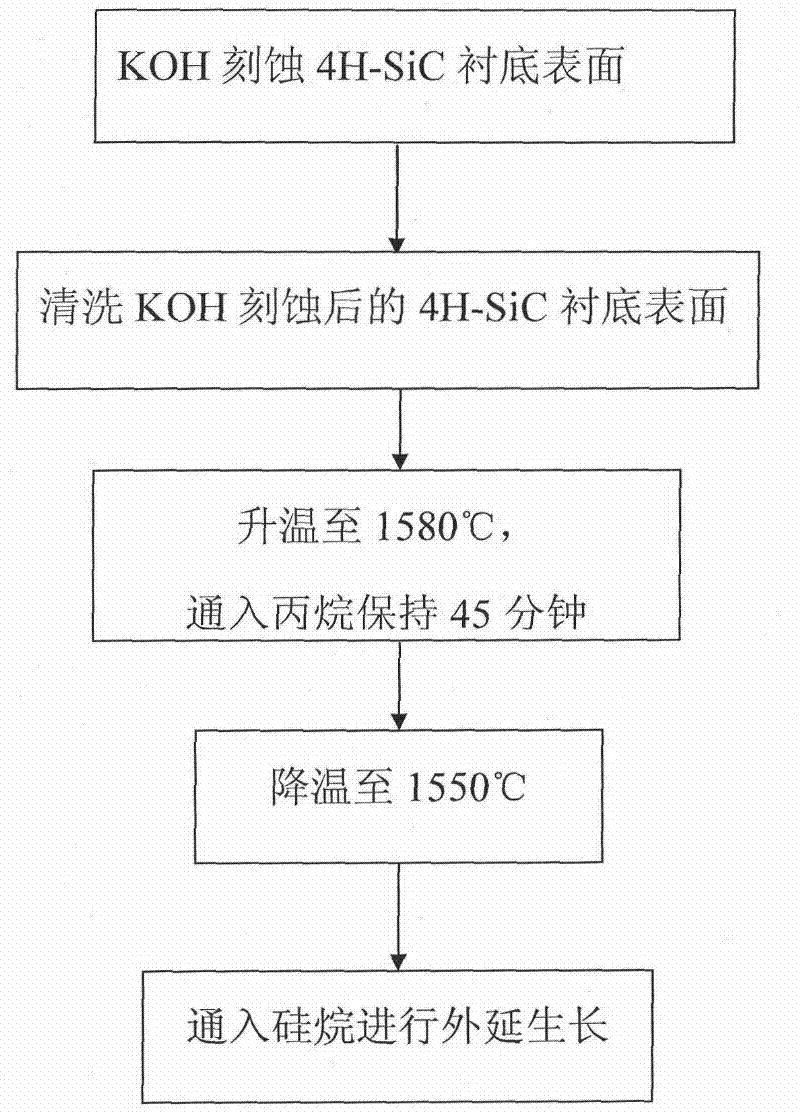

[0020] Embodiment 1, the implementation steps are as follows:

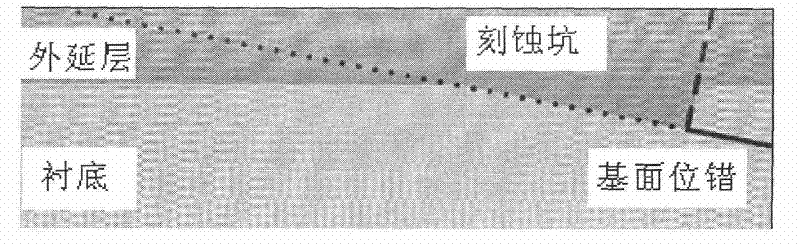

[0021] Step 1, the substrate is etched with KOH, the etching temperature is 480°C, and the etching time is 20min. The etched structure is as follows figure 2 shown.

[0022] Step 2: Clean the etched substrate surface with ethanol for the first cleaning to remove organic matter; use HF for the second cleaning of the etched substrate surface to remove ionic and atomic impurities; use high-purity water Carry out the third surface cleaning to ensure that the substrate surface is clean, and finally dry the surface moisture.

[0023] Step 3, place the cleaned 4H-SiC substrate in the CVD furnace cavity, and vacuumize the furnace so that the pressure in the furnace reaches 10 -7 Pa, raise the temperature in the furnace, and at the same time, feed hydrogen gas with a flow rate of 20l / min, raise the temperature to 1400°C, keep it for 5min, then feed it with a flow rate of 8ml / min propane, raise the temperature to 1580°C, ...

Embodiment 2

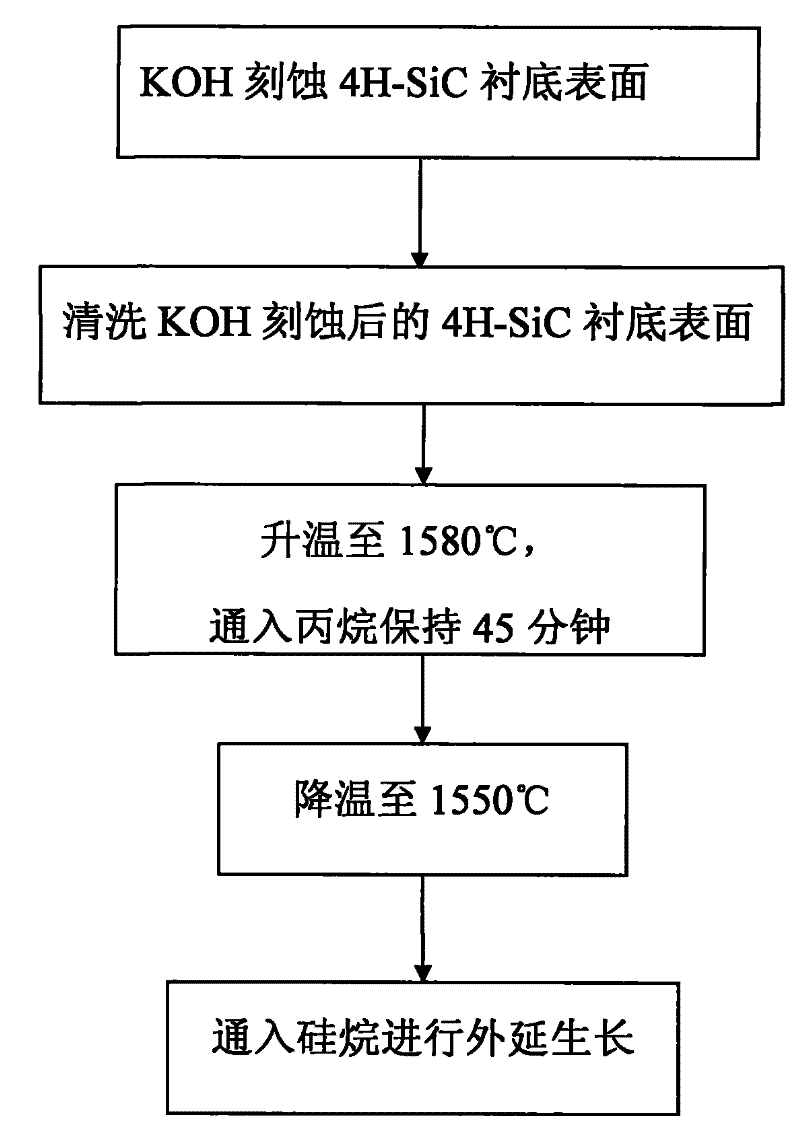

[0025] Embodiment 2, the implementation steps are as follows:

[0026] In step 1, the substrate is etched with KOH, the etching temperature is 520° C., and the etching time is 10 min.

[0027] Step 2: Clean the etched substrate surface with ethanol for the first cleaning to remove organic matter; use HF for the second cleaning of the etched substrate surface to remove ionic and atomic impurities; use high-purity water Carry out the third surface cleaning to ensure that the substrate surface is clean, and finally dry the surface moisture.

[0028] Step 3, place the cleaned 4H-SiC substrate in the CVD furnace cavity, and vacuumize the furnace so that the pressure in the furnace reaches 10 -7 Pa, raise the temperature in the furnace, and at the same time feed hydrogen with a flow rate of 50l / min, raise the temperature to 1500°C, keep it for 5min, then feed it with a flow rate of 15ml / min propane, raise the temperature to 1600°C, and keep it at a pressure of 100mbar for 30 minute...

Embodiment 3

[0030] Embodiment 3, the implementation steps are as follows:

[0031] In step 1, the substrate is etched with KOH, the etching temperature is 490° C., and the etching time is 15 minutes.

[0032] Step 2: Clean the etched substrate surface with ethanol for the first cleaning to remove organic matter; use HF to clean the etched substrate surface for the second time to remove ionic and atomic impurities; use high-purity water Carry out the third surface cleaning to ensure that the substrate surface is clean, and finally dry the surface moisture.

[0033] Step 3, place the cleaned 4H-SiC substrate in the CVD furnace cavity, and vacuumize the furnace so that the pressure in the furnace reaches 10 -7 Pa, raise the temperature in the furnace, and at the same time feed hydrogen with a flow rate of 30l / min, raise the temperature to 1450°C, keep it for 5min, then feed it with a flow rate of 10ml / min propane, raise the temperature to 1590°C, and keep it at a pressure of 90mbar for 45 m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More