Self-aligned T-gate carbon nanotube field effect transistor devices and method for forming the same

A technology of field effect transistors and nanotubes, applied in the field of nanotube field effect transistors, can solve the problems of CNT integrated FET difficulties, large-scale manufacturing of consistent characteristics and uniform characteristics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0009] Detailed description of the preferred embodiment

[0010] The present invention is directed to self-aligned T-gate carbon nanotube (CNT) field effect transistors (FETs) and methods for forming the devices.

[0011] In one or more embodiments described herein, for each description, while nanotubes may be described as layers of carbon nanotubes, it should be understood that the nanotubes may include any type of nanotube, including but not limited to carbon nanotubes. tubes, single-walled nanotubes (SWNTs) and multi-walled nanotubes (MWNTs). Furthermore, each of the various embodiments may also be implemented in any one-dimensional semiconductor device (eg, nanotube, nanowire, etc.) or two-dimensional semiconductor device (eg, graphene-based device, etc.).

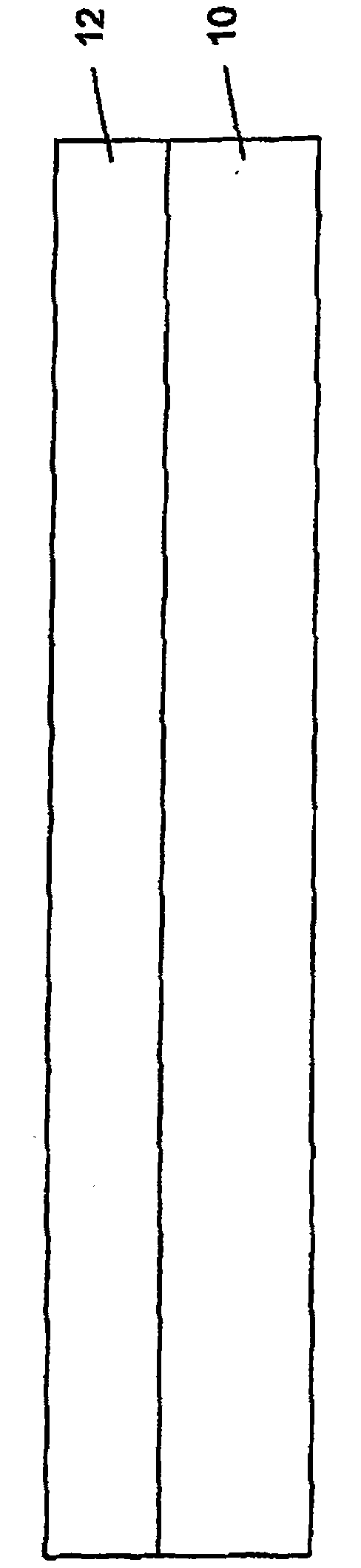

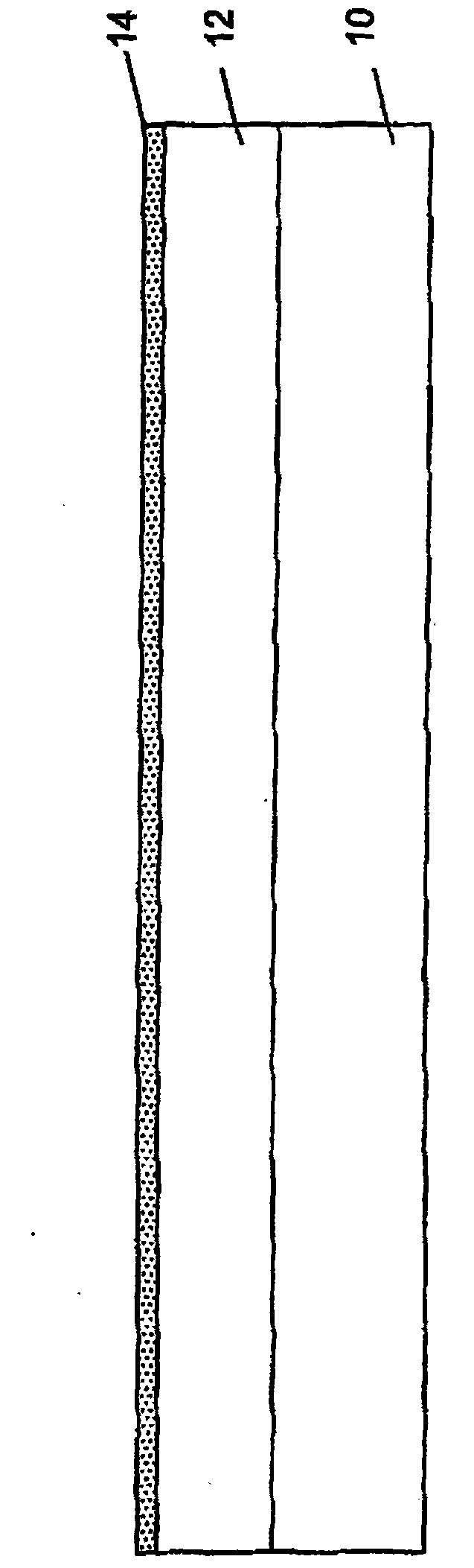

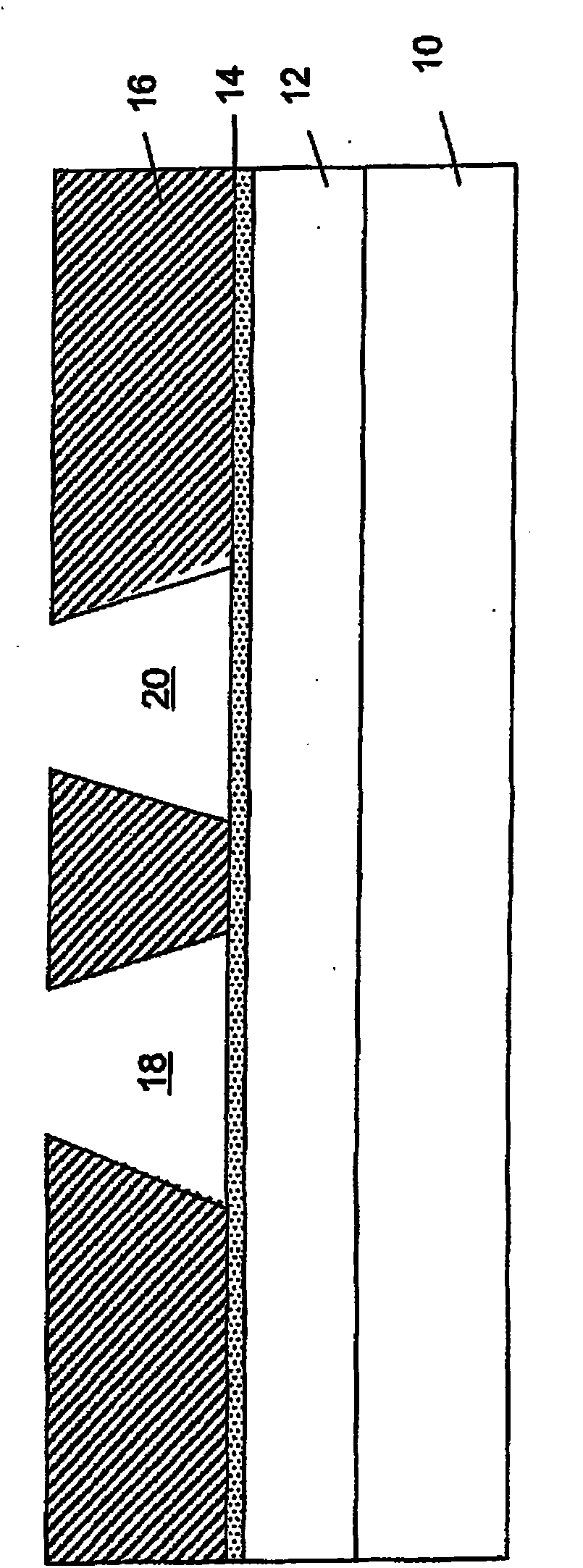

[0012] According to one or more embodiments, a method for forming a self-aligned T-gate carbon nanotube field effect transistor is provided. now refer to Figures 1 to 8 , various process steps for forming a CNT FET...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com