Self-adaption voltage regulator based on optimized PSM modulation mode

A technology of self-adaptive voltage and modulation mode, applied in the direction of control/regulation system, regulation of electrical variables, instruments, etc., can solve the problems of complicated circuit implementation method, compensation loop oscillation phenomenon, time-consuming system error correction, etc., to achieve electromagnetic compatibility The effect of good characteristics, fast response speed and strong anti-interference ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] specific implementation plan

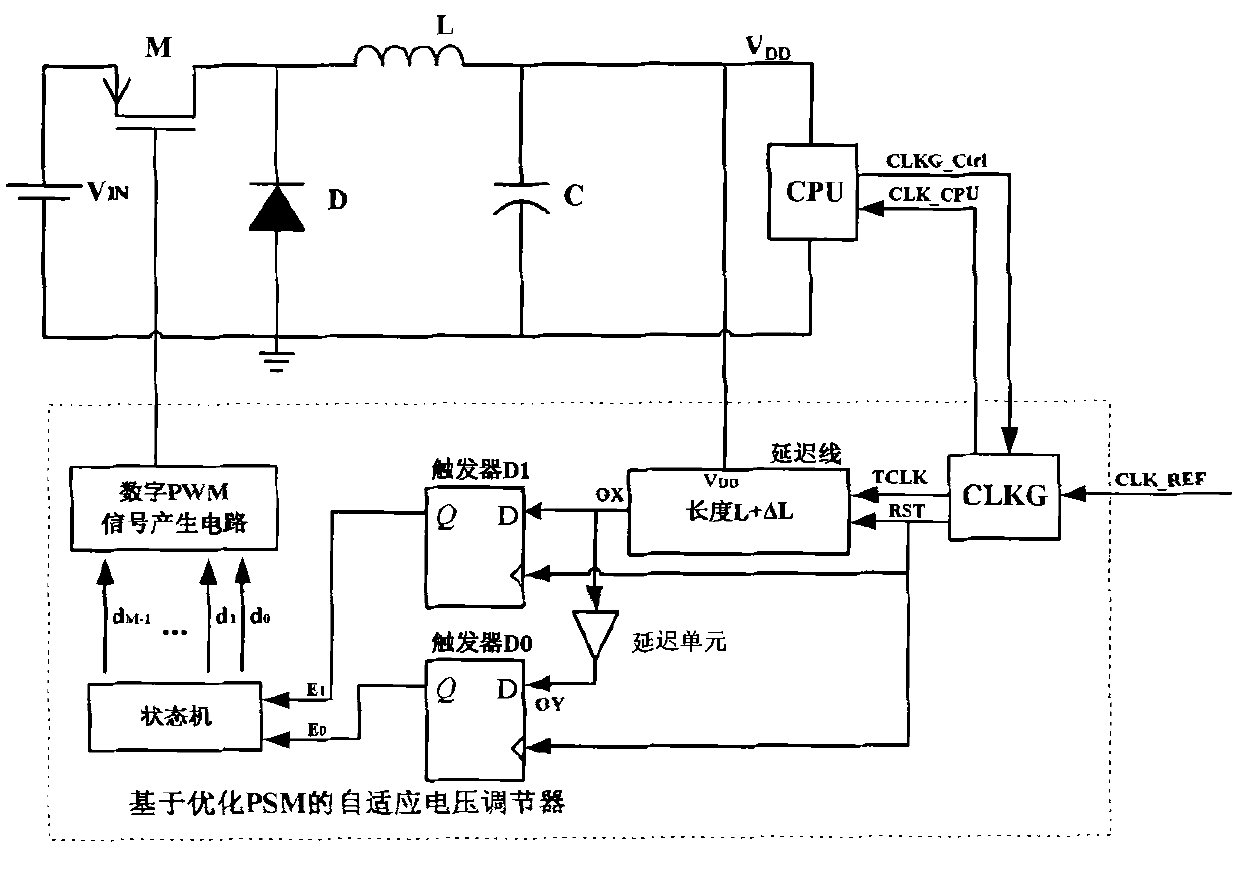

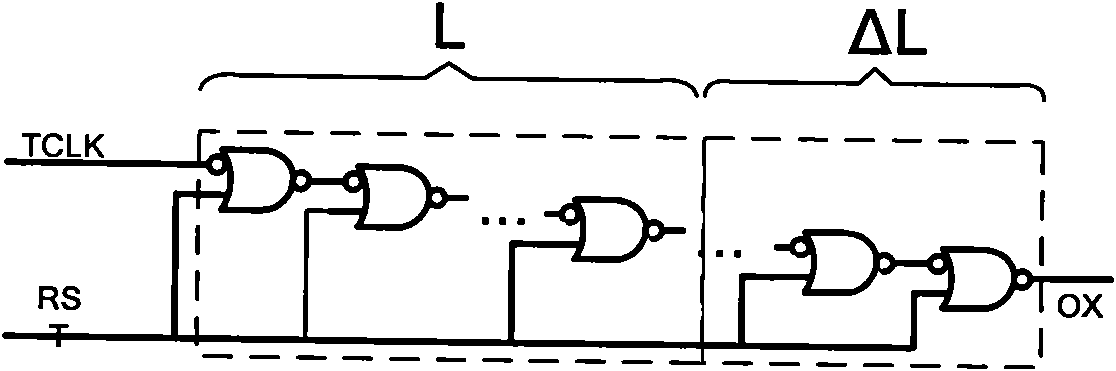

[0025] An adaptive voltage regulator based on an optimized PSM modulation scheme, such as figure 1As shown, it includes a clock signal generator CLKG, a delay line, two flip-flops D0 and D1, a state machine and a digital PWM signal generation circuit. The external clock signal source provides the reference clock signal CLK_REF for the clock signal generator CLKG; the clock signal generator CLKG generates three clock signals according to the control signal CLKG_Ctrl of the operating frequency requested by the external load processor: load processor clock signal CLK_CPU, delay line reset Signal RST and delay test signal TCLK; the delay line reset signal RST and delay test signal TCLK are N frequency division signals of the load processor clock signal CLK_CPU, N is an integer greater than or equal to 2, and the delay line reset signal RST rising edge ratio The rising edge of the delay test signal TCLK lags a clock cycle of the load processor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More