Patents

Literature

152 results about "Delayed Testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

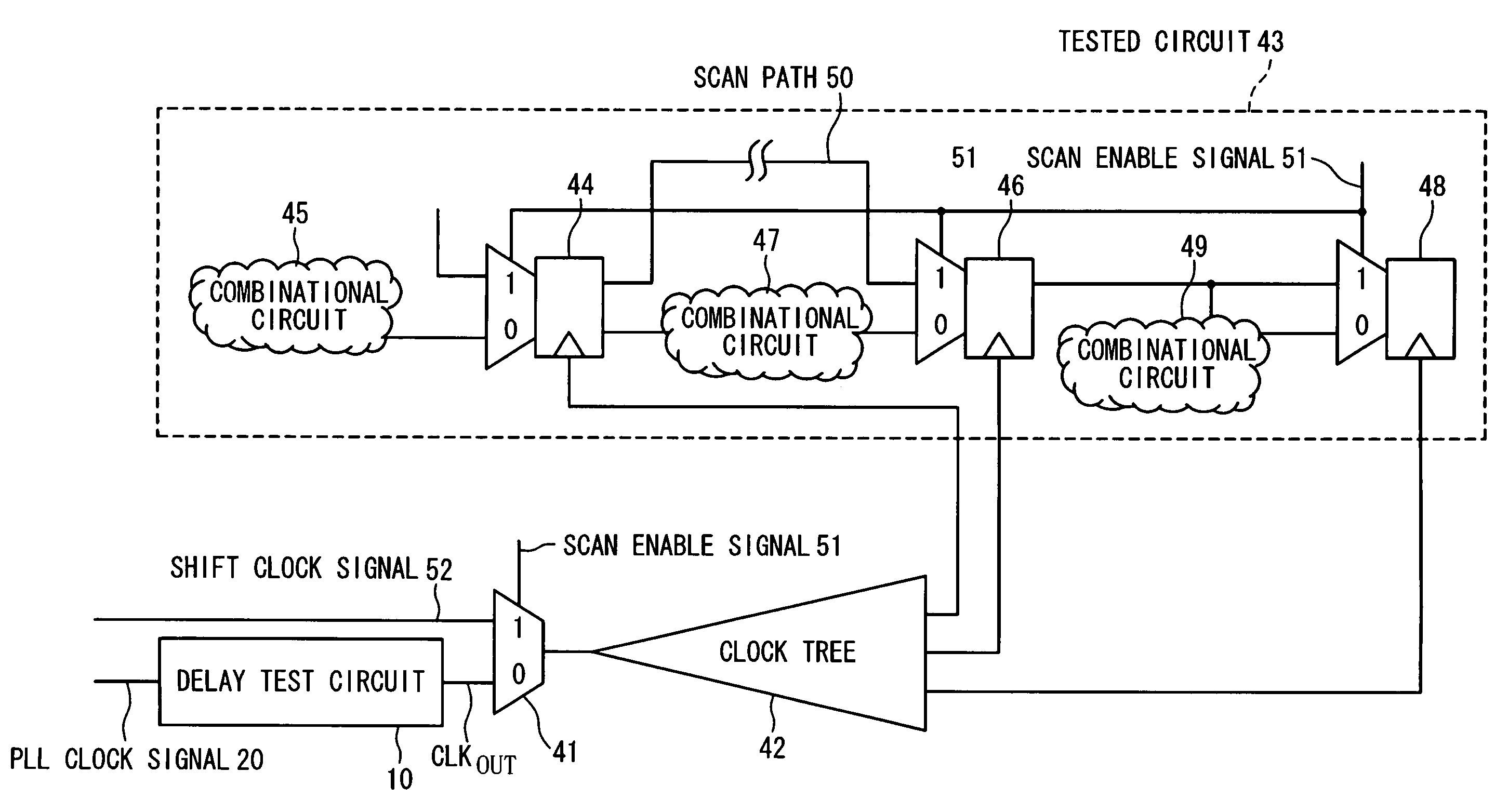

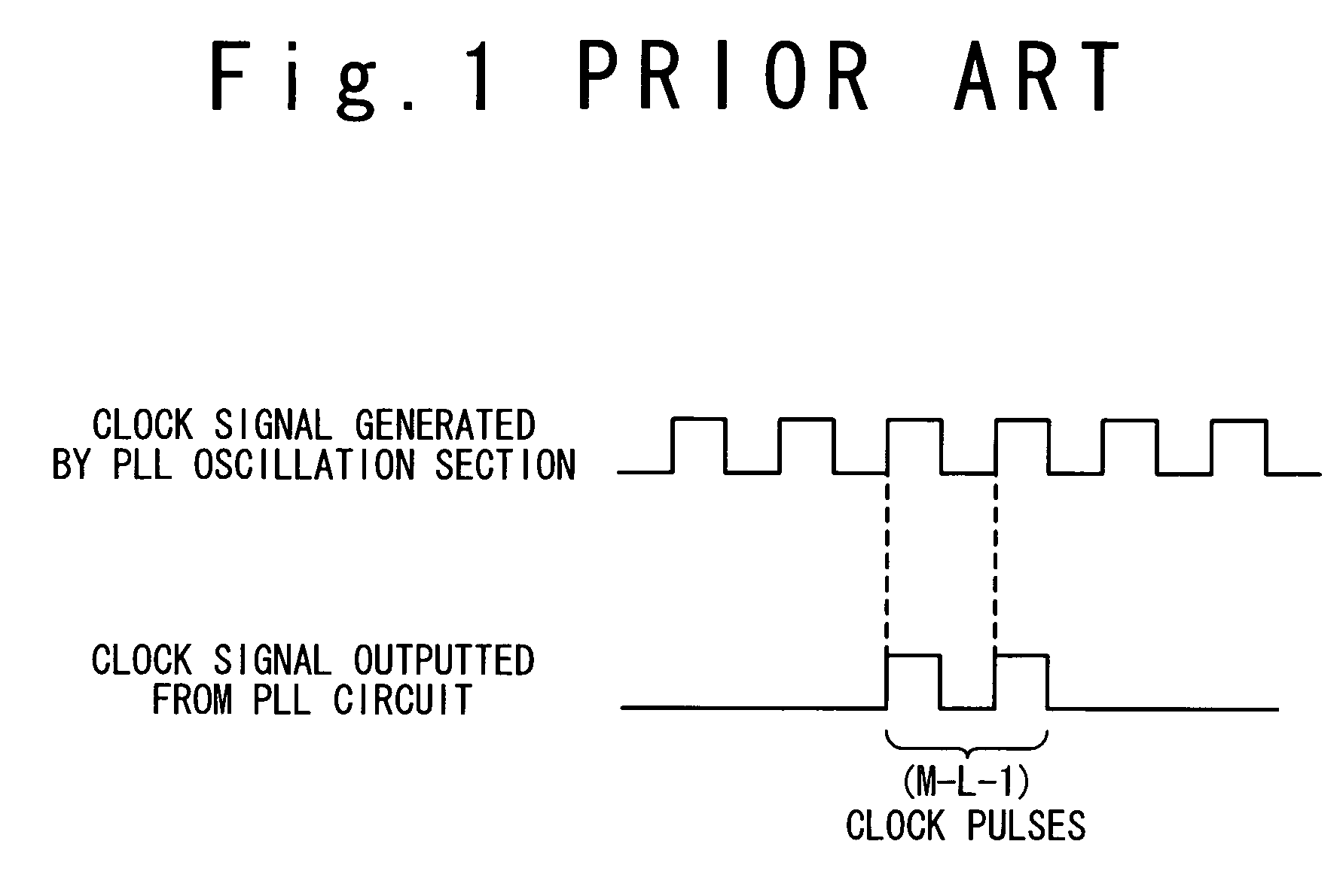

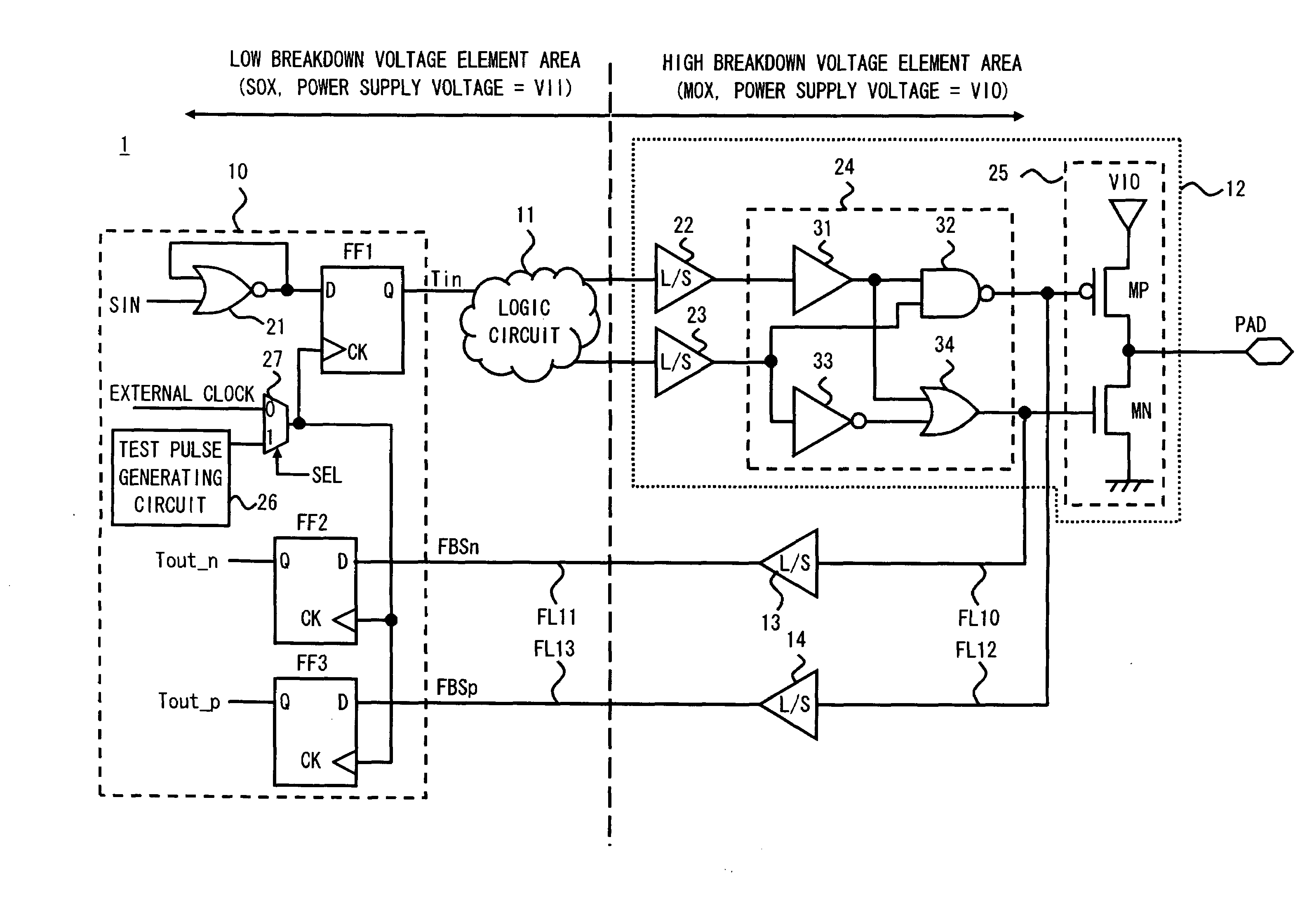

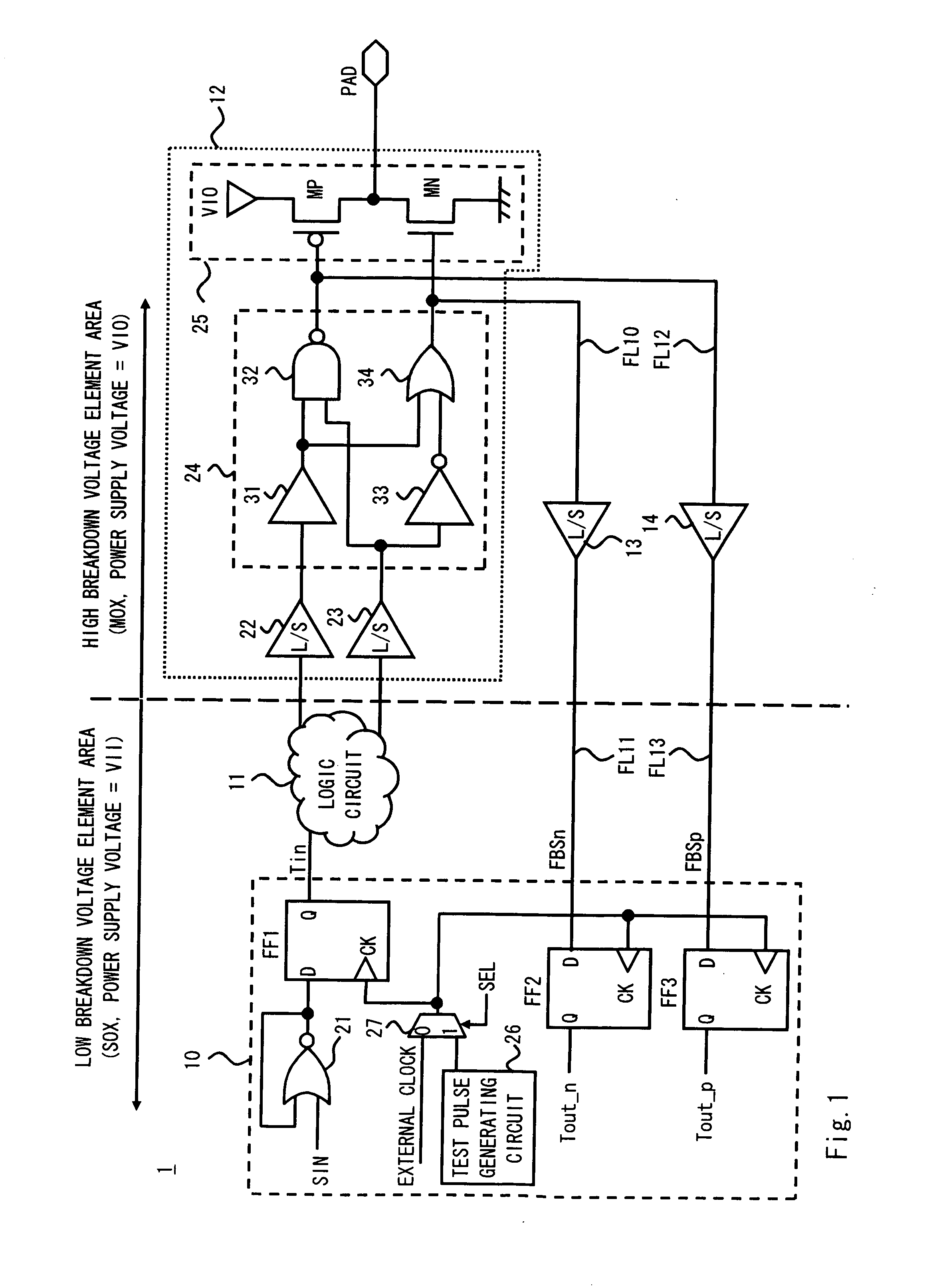

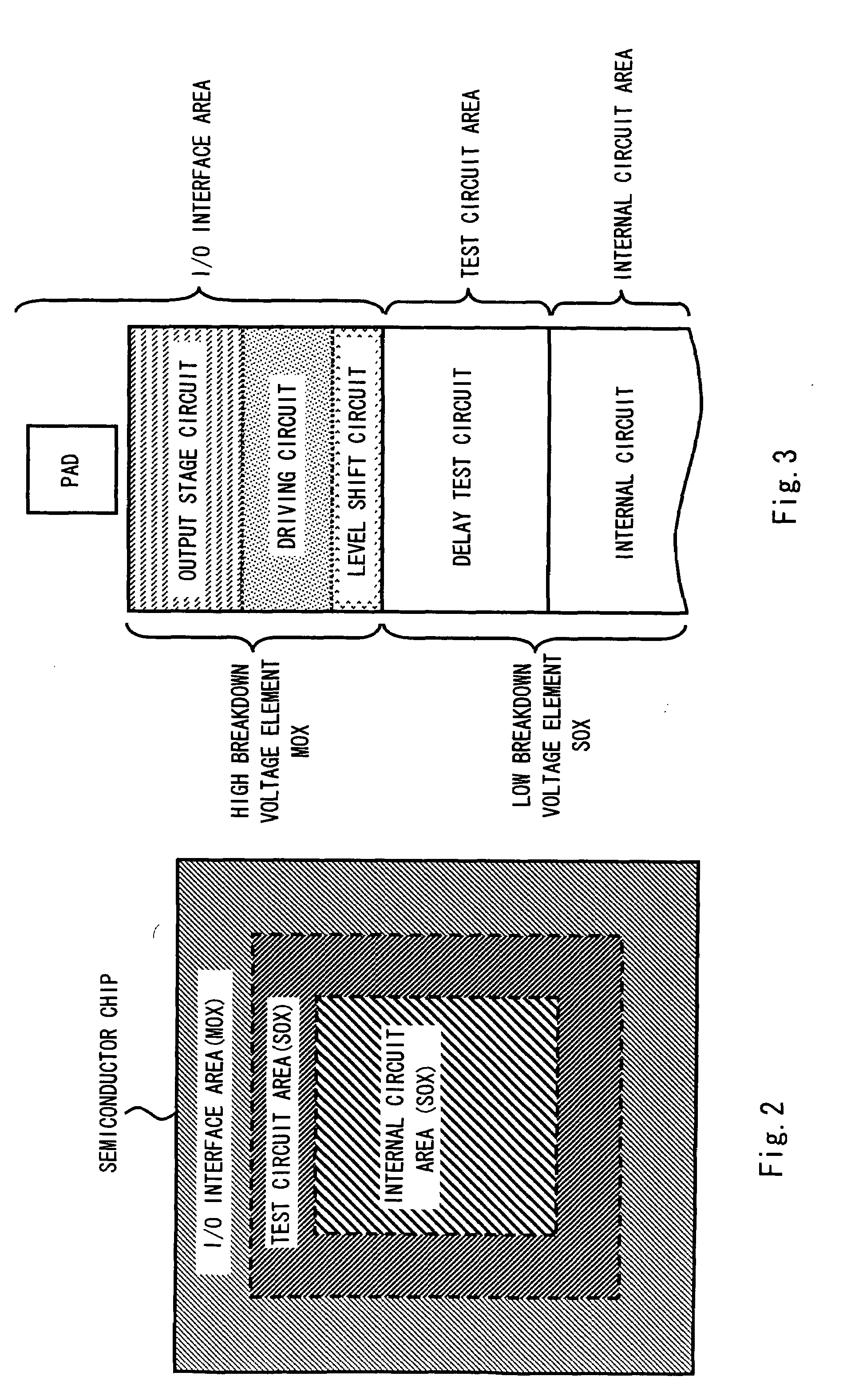

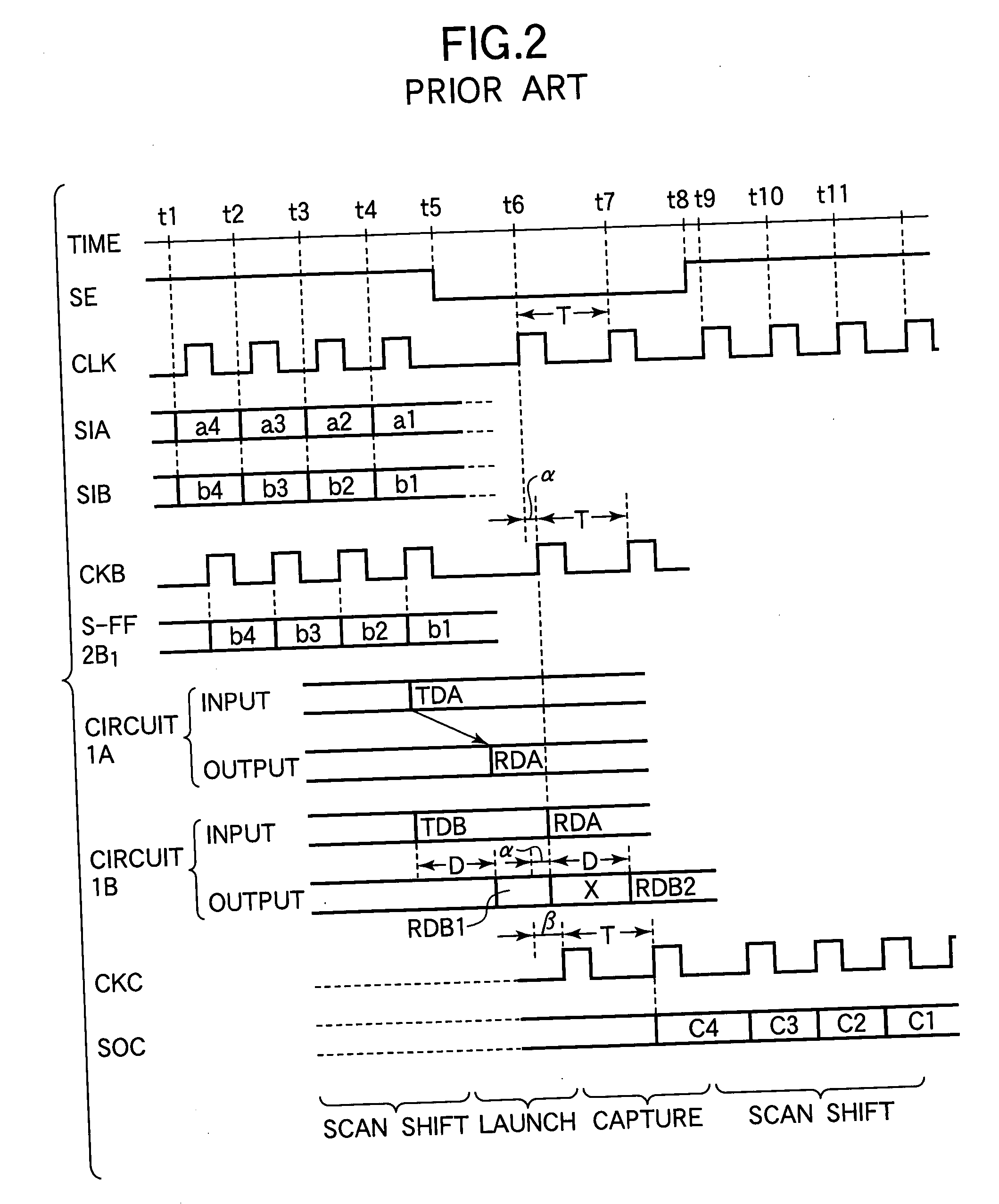

Semiconductor integrated circuit with delay test circuit, and method for testing semiconductor integrated circuit

ActiveUS7613971B2Electronic circuit testingError detection/correctionSemiconductorIntegrated circuit

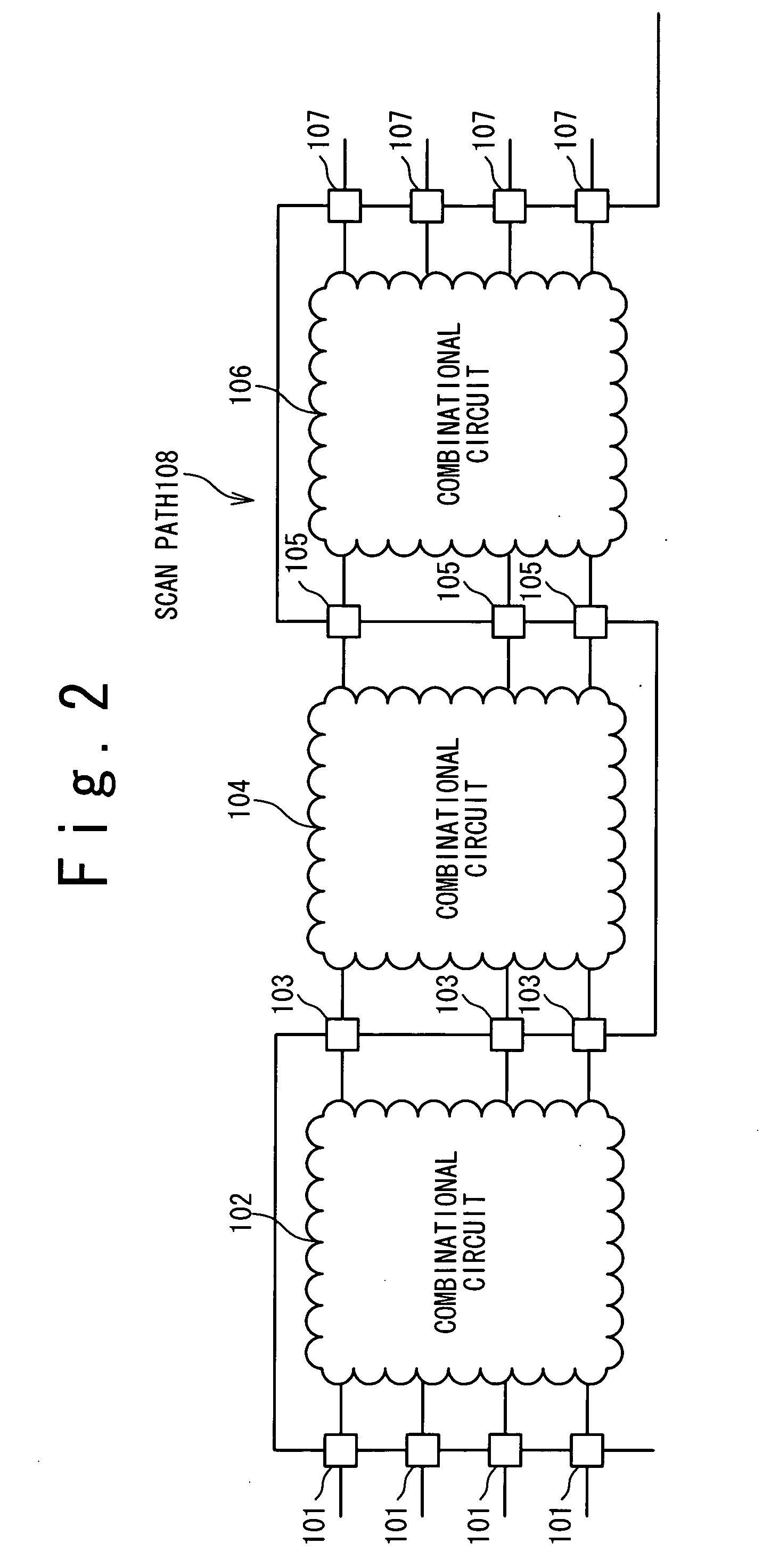

A semiconductor integrated circuit includes an input side flip-flop; a combinational circuit having an input connected with the input side flip-flop; an output side flip-flop connected with an output of the combinational circuit; and a delay test circuit. The delay test circuit generates output clock pulses by removing an optional one from equal to or more than 3 continuing clock pulses of an input clock signal, and supplies the output clock pulse to the input side flip-flop and the output side flip-flop.

Owner:RENESAS ELECTRONICS CORP

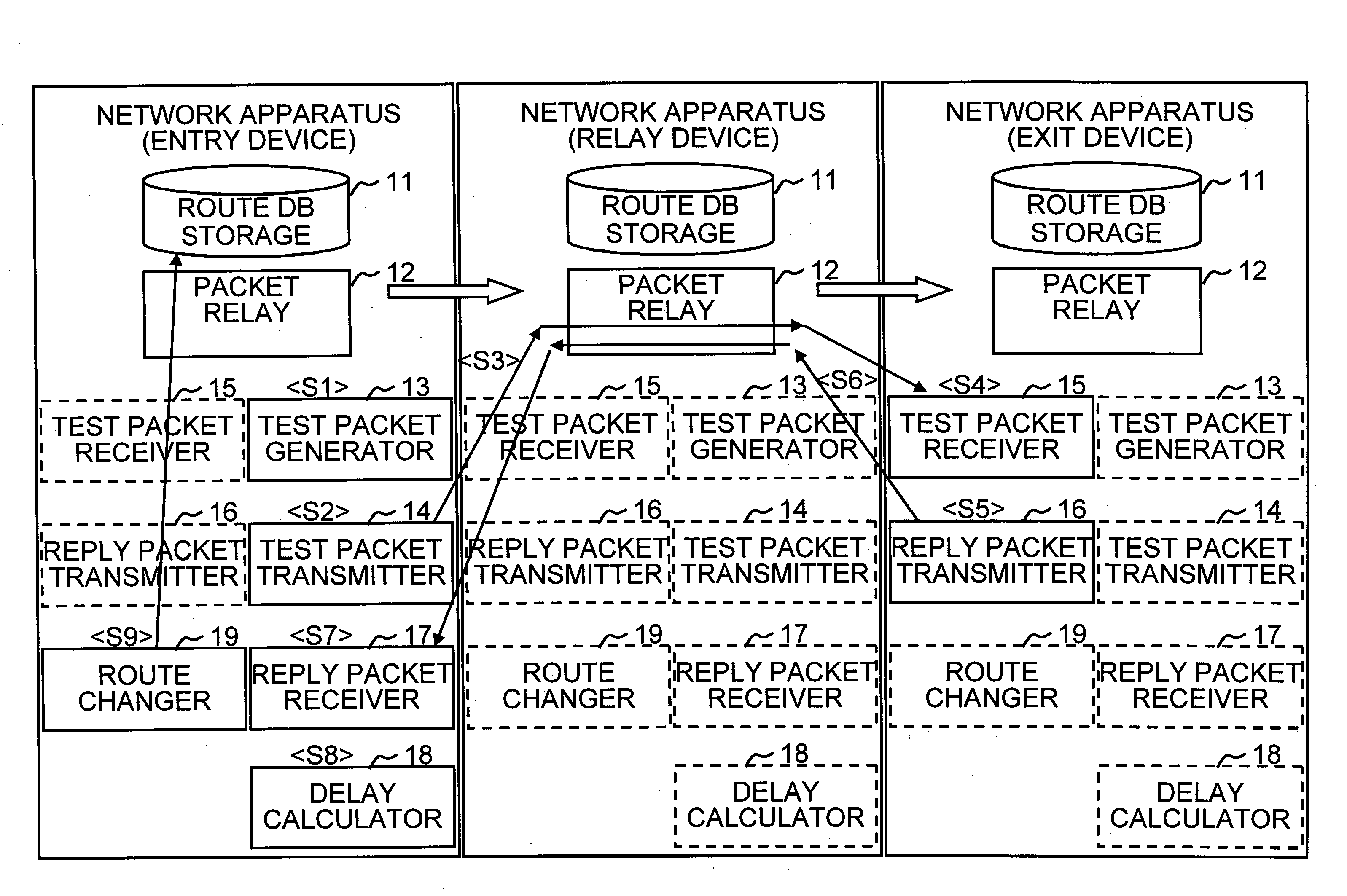

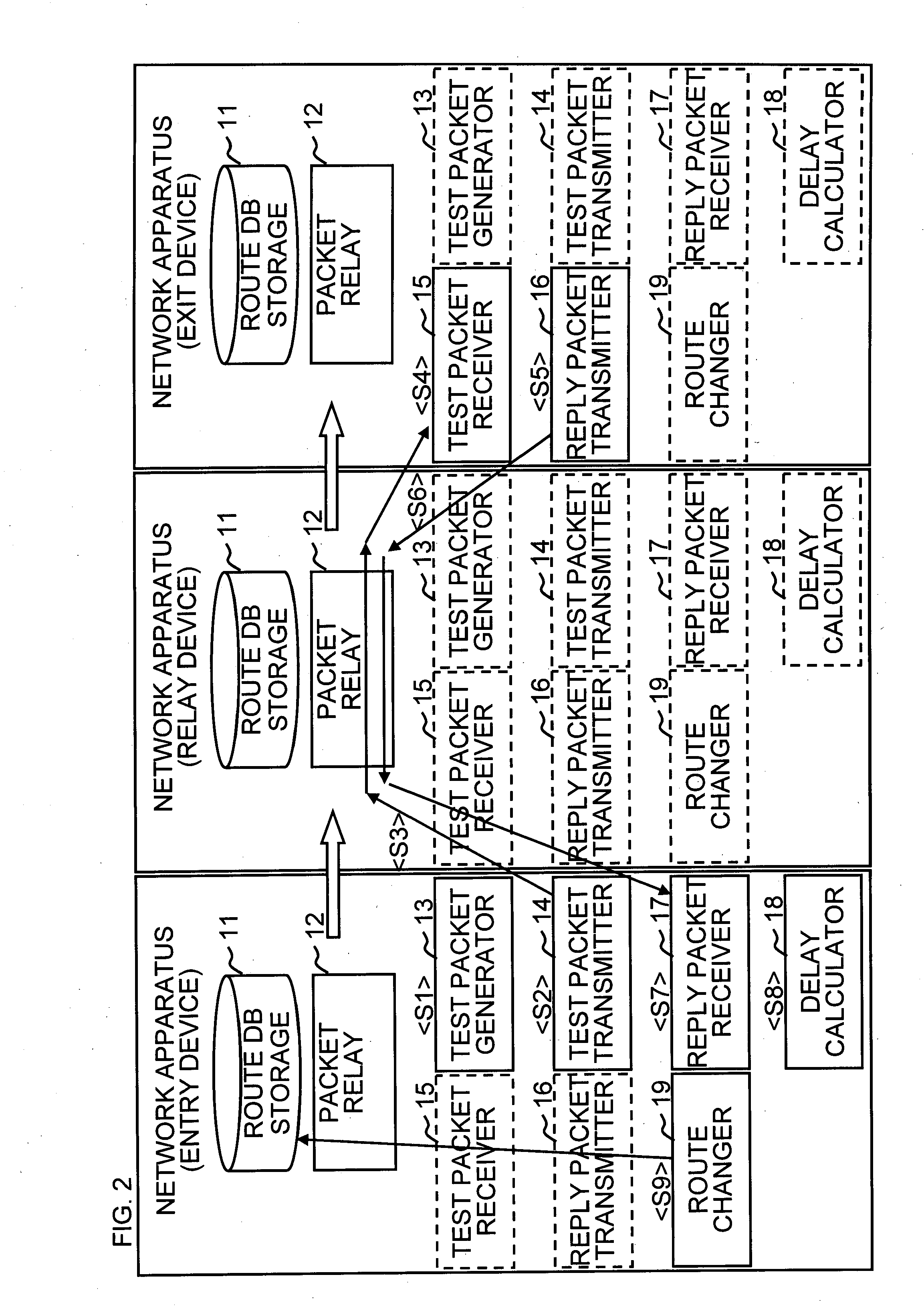

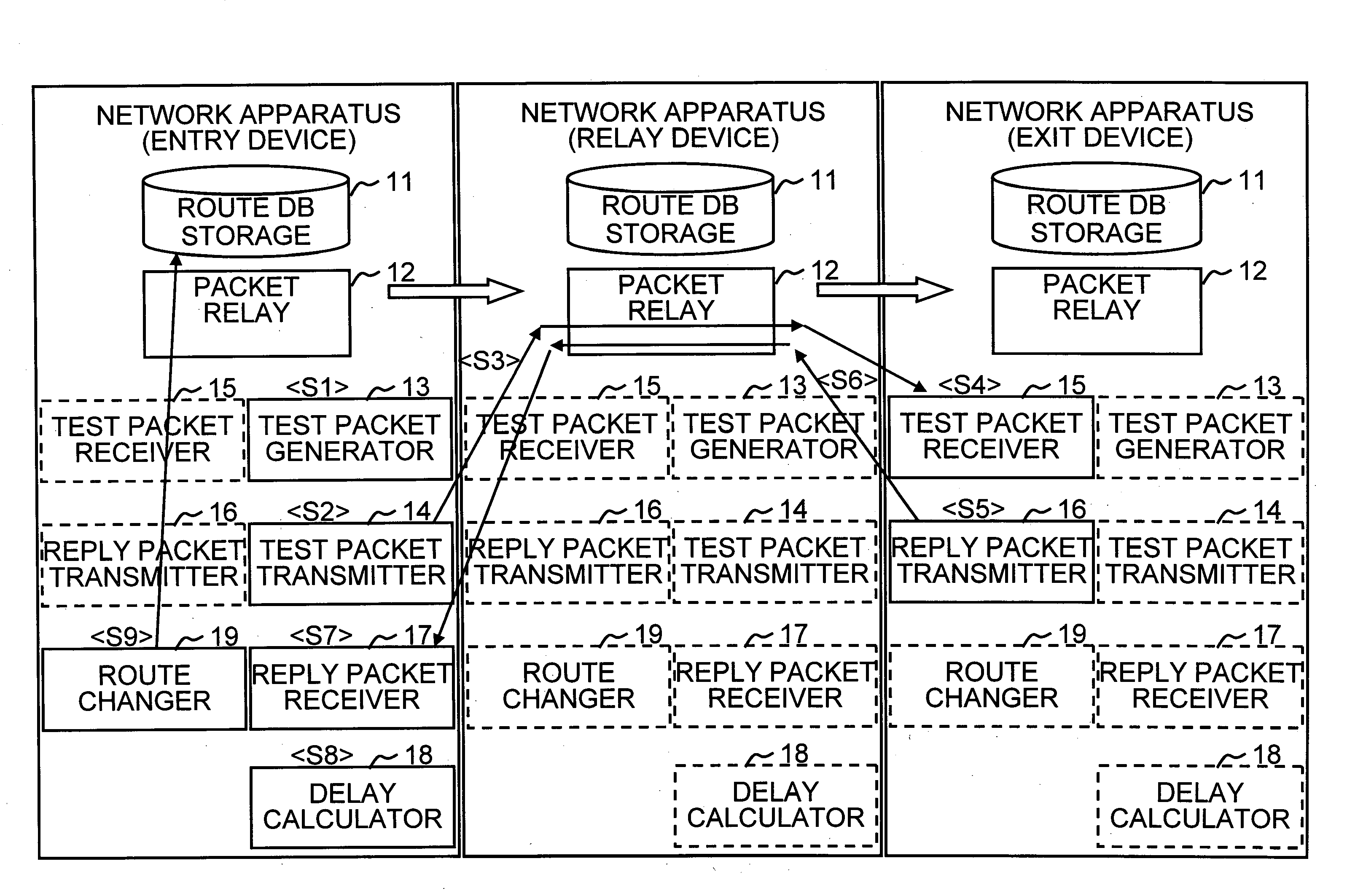

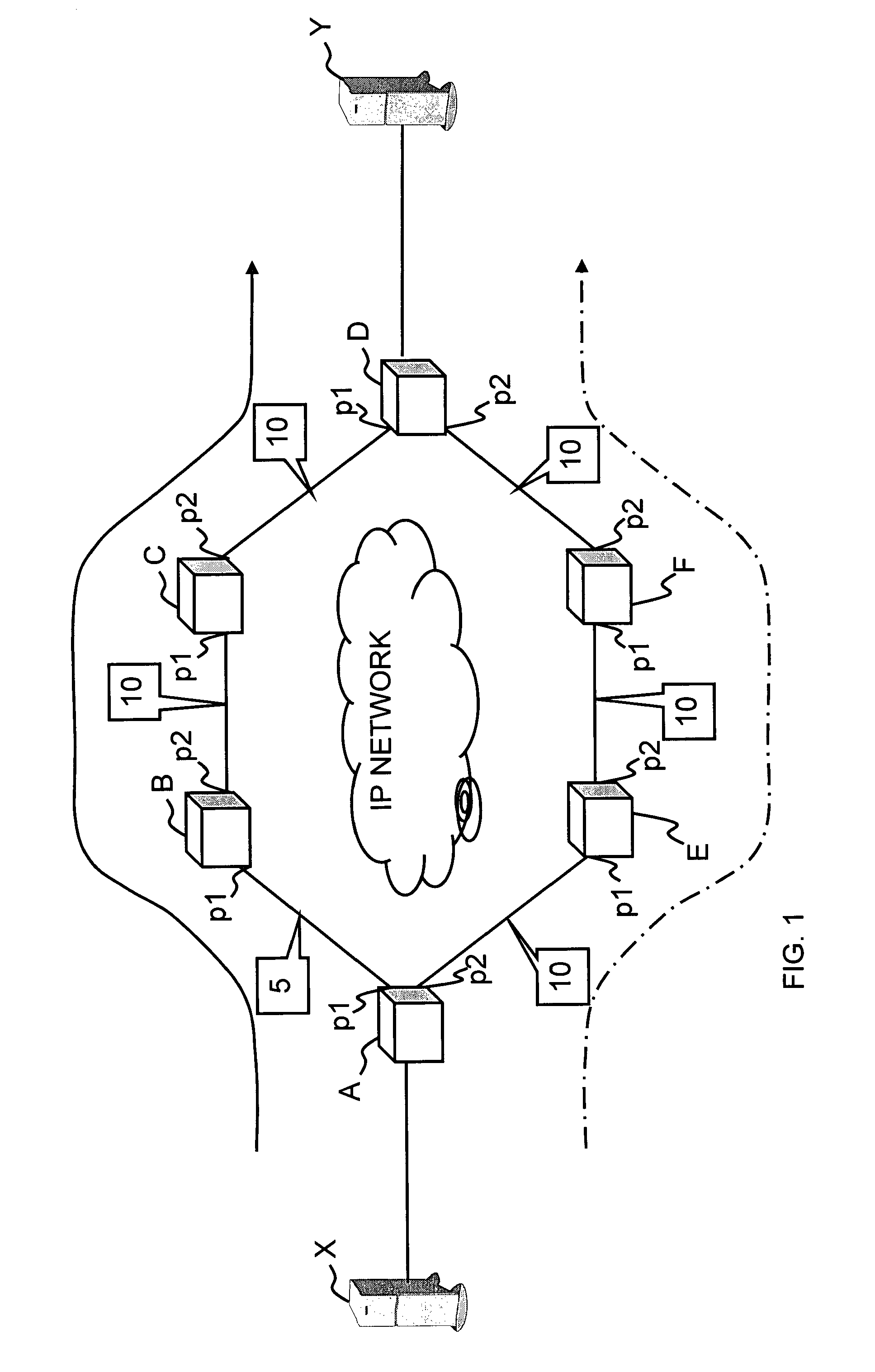

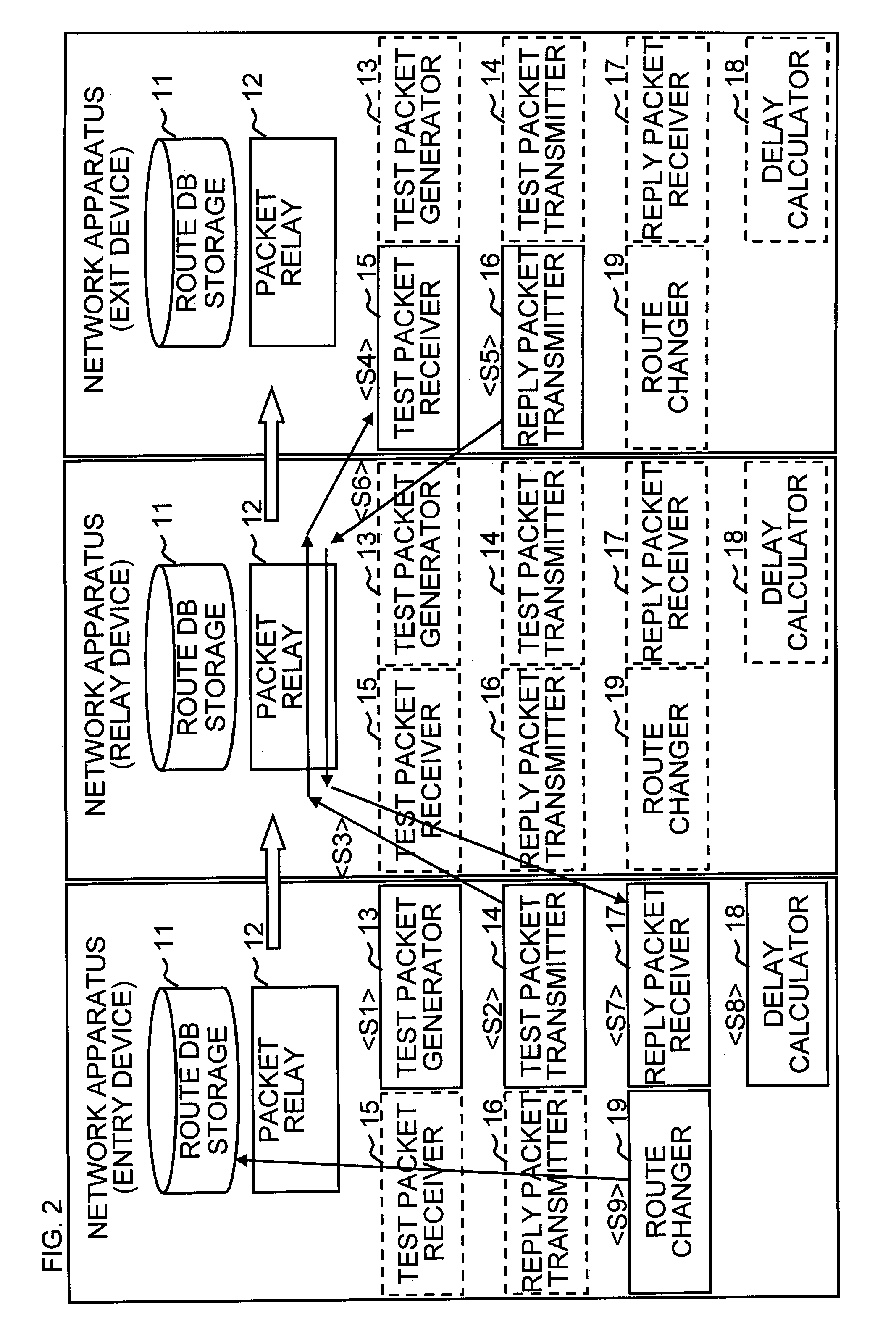

Network system, network apparatus, route change method, and program storage medium storing program thereof

InactiveUS20080117829A1Good serviceError preventionFrequency-division multiplex detailsPacket generatorNetworked system

A test packet generator of an entry device generates a delay test packet including priority information. A test packet transmitter of the entry device transmits the delay test packet to an exit device through a route corresponding to the priority information. A test packet receiver of the exit device receives the delay test packet. A reply packet transmitter of the exit device returns a reply-delay test packet toward the entry device through the same route in the counter direction. A reply packet receiver of the entry device receives the reply-delay test packet. A delay calculator of the entry device calculates a delay time on the basis of the time of transmitting the delay test packet and the time of receiving the reply-delay test packet. A route changer of the entry device changes routing appropriately on the basis of the delay time.

Owner:FUJITSU LTD

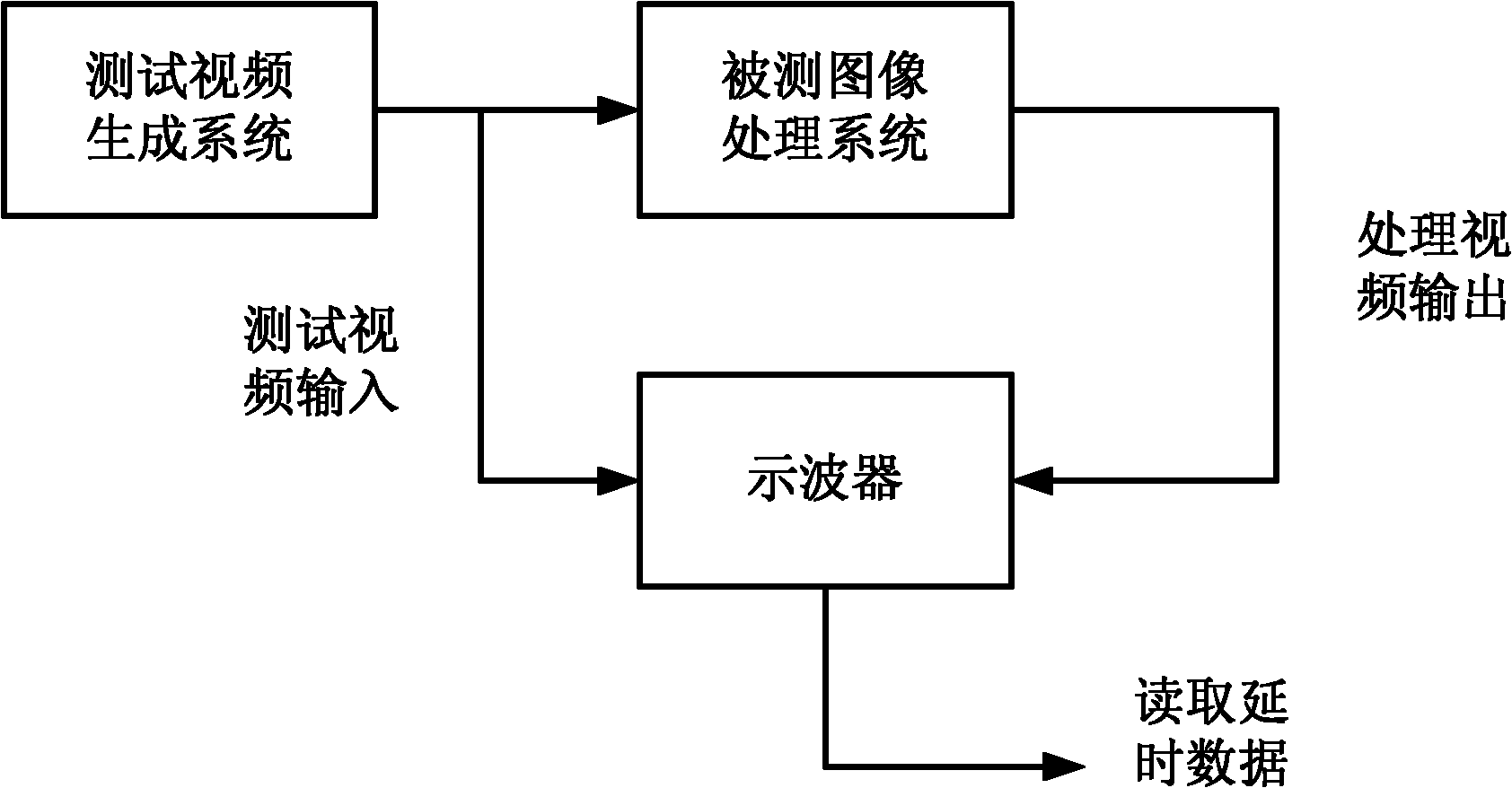

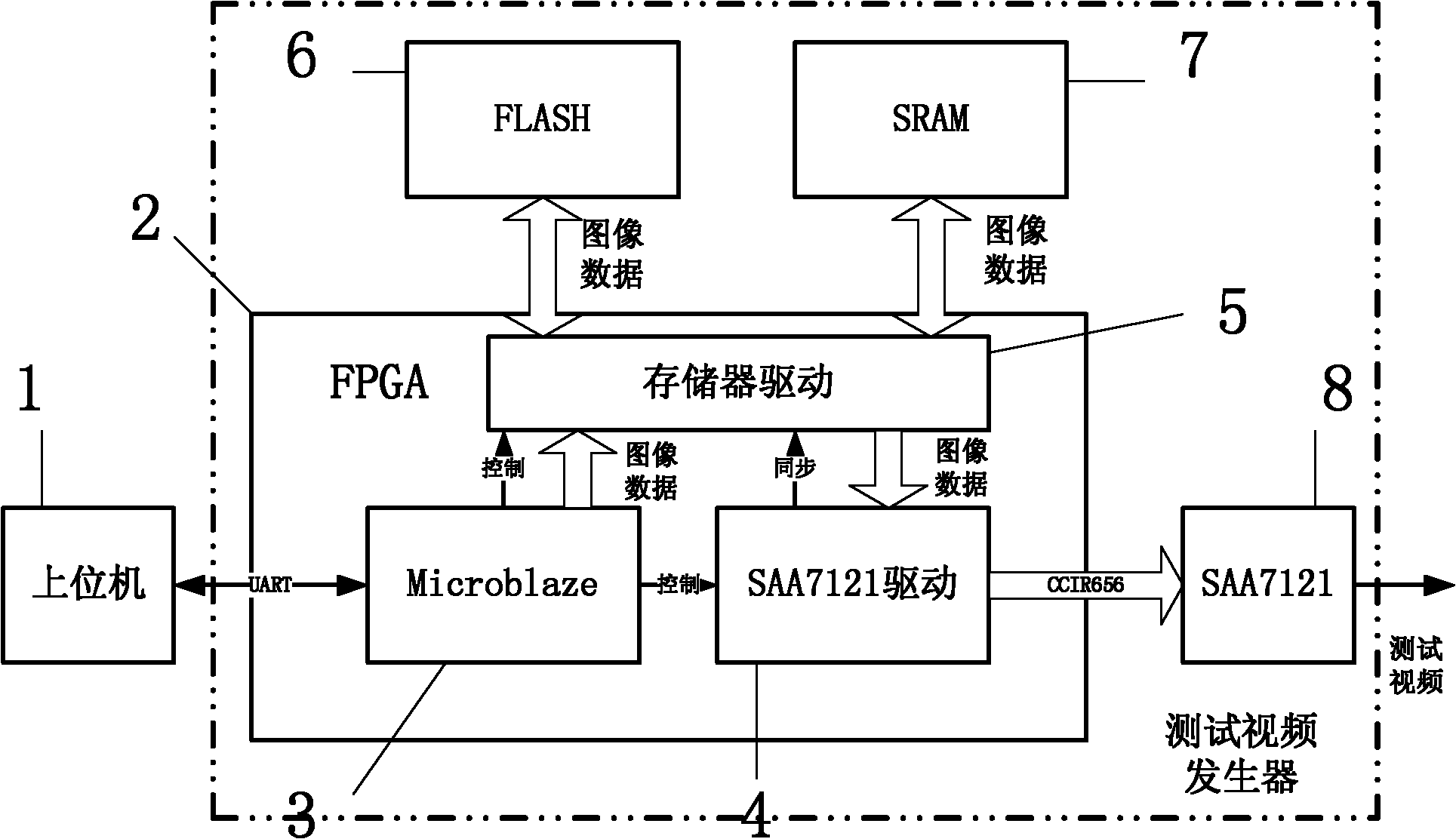

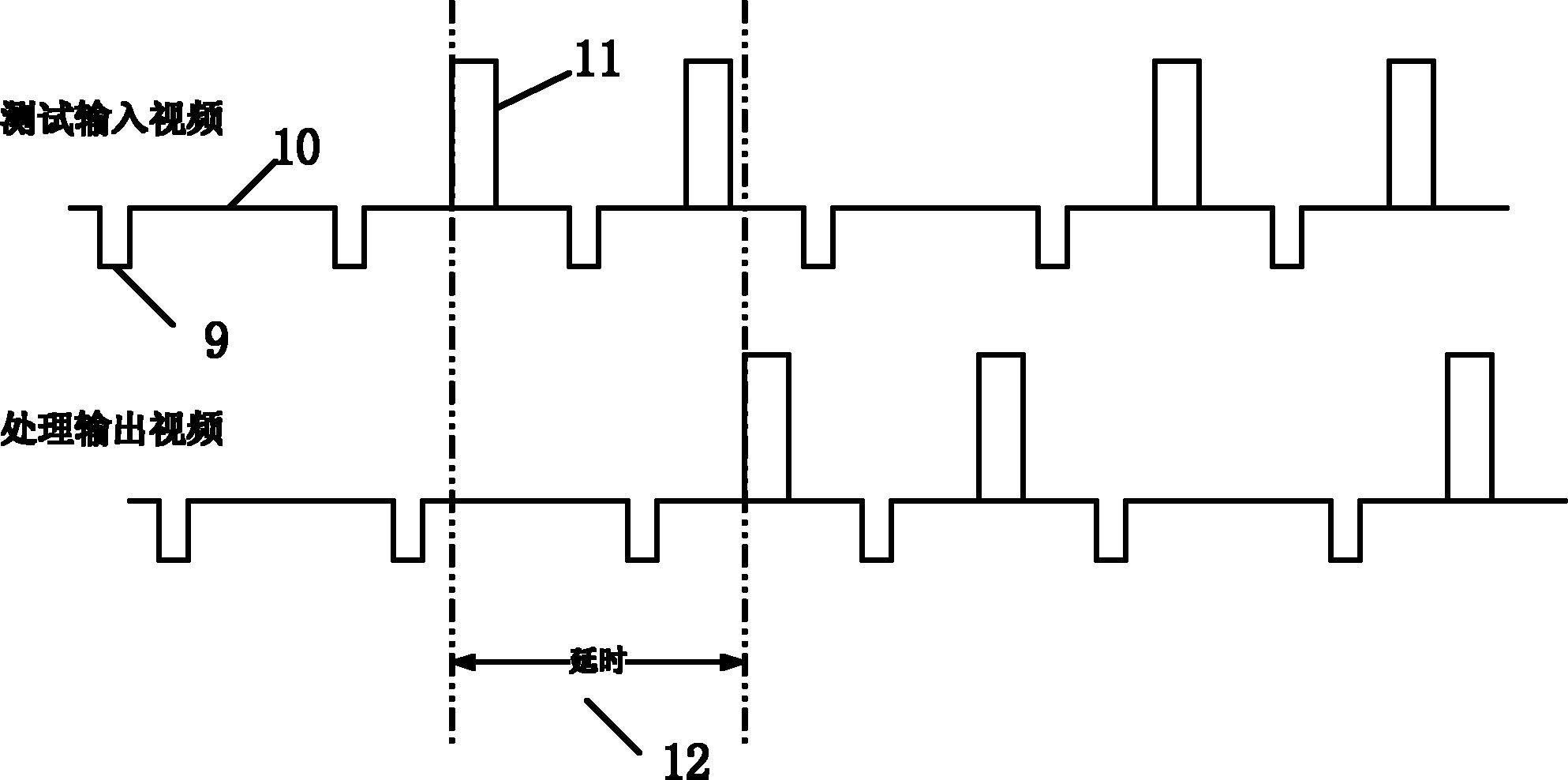

Delay test method for video image processing system

The invention relates to a delay test method for a video image processing system, which comprises the following steps: 1) editing a to-be-tested image by the using of a PC (personal computer), sending the to-be-tested image to a tested video generator, storing the to-be-tested image in a flash by the tested video generator, and standing by; 2) at the moment of testing, selecting the to-be-tested image by an upper computer according to a video standard of tested system and testing the specific sequence form and video format; 3) sending a to-be-tested video into the tested system; and 4) sending the to-be-tested video generated from the step 2) and the video outputted by the tested system to an oscilloscope or logic analysis meter, and reading the time difference of input and output, namely acquiring the system delayed volume. The tested images in the tested video are continuously outputted at intervals. The invention provides a simple, direct and practical method, which can be used for accurately testing the delay of the video image processing system.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

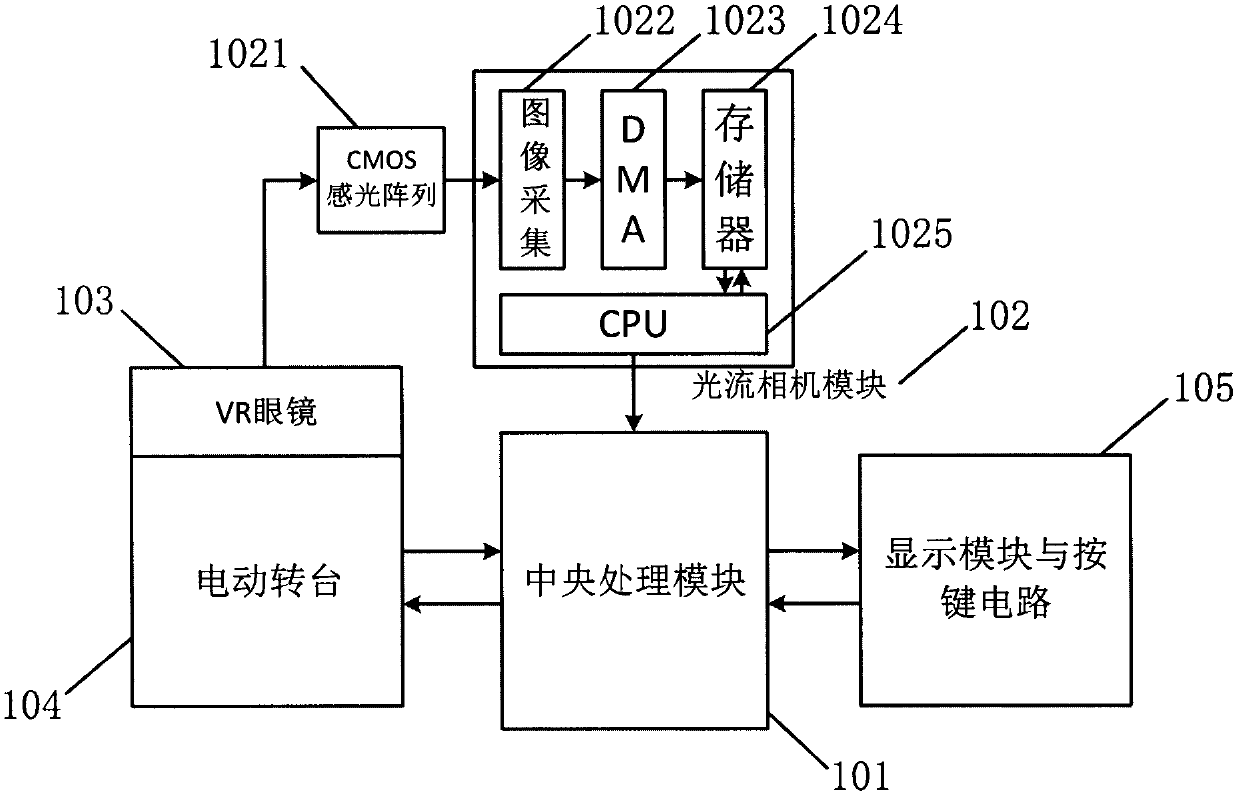

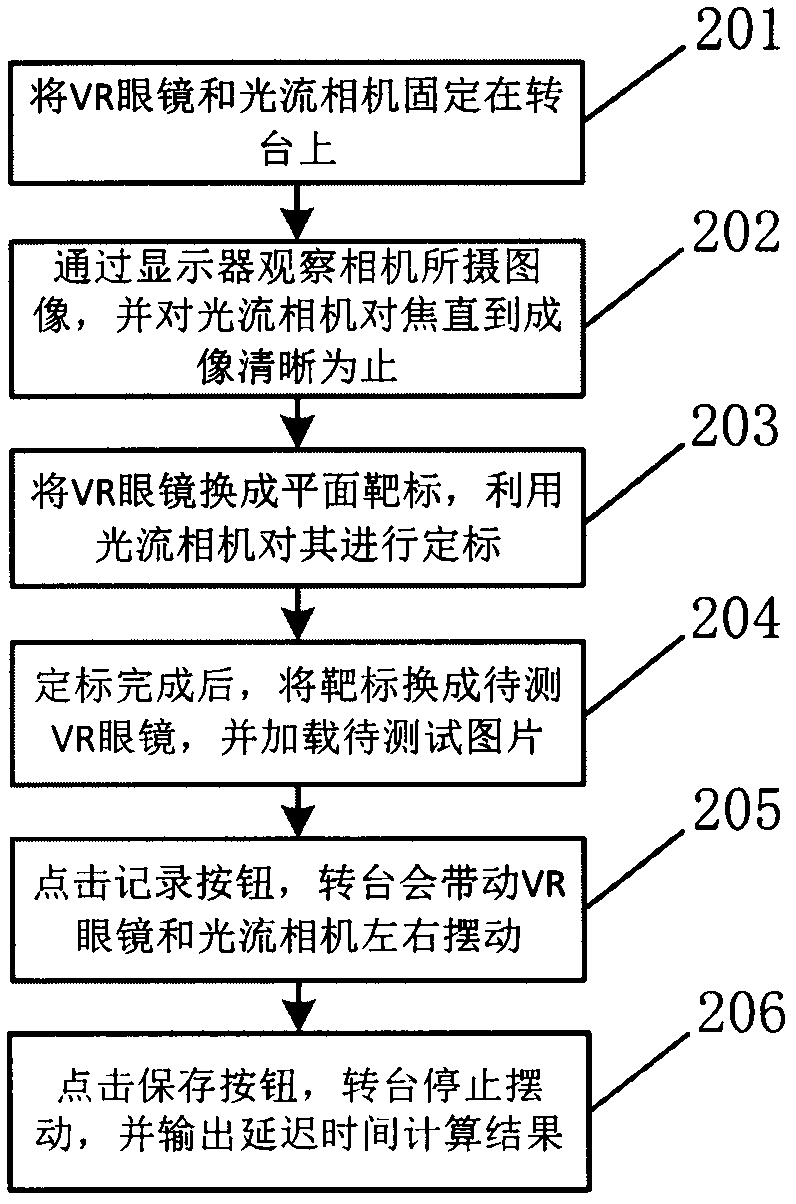

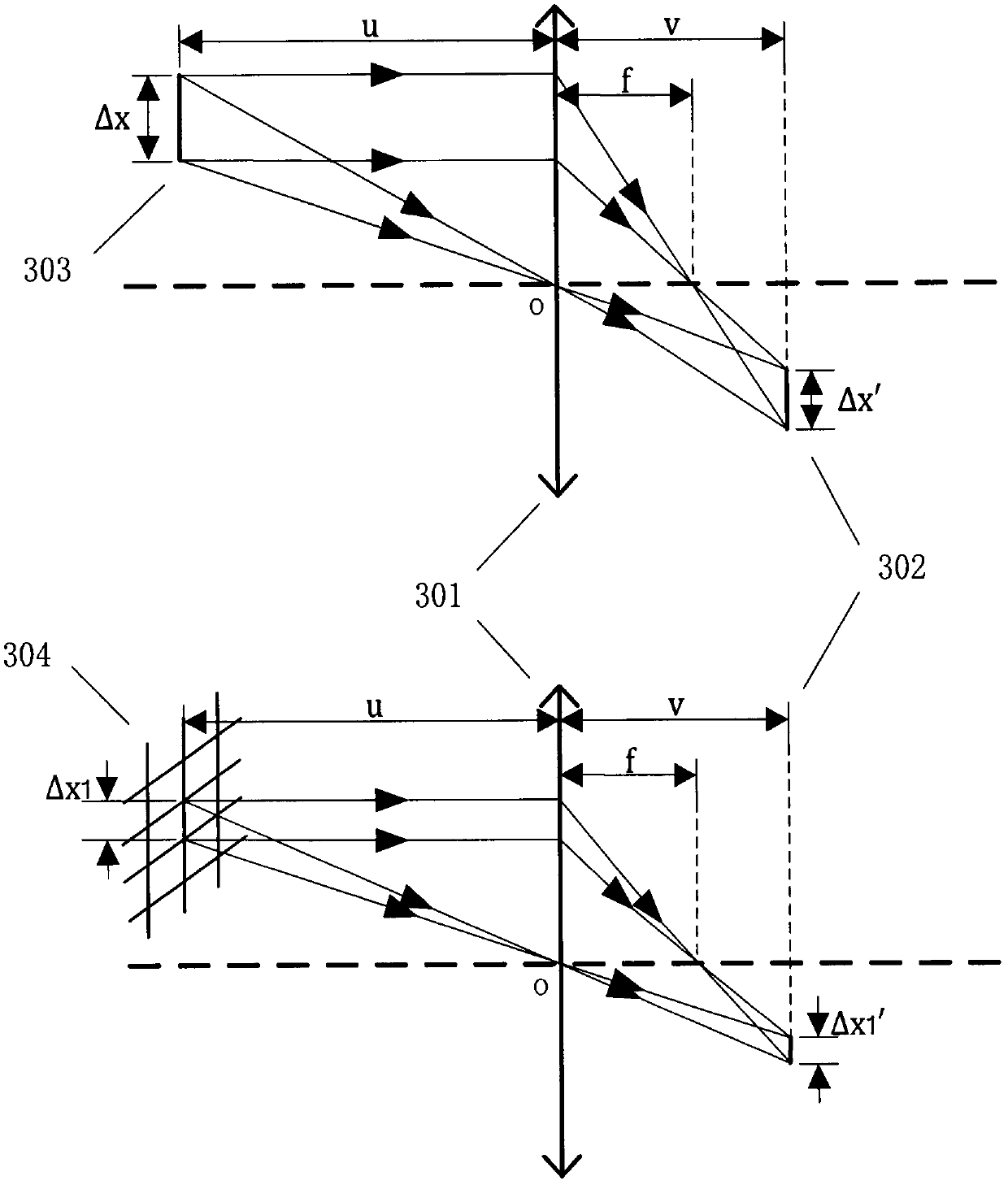

VR (Virtual Reality) equipment delay test device based on optical flow camera

InactiveCN107820075AImprove measurement accuracyNo added complexityTelevision system detailsColor television detailsComputer moduleSimulation

The invention provides a VR (Virtual Reality) equipment delay test device based on an optical flow camera, which is used for measuring the delay time between user action input and the display screen switching. The device comprises an optical flow camera module, a motorized turntable, a central processing module, a display module and VR glasses; the optical flow camera module is used for acquiringdisplacement information of a display picture of the VR glasses; the motorized turntable is used for simulating user action output; and the central processing module determines the delay time according to the displacement information and swing information of the turntable, and the display module displays the final delay result. The VR equipment delay test device based on the optical flow camera provided by the invention is characterized in that displacement is measured by utilizing the optical flow camera, and the delay time of the VR glasses is obtained according to a delay time calculation algorithm; and besides, the device can be used for the delay test of VR products.

Owner:CHINA JILIANG UNIV

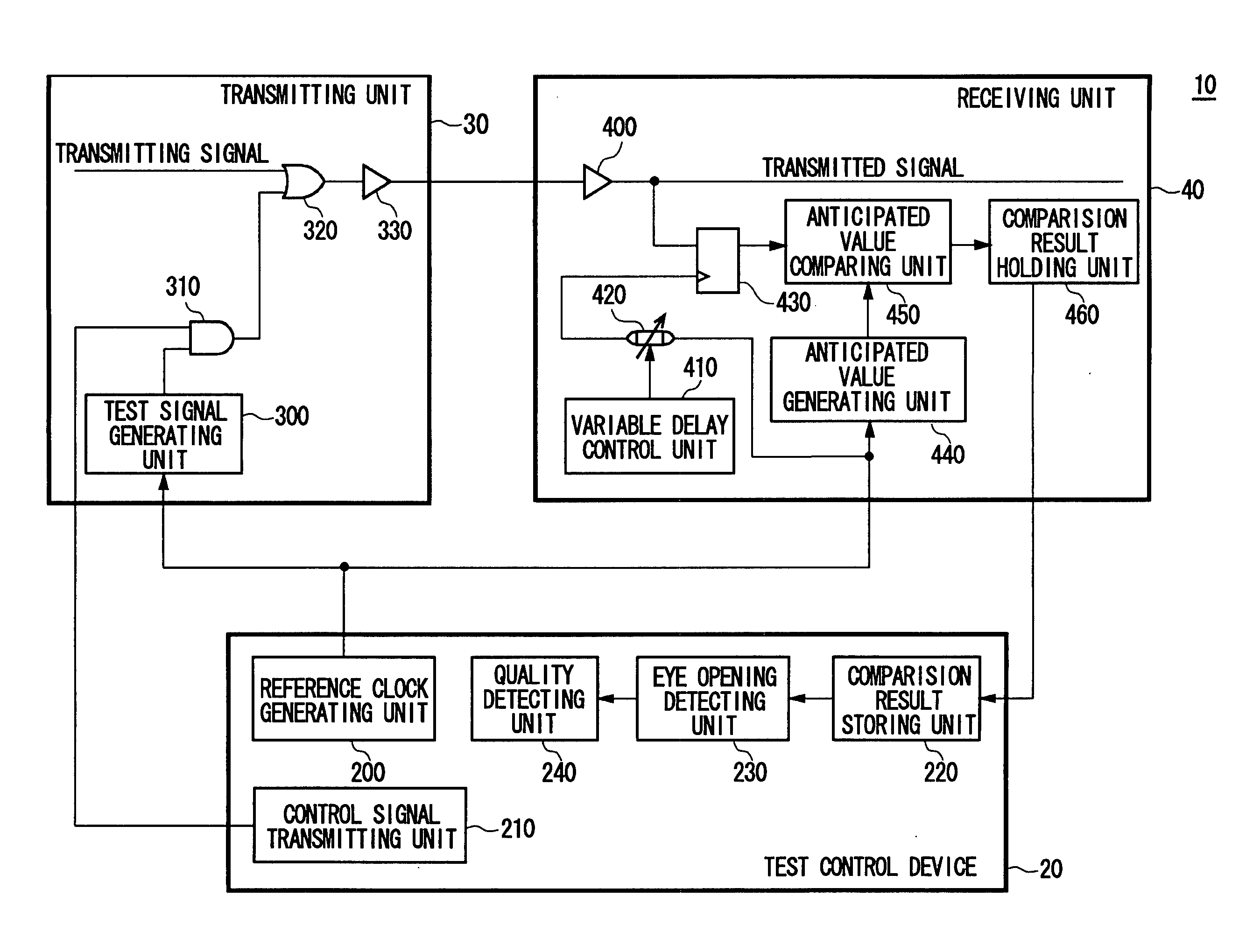

Testing method, communication device, and testing system

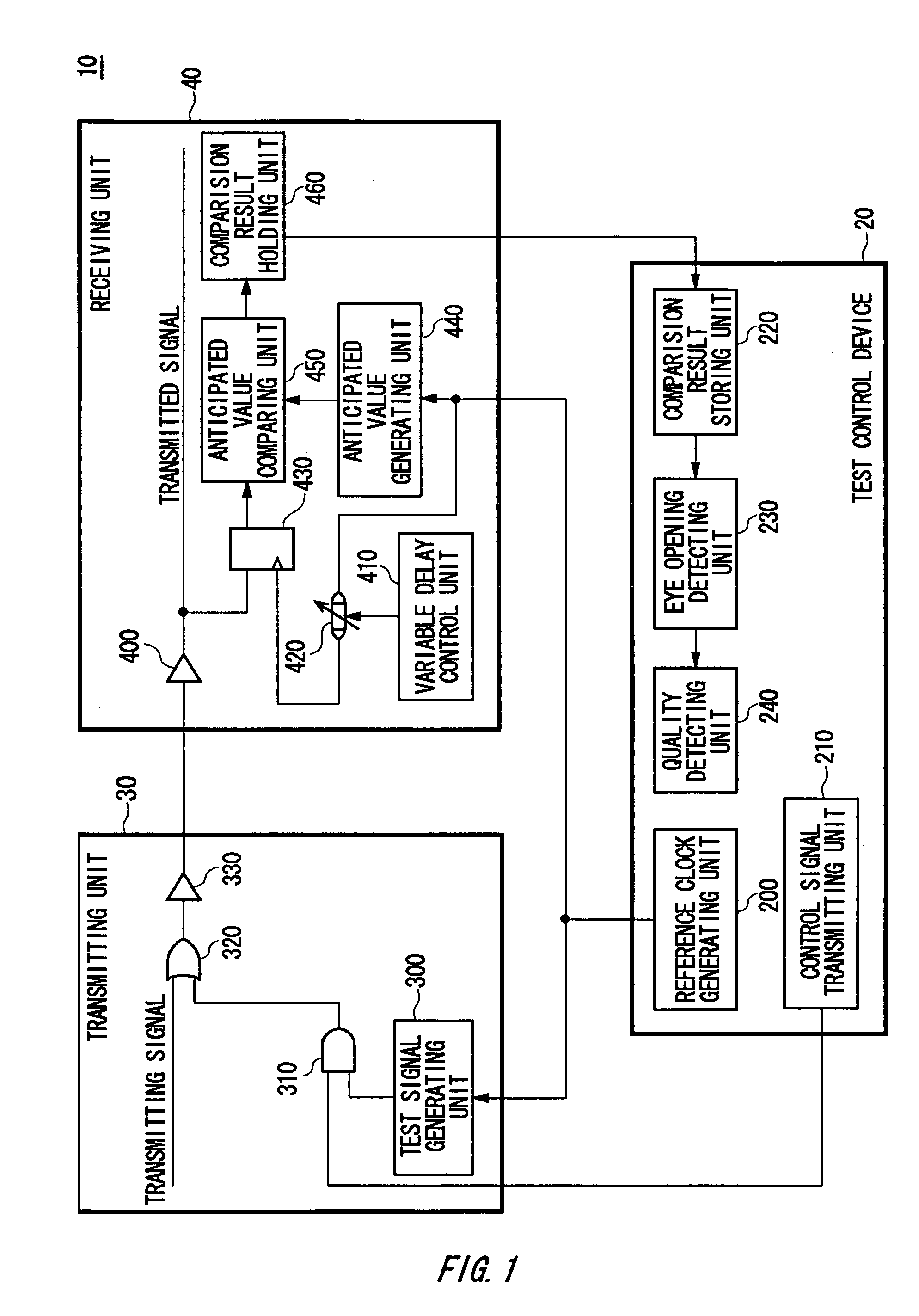

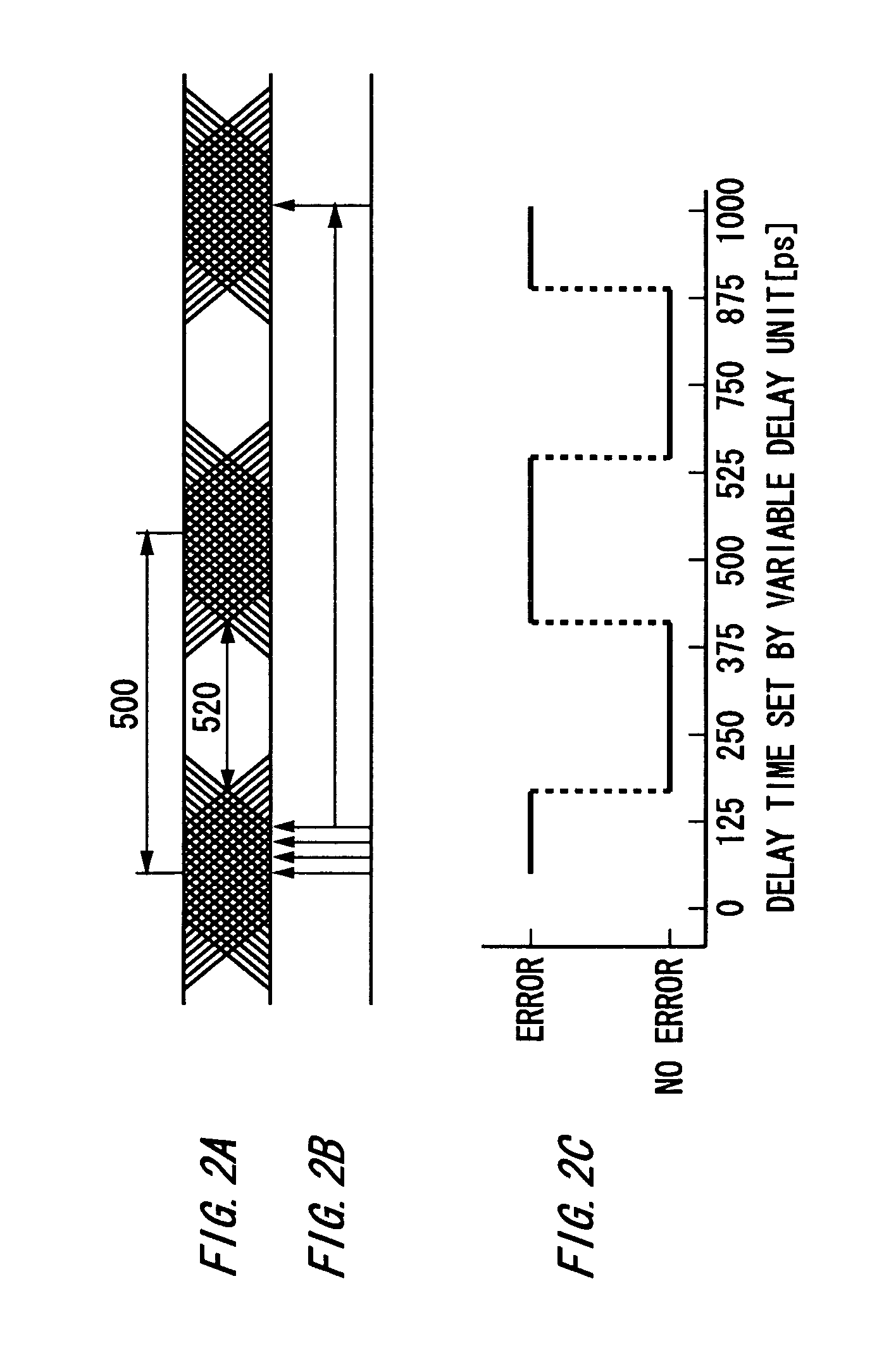

ActiveUS20060209710A1Correct operation testingTransmission systemsComputer scienceCommunication device

A testing method of a communication device according to the present invention comprises: a step for transmitting and receiving a test signal generated based on a reference clock; a step for generating an anticipated value of the test signal based on the reference clock; a step for delaying the test signal; a step for comparing the delay test signal with the anticipated value and outputting the comparison results; a step for repeatedly performing the above steps and storing the comparison results for each delay time; a step for detecting the eye opening for the test signal based on the comparison results for each delay time; and a step for determining the quality of the communication device based on the detected eye opening.

Owner:ADVANTEST CORP

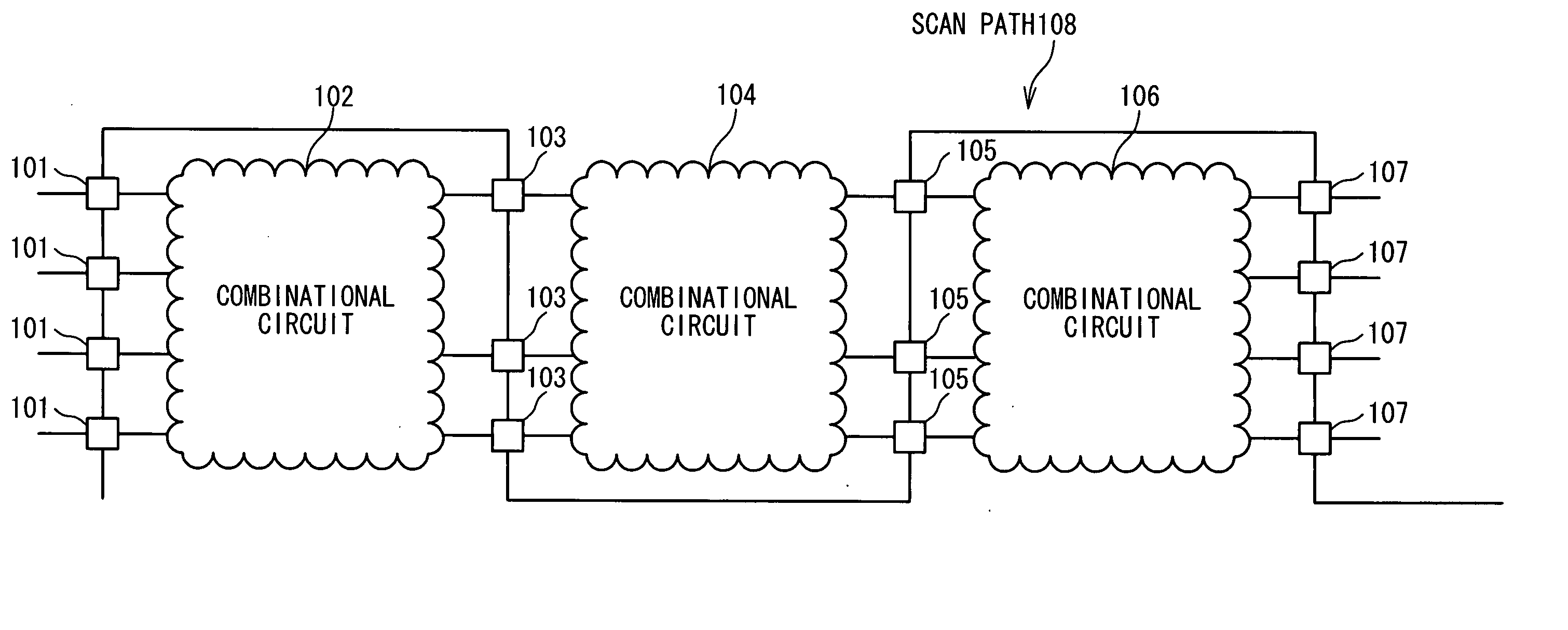

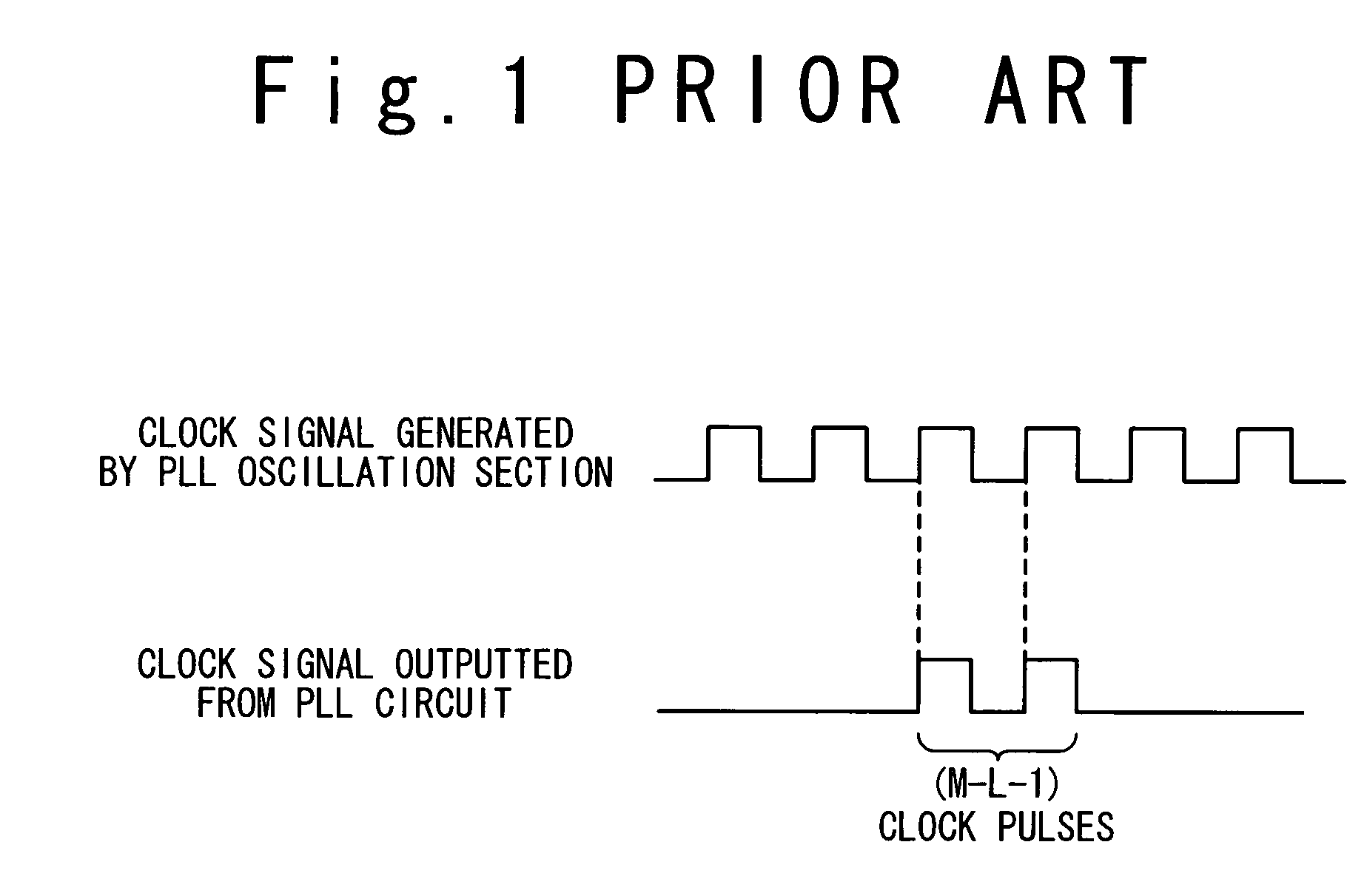

Semiconductor integrated circuit with delay test circuit, and method for testing semiconductor integrated circuit

A semiconductor integrated circuit includes an input side flip-flop; a combinational circuit having an input connected with the input side flip-flop; an output side flip-flop connected with an output of the combinational circuit; and a delay test circuit. The delay test circuit generates output clock pulses by removing an optional one from equal to or more than 3 continuing clock pulses of an input clock signal, and supplies the output clock pulse to the input side flip-flop and the output side flip-flop.

Owner:RENESAS ELECTRONICS CORP

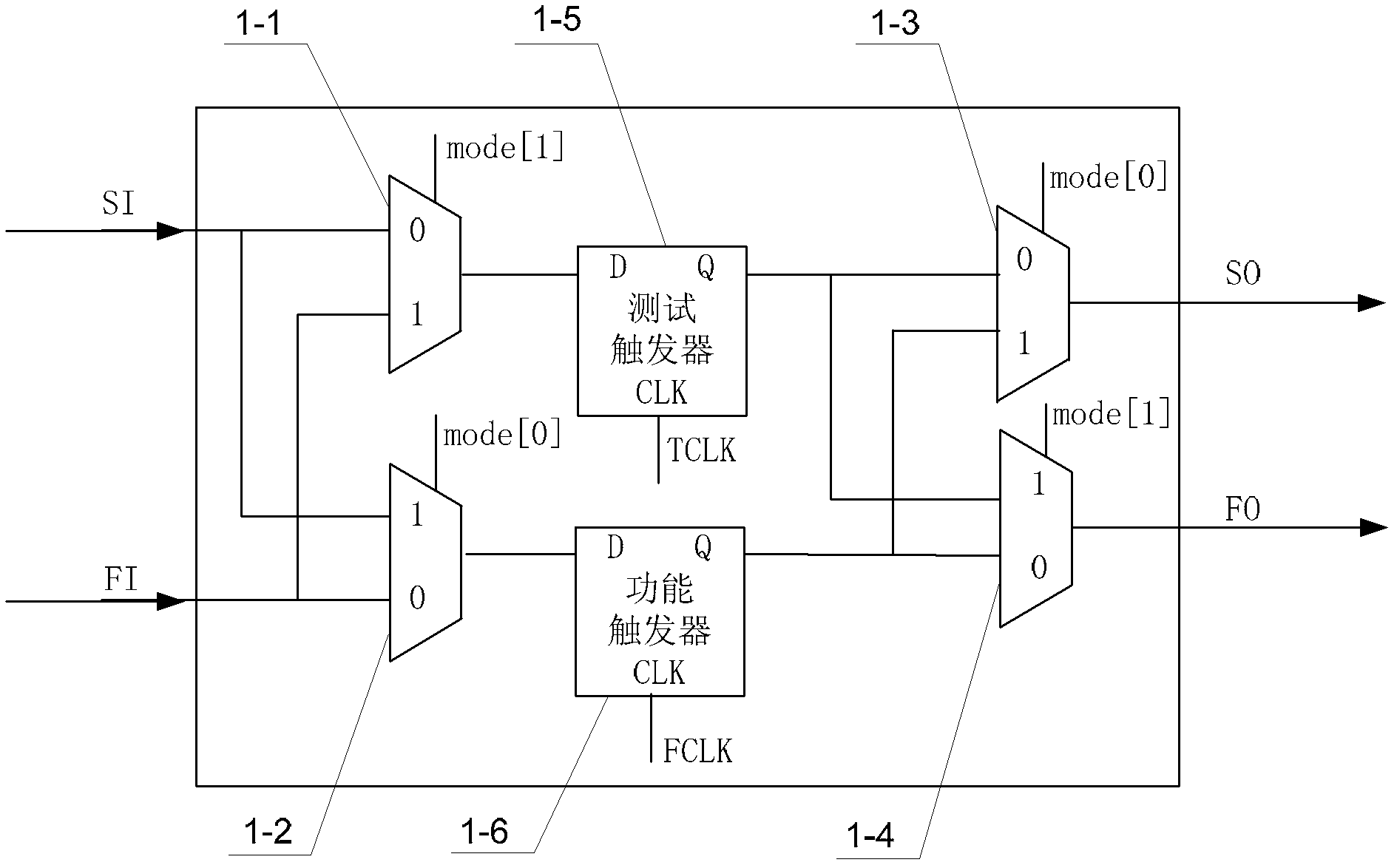

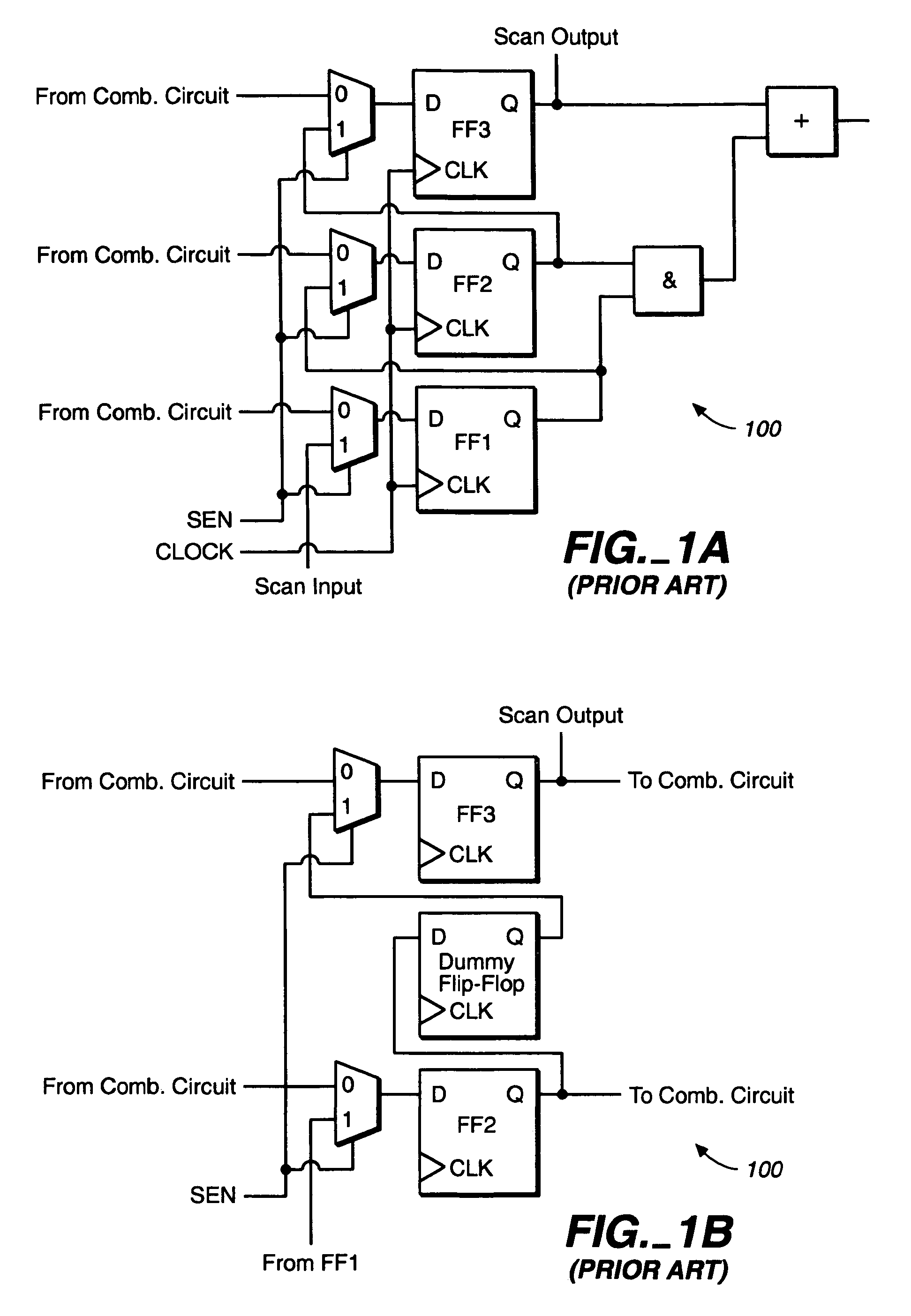

Scan chain and method that realizing high speed testing circuitry

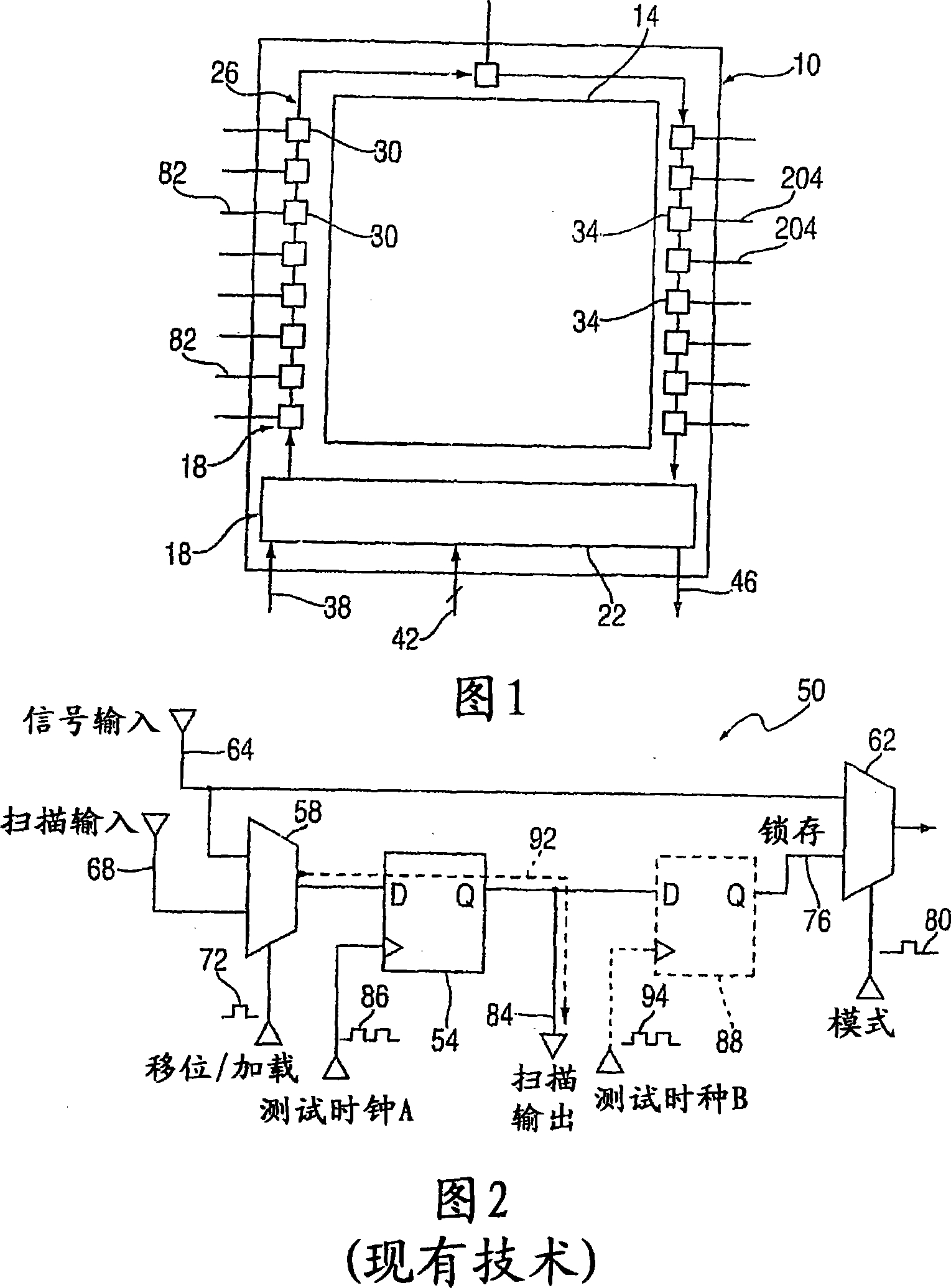

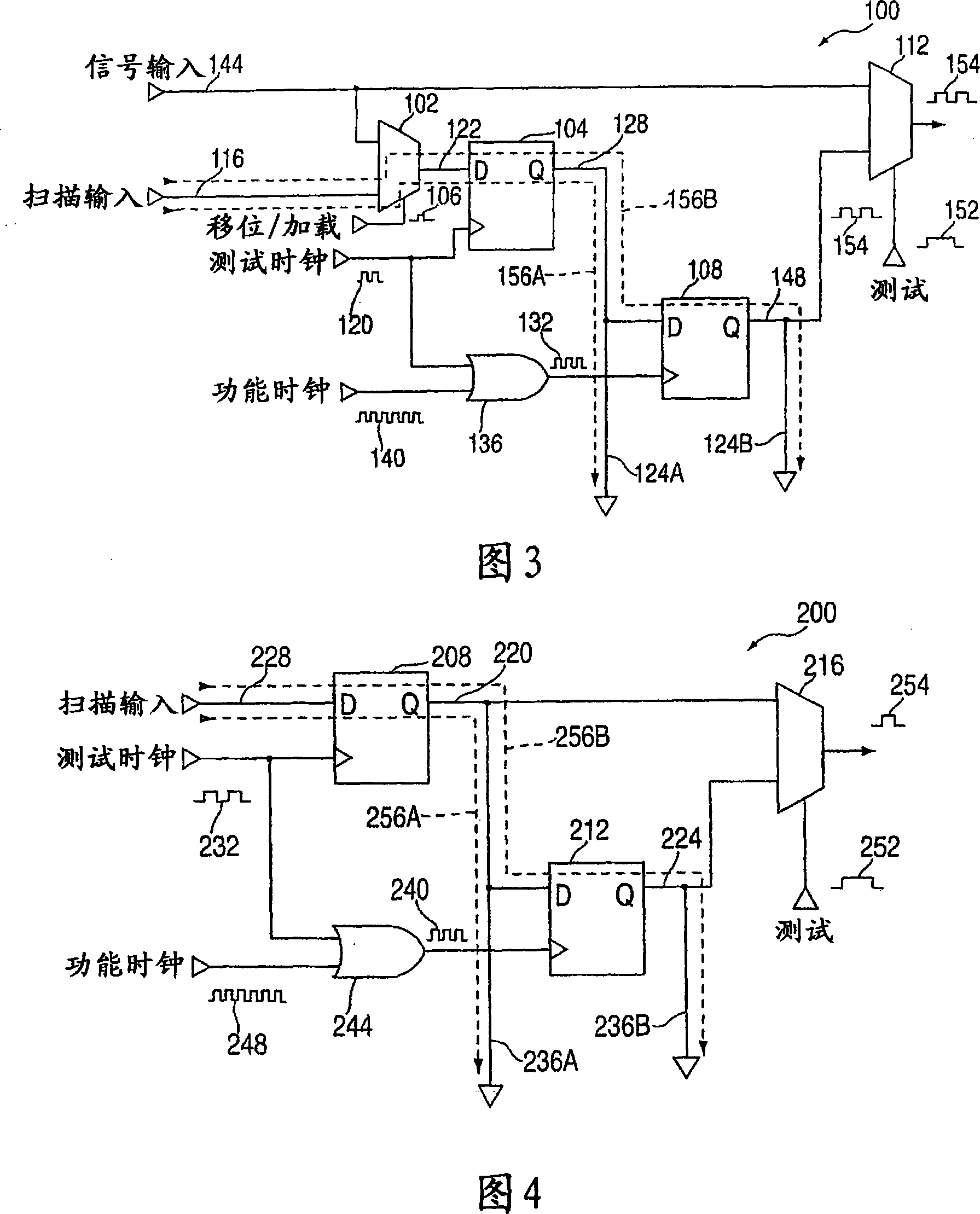

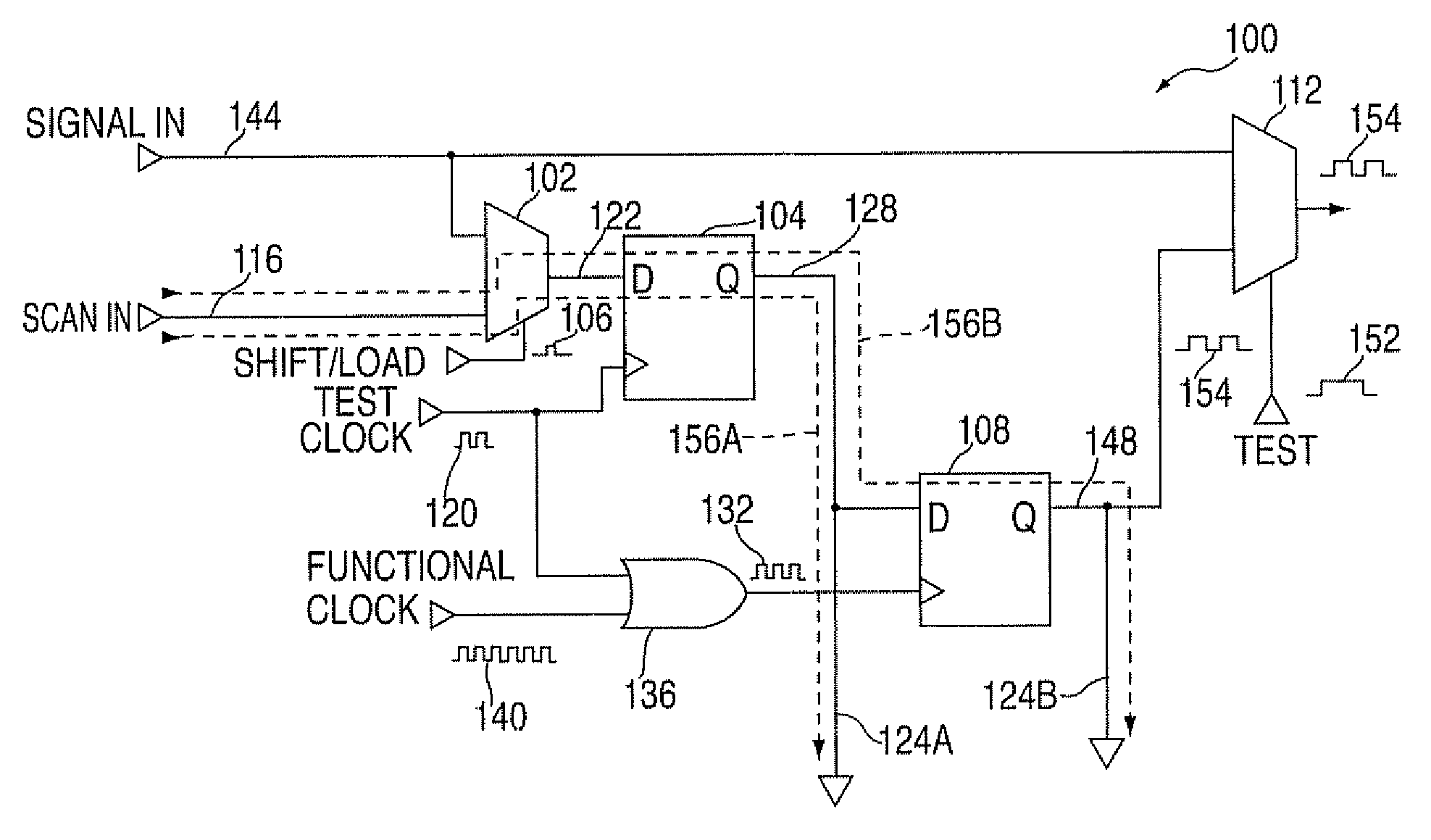

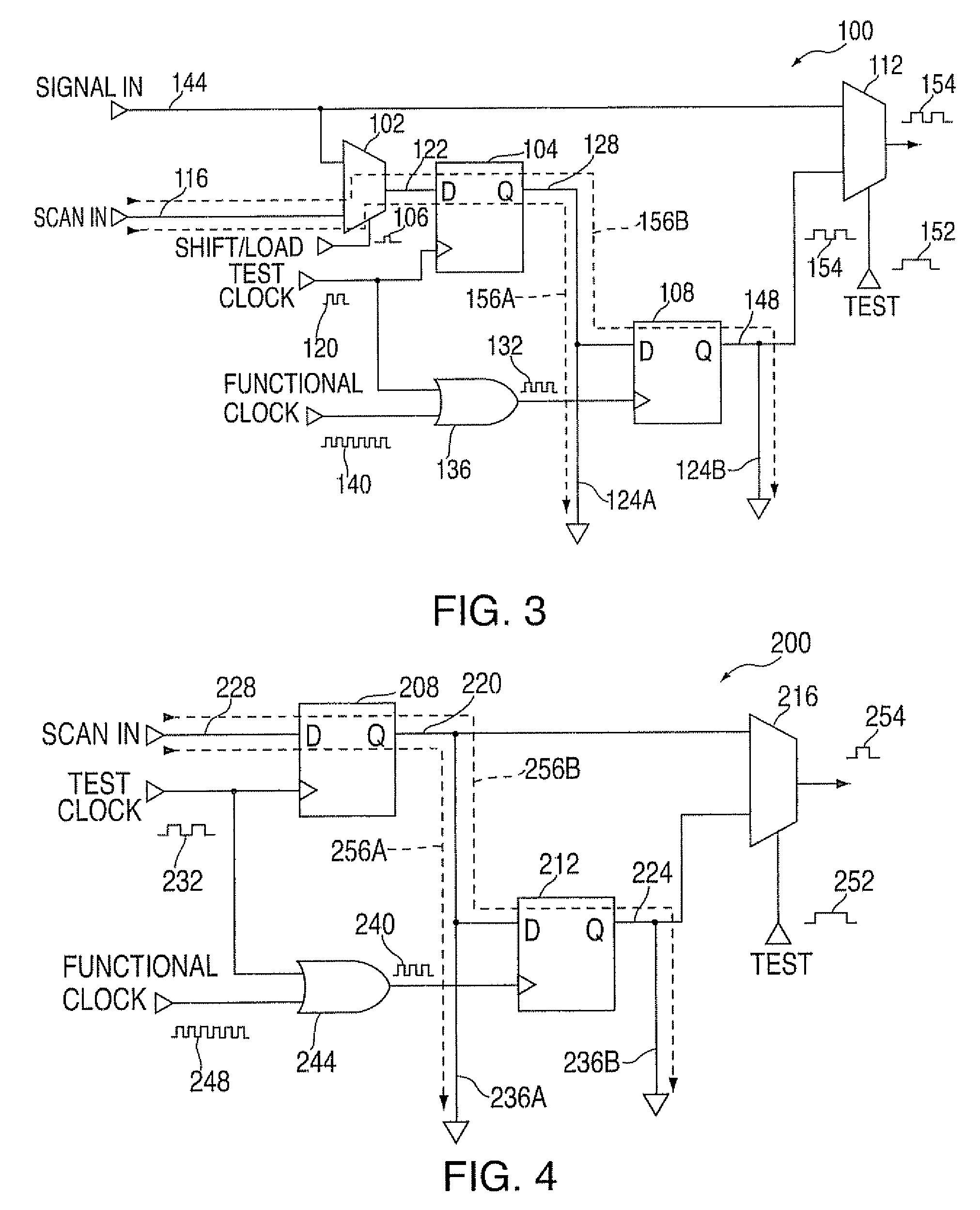

Boundary scan circuitry that includes a plurality of scan cells that each contain two scan registers each for storing a respective test value. During on-chip or inter-chip testing, one of the scan registers is responsive to a functional clock signal so that the test cell generates transition delay test data having at least one state transition made at the speed of the functional clock signal. The transition delay test data allows the integrity of on-chip functional circuitry or the integrity of inter-chip circuitry to be verified at full functional speed.

Owner:GLOBALFOUNDRIES INC

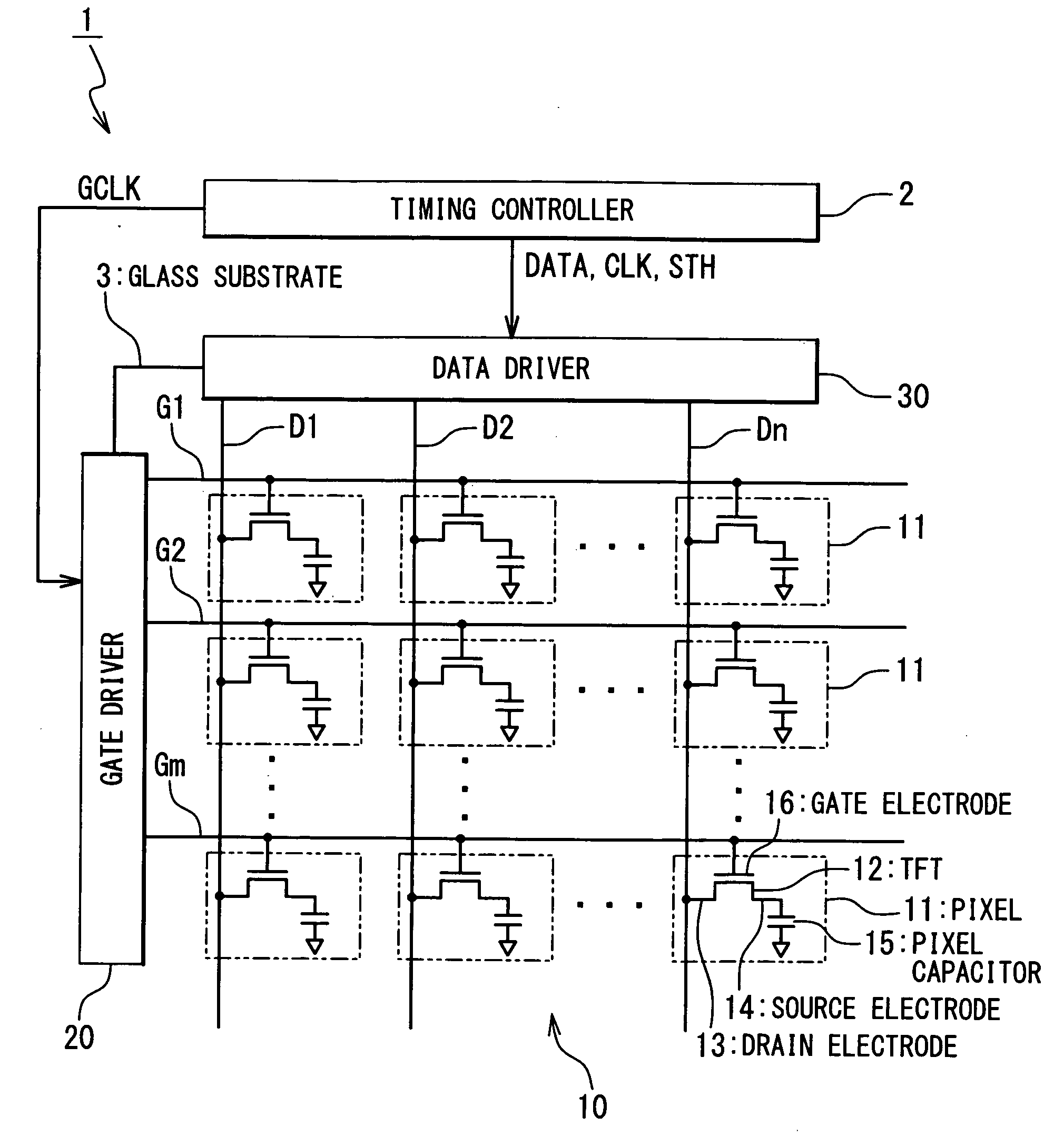

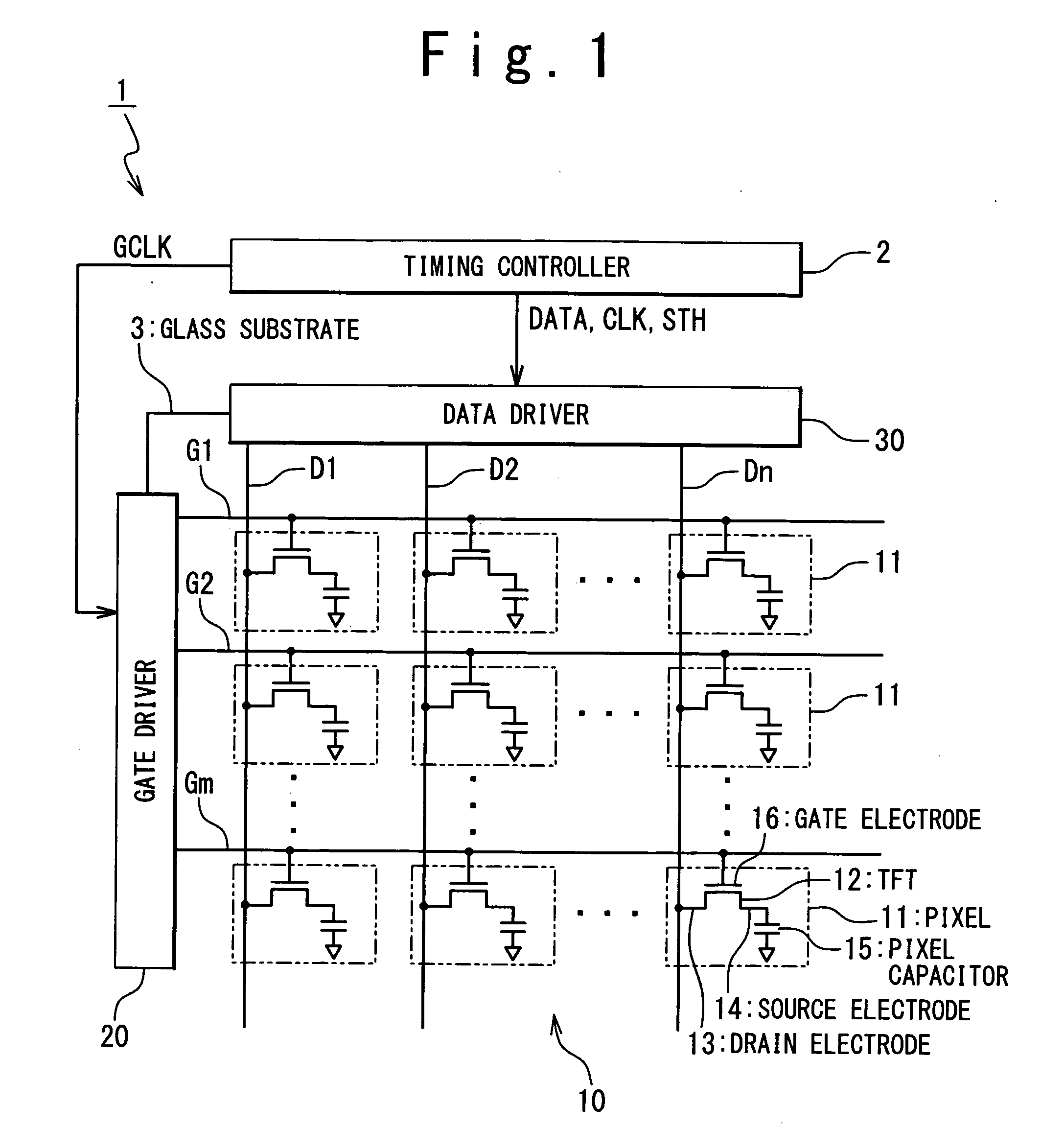

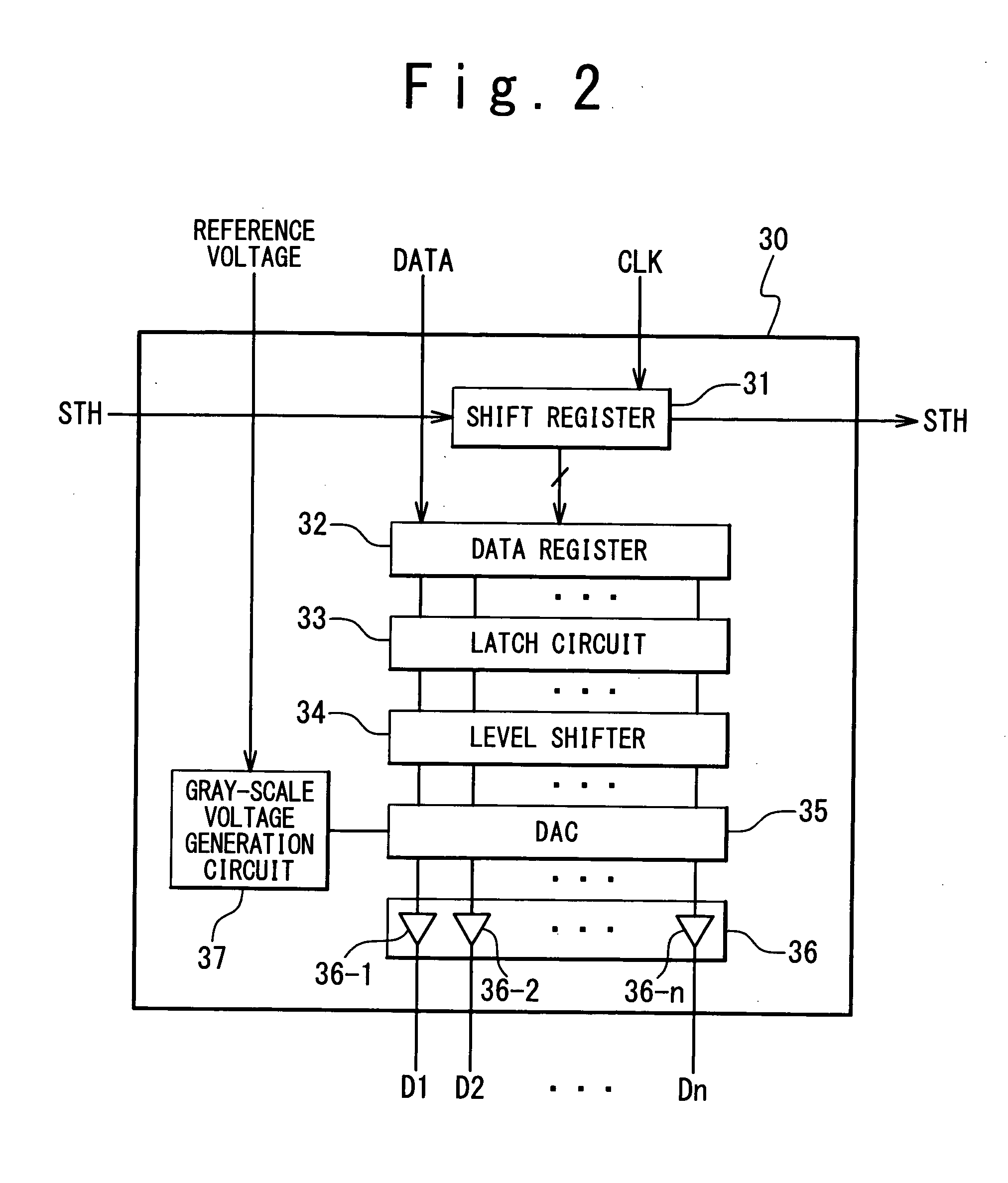

Data driver for display device, test method and probe card for data driver

InactiveUS20090015572A1Quality is determinedAccurately determineCathode-ray tube indicatorsFault locationAudio power amplifierProbe card

A data driver of a display device includes: a DAC (Digital Analog Converter) outputting a drive signal for driving a signal line of a displaying unit; an amplifier amplifying the drive signal outputted by the DAC and outputting the drive signal to the signal line; a repair amplifier having an input and an output, wherein the signal line is separated by a breakage point into a connected data line connected to the amplifier and a disconnected data line not connected to the amplifier, and the input of the repair amplifier is connected to the connected data line and the output of the repair amplifier is connected to the disconnected data line; and a switch supplying the drive signal to the input of the repair amplifier for testing the repair amplifier. An output delay test for the repair amplifier can be performed under a condition similar to that of the amplifier.

Owner:RENESAS ELECTRONICS CORP

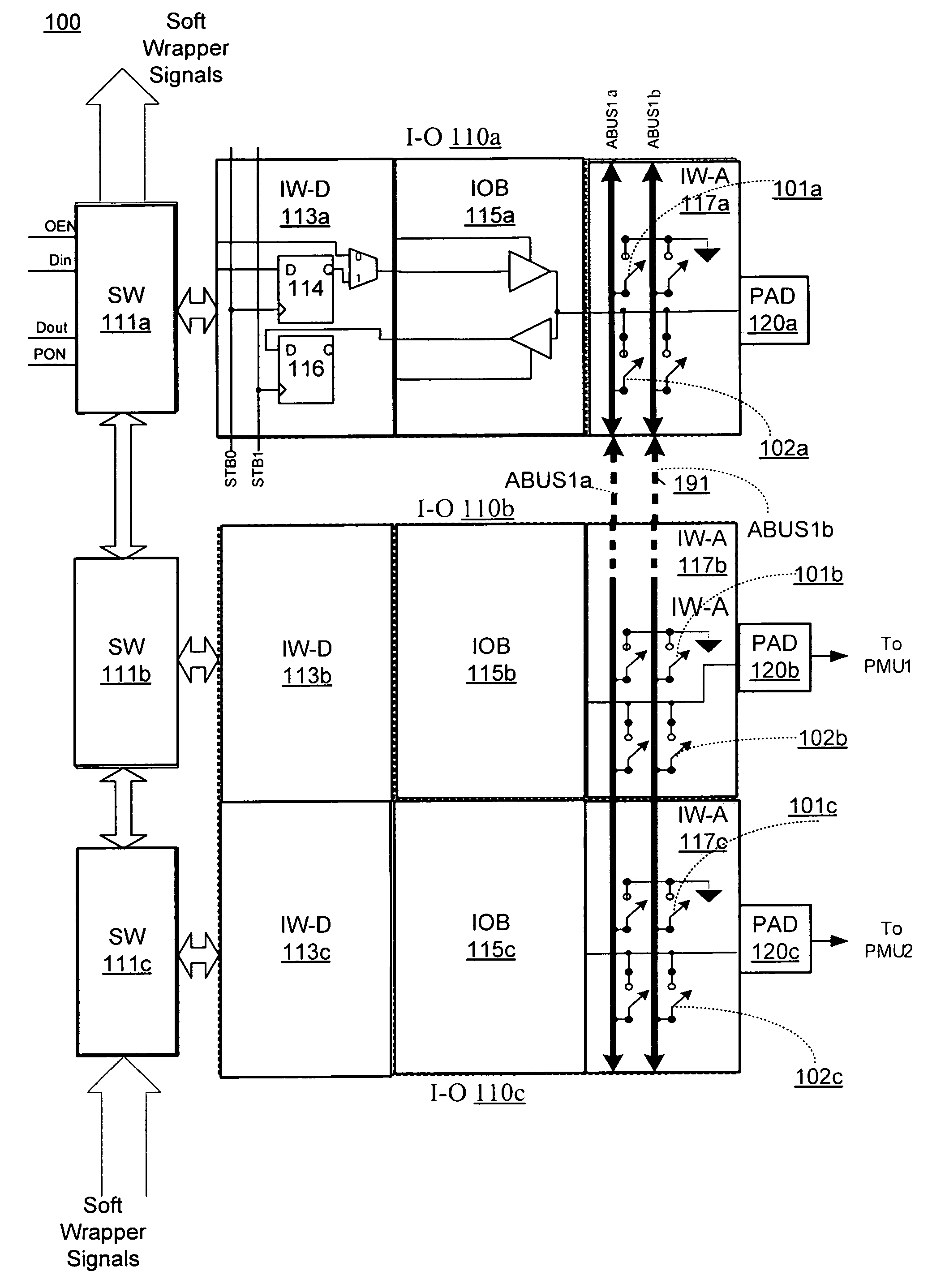

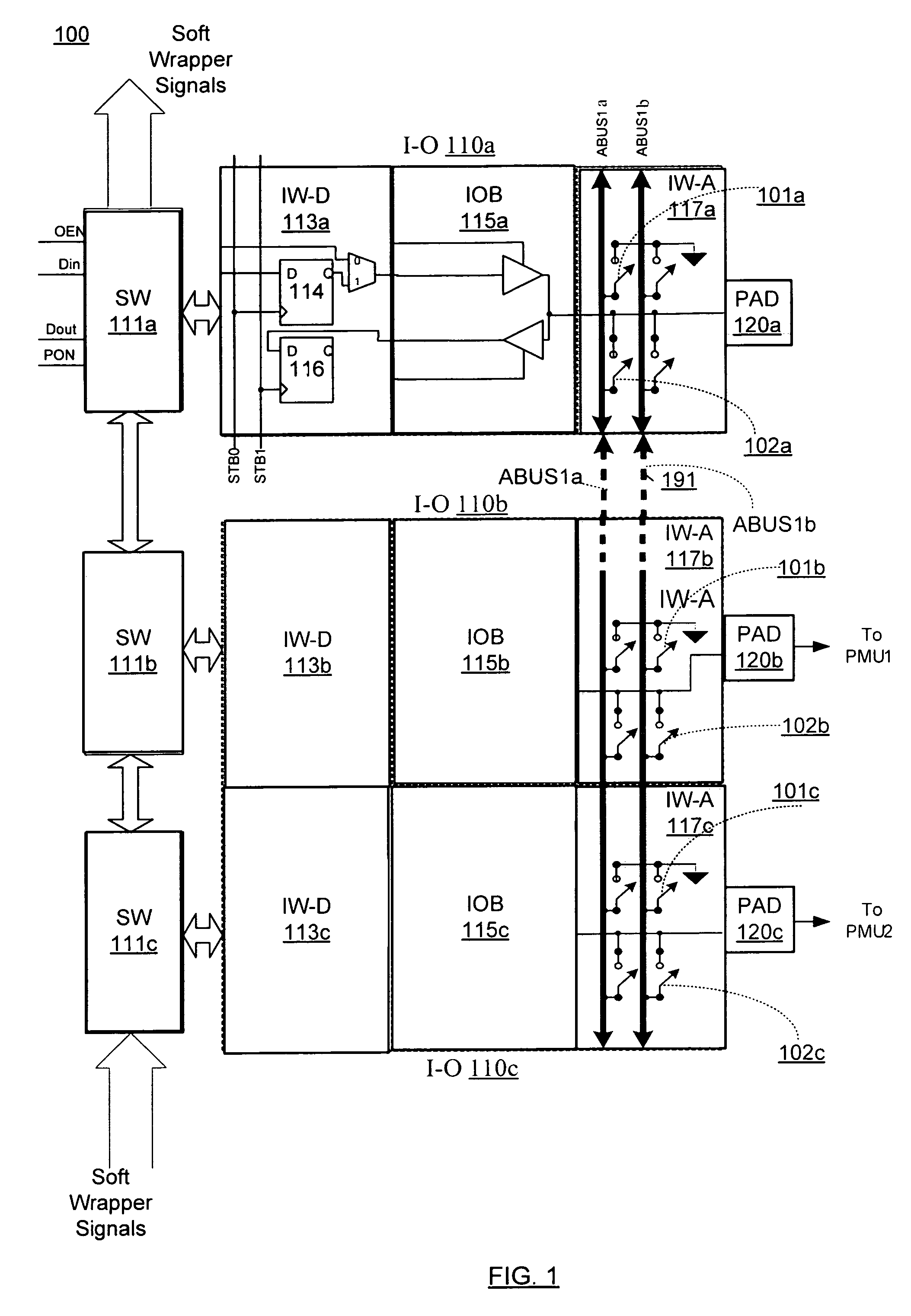

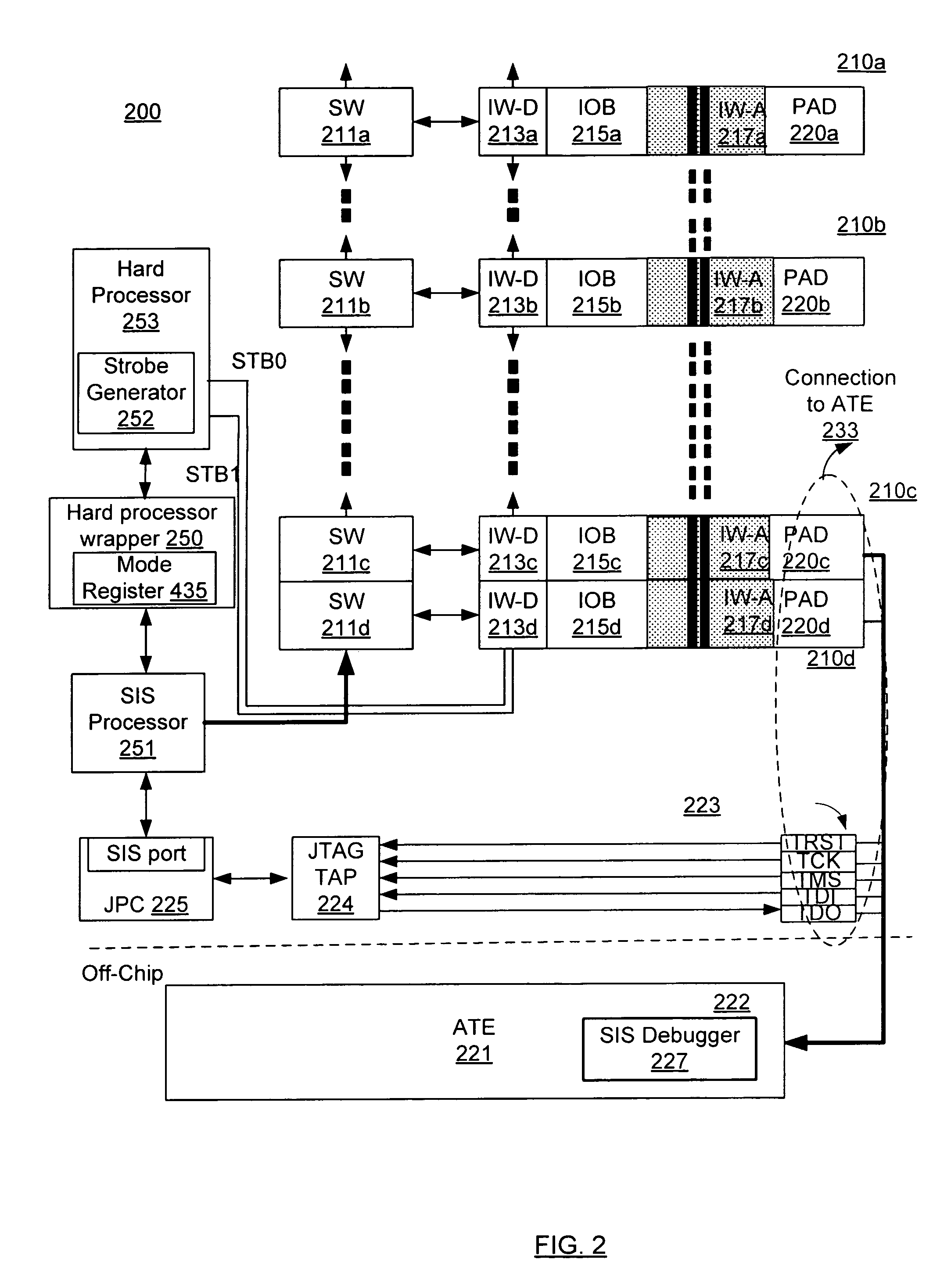

Methods and apparatuses for external delay test of input-output circuits

Various methods and apparatuses are described for a system that includes some on-chip components, e.g., I-Os, test processors, soft wrappers, etc., an external testing unit that provides Parametric Measurement Unit (PMU) capability, and various tests performed on the I-Os by the on-chip testing logic, the test vector patterns supplied by the external testing unit.

Owner:SYNOPSYS INC

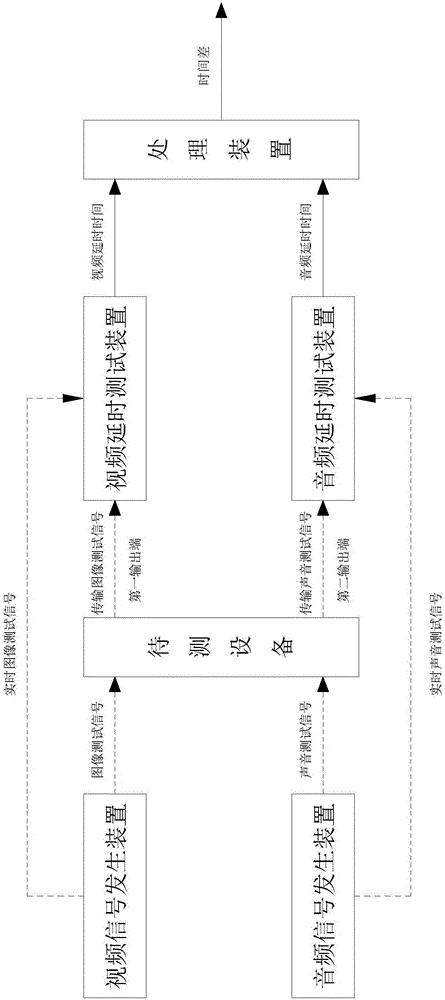

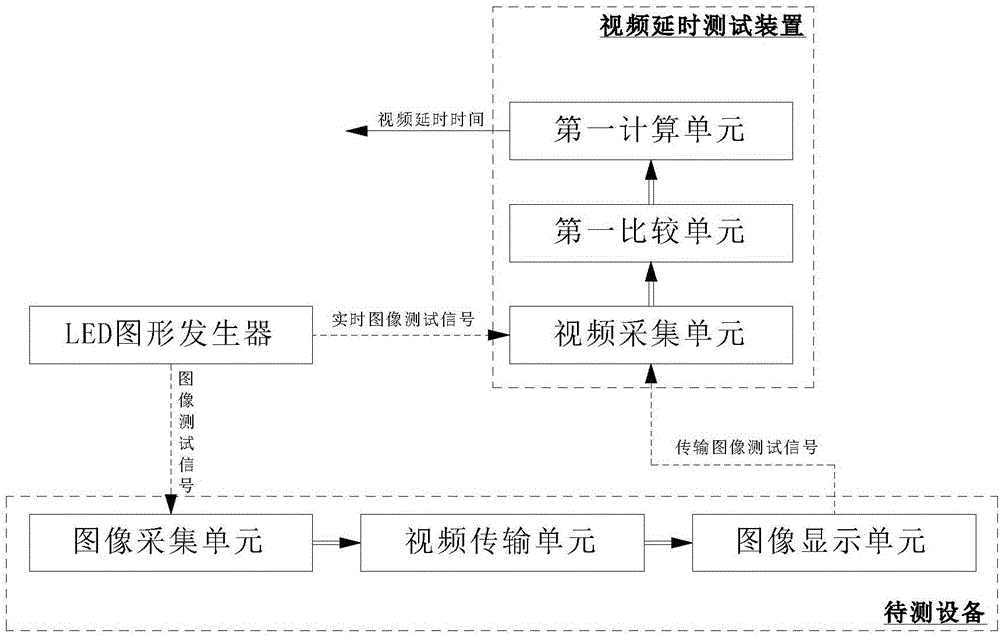

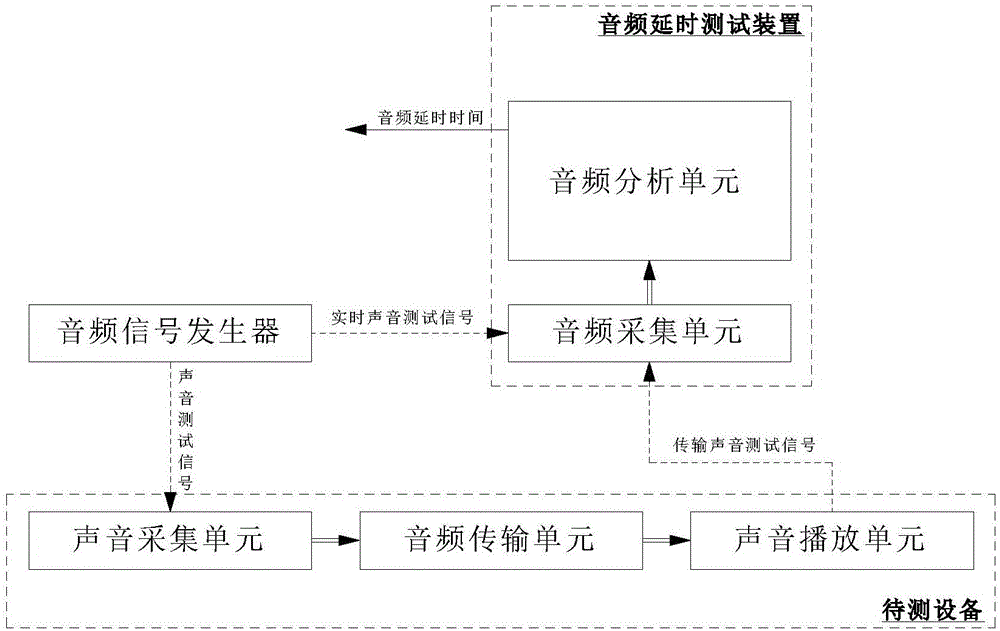

System and method for testing synchronization of audio and video

InactiveCN106060534AEasy accessAccurate acquisitionTelevision systemsSelective content distributionComputer hardwareVideo transmission

The invention relates to the technical field of testing of audio and video devices, and in particular relates to a system and a method for testing the synchronization of an audio and a video. The system and the method can be applied to a synchronization test of an audio and video synchronous transmission playing device, and particularly can simply and accurately achieve a performance test of an audio and video synchronous transmission playing system (such as a building security and protection system and a video communication system) with a high requirement on audio and video synchronization performance, namely a video delay time and an audio delay time of the audio and video synchronous transmission playing device can be simply, accurately and feasibly acquired by respectively using a video delay test device and an audio delay test device, and the audio and video synchronization performance of the audio and video synchronous transmission playing device can be accurately learned by comparing the acquired video delay time with the acquired audio delay time.

Owner:THE THIRD RES INST OF MIN OF PUBLIC SECURITY

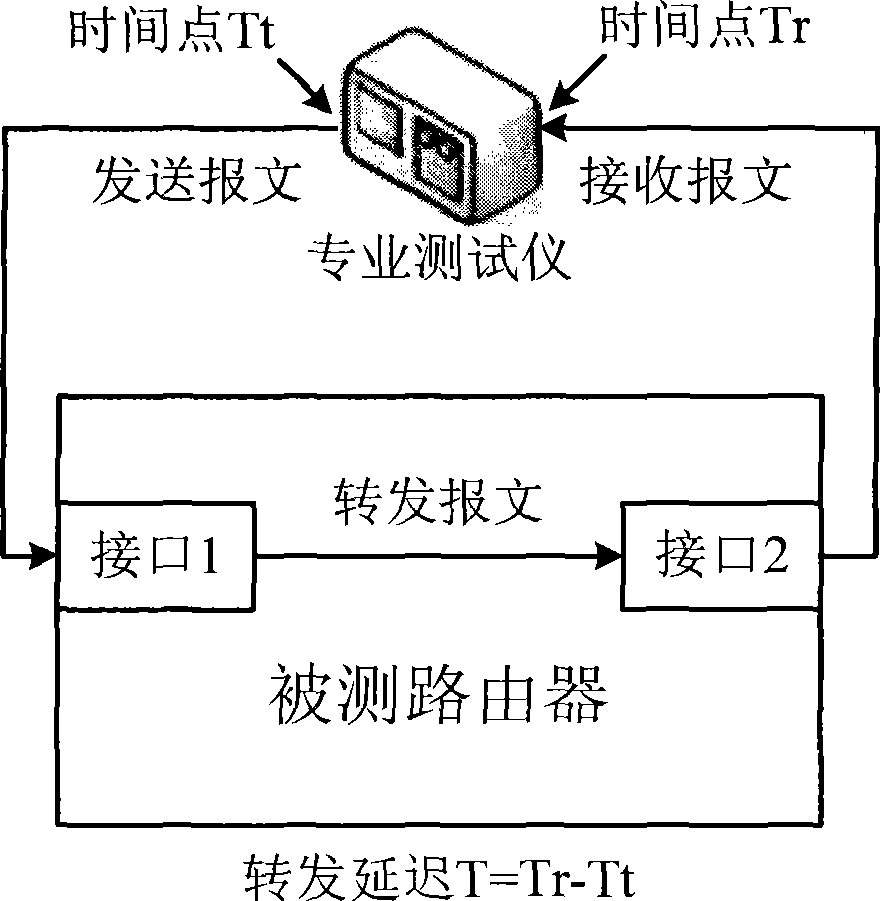

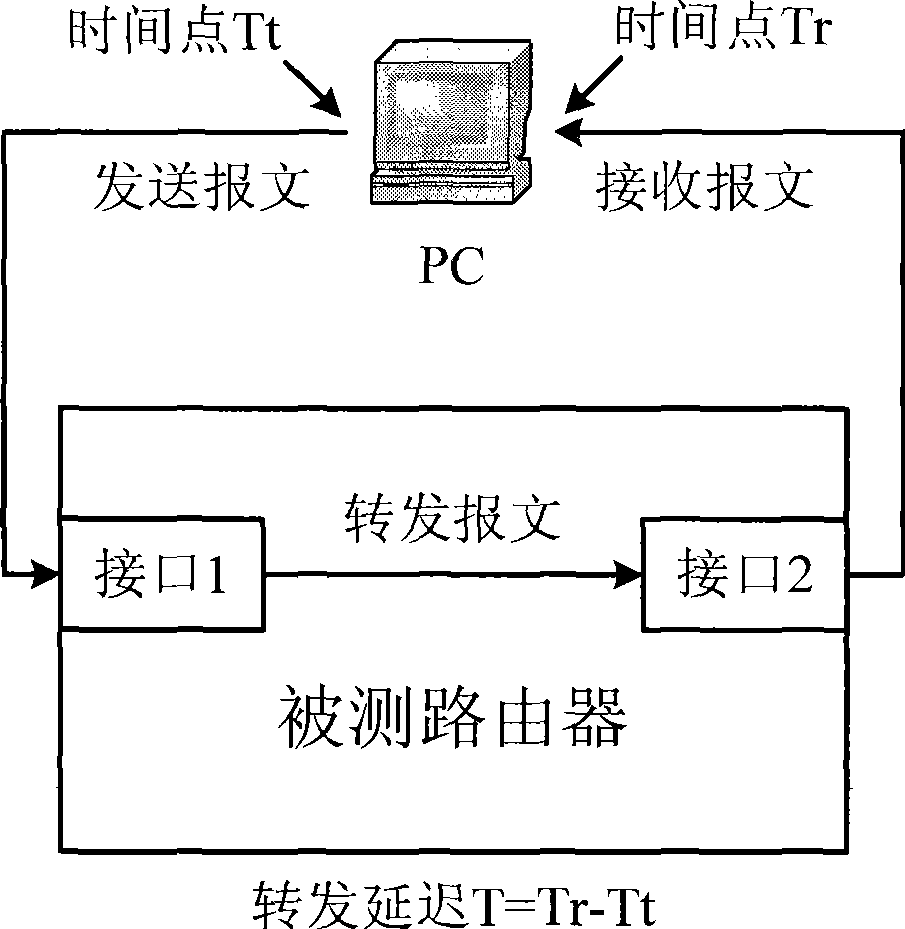

Method and system for testing forward delay

InactiveCN101547063AReduce testing costsReduce mistakesError preventionData switching networksCyclic testIp address

The invention provides a method and a system for testing forward delay, which are used for improving the accuracy of the forward delay test of common testing equipment. Through the configuration of a binding relation between a next hop IP address received by tested equipment and the port of the tested equipment on the tested equipment, the method enables a sent test message to perform circular test in the tested equipment. Therefore, the obtained result of the forward delay test has reduced errors caused by self time consumption in the forward delay test of a common testing instrument, so the high test cost caused by the use of a professional testing instrument is saved.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

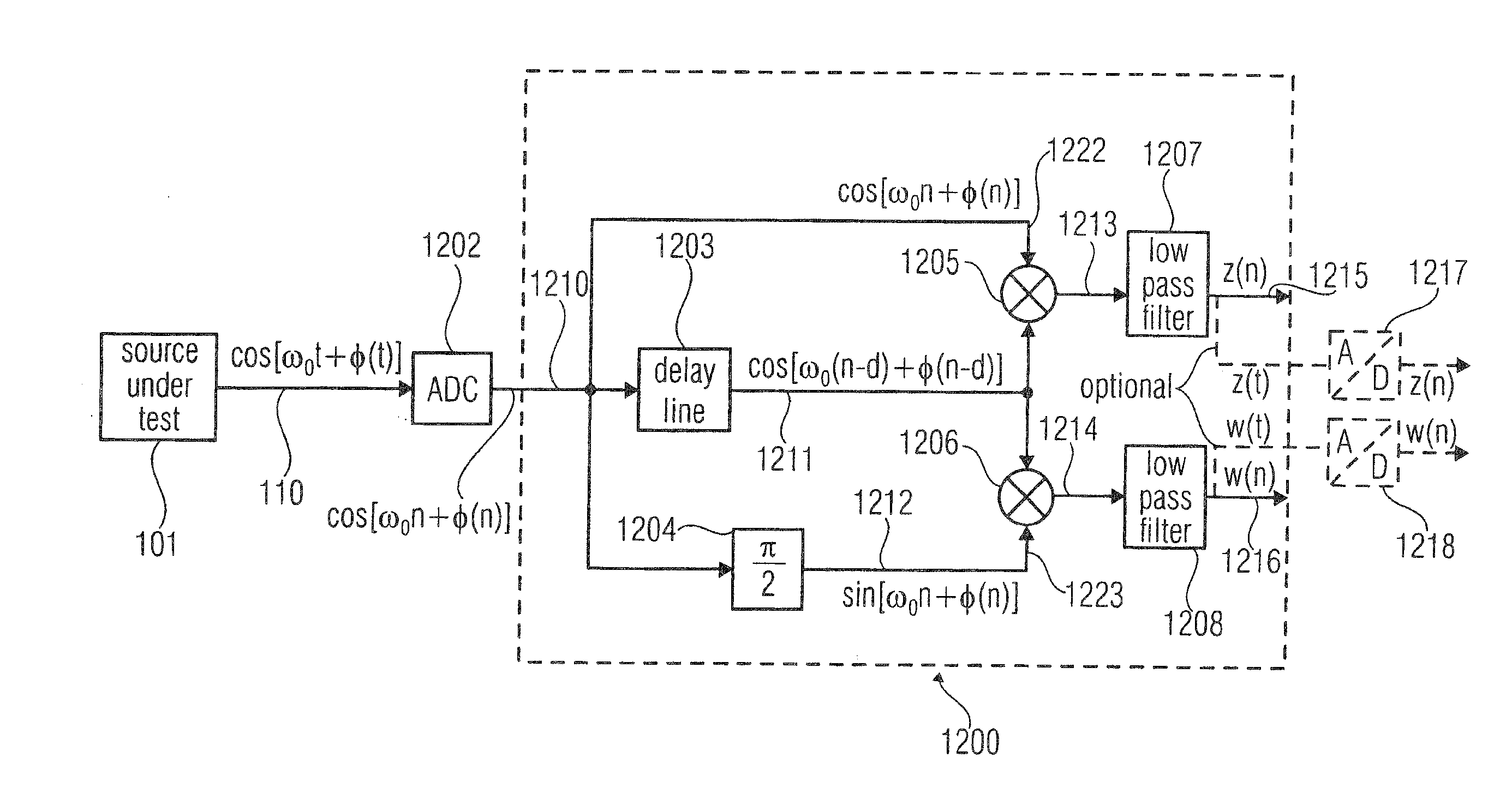

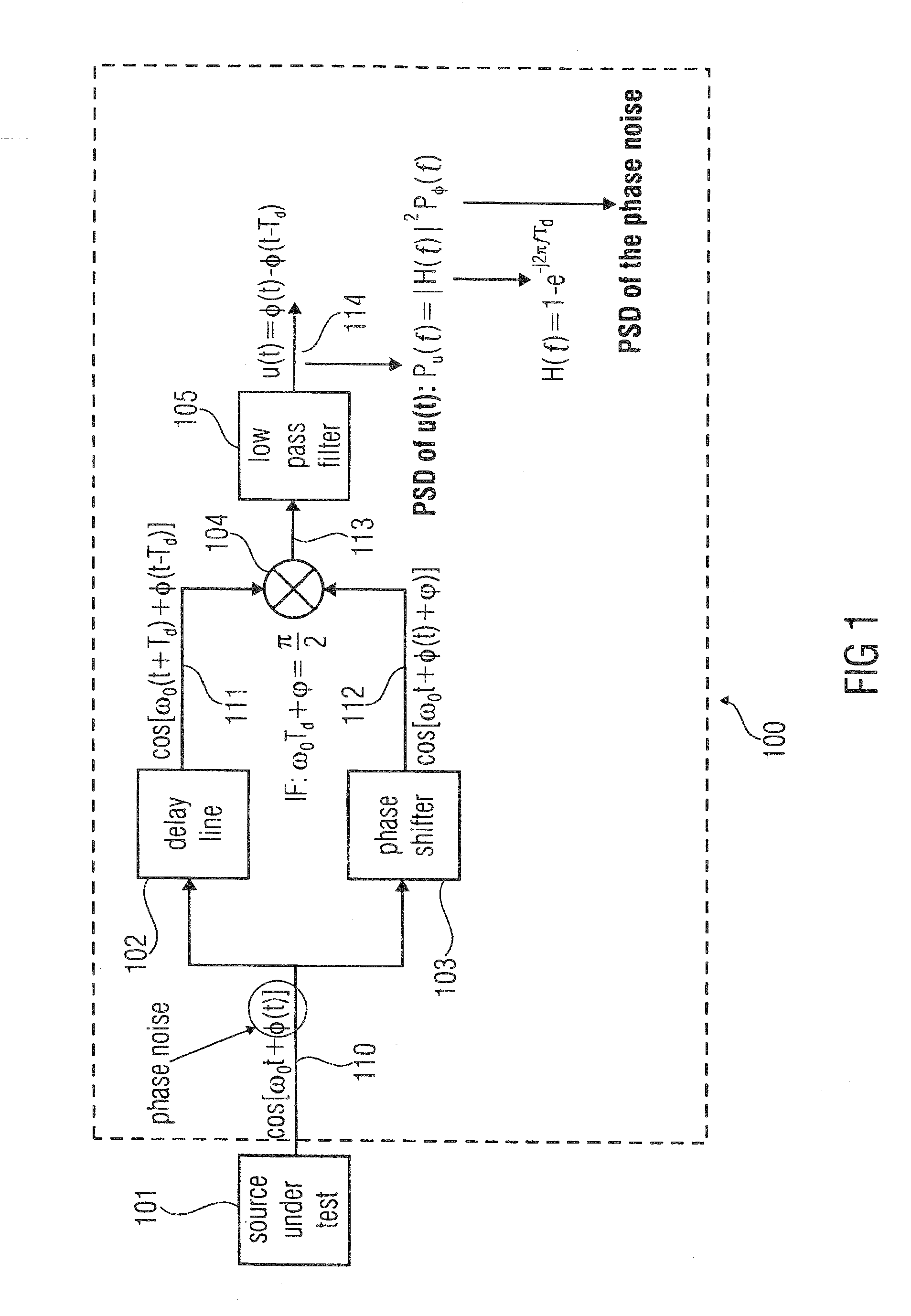

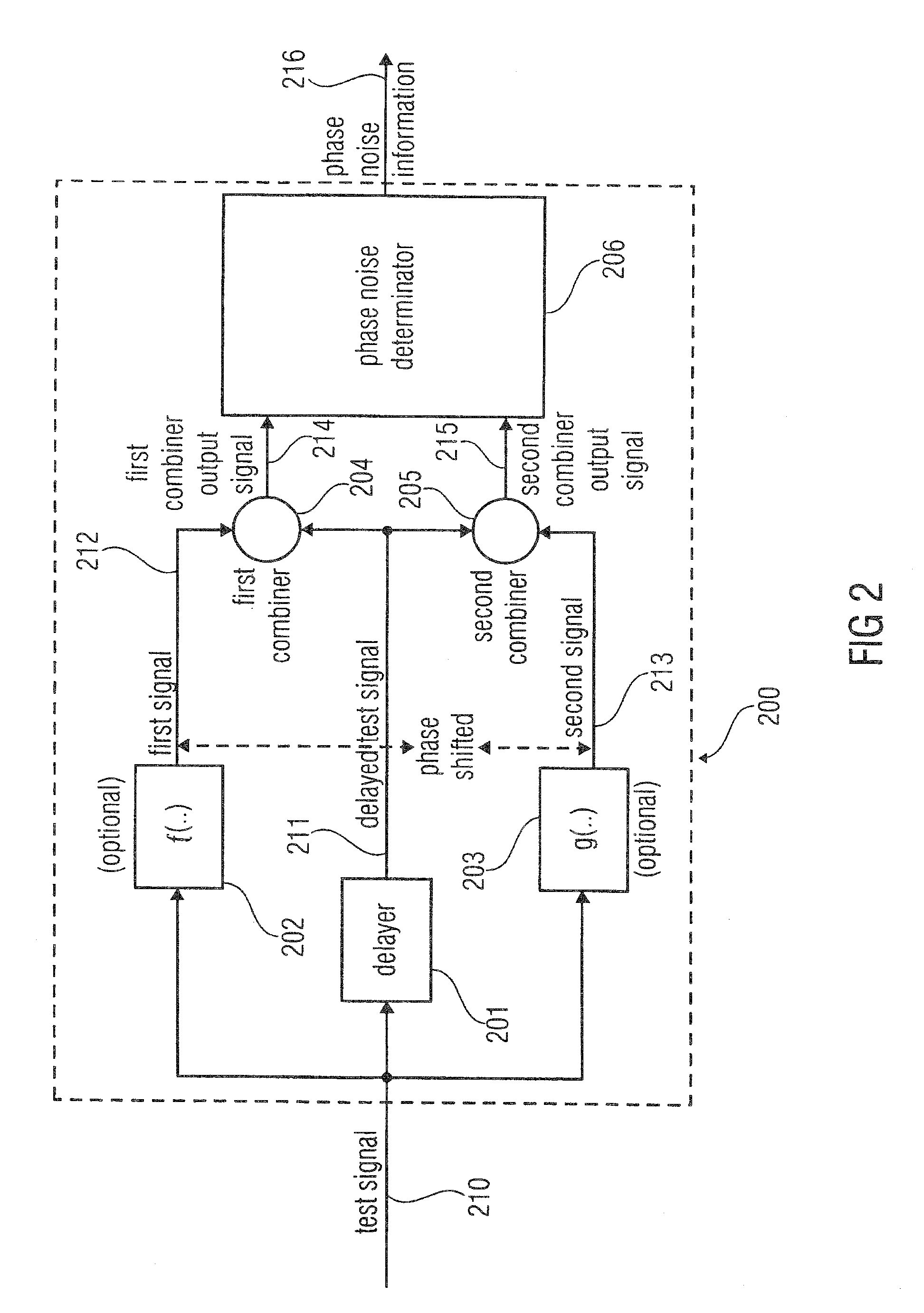

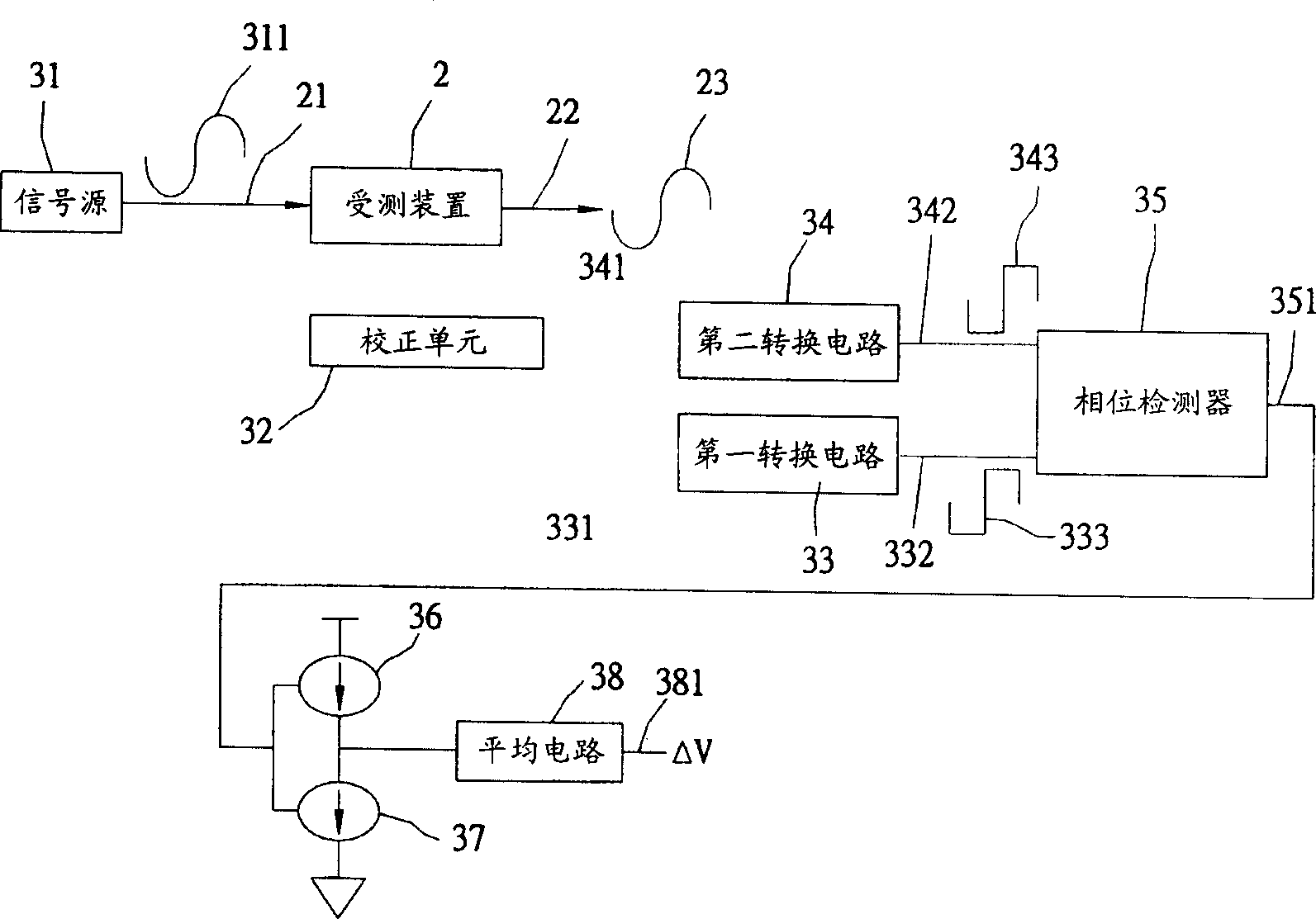

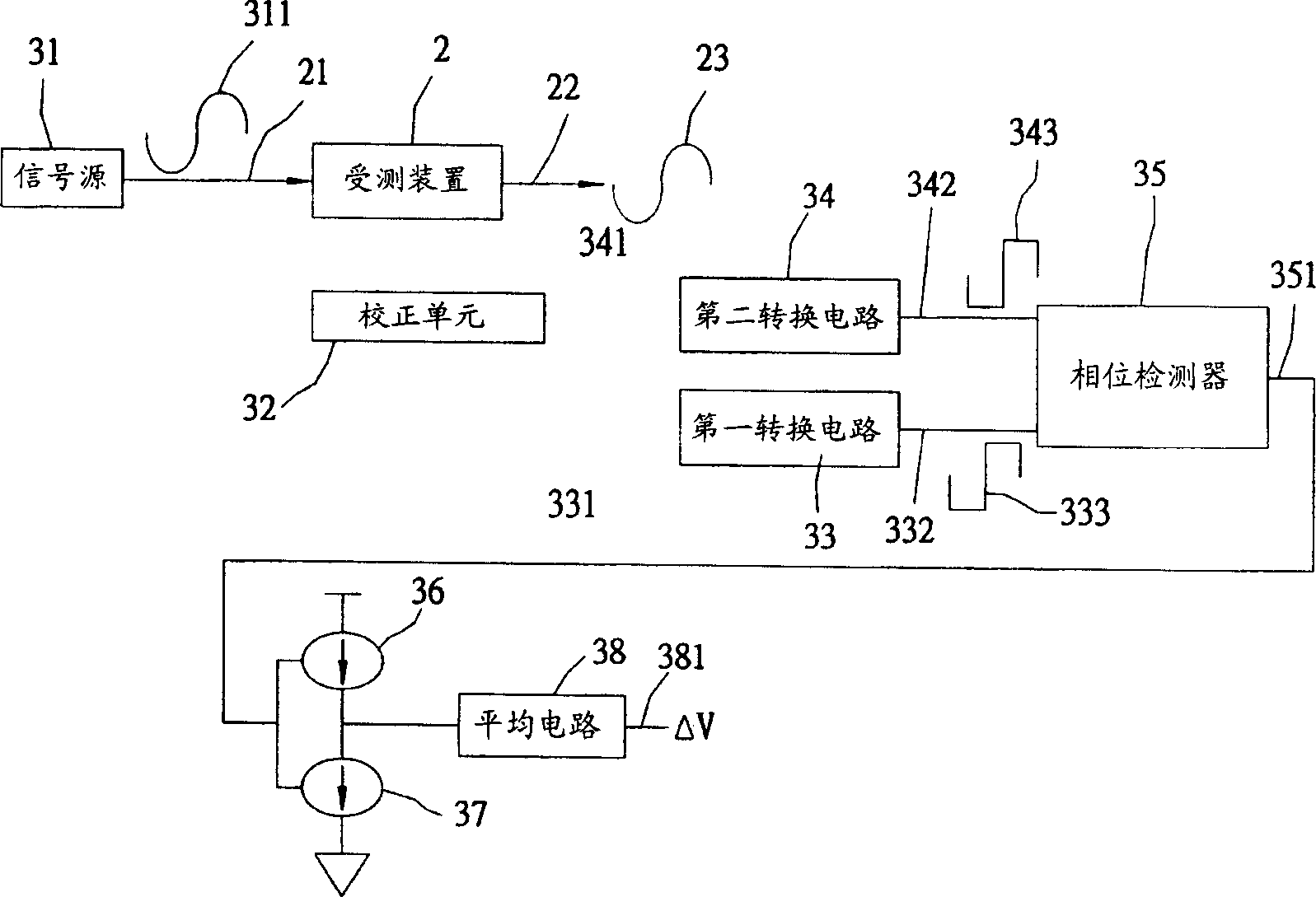

Test device and test method for measuring a phase noise of a test signal

ActiveUS20120217980A1Simplify the calibration processSimple structureNoise figure or signal-to-noise ratio measurementElectrical testingPhase shiftedPhase noise

A test device for measuring a phase noise of a test signal includes a delayer configured to delay the test signal to provide a delayed test signal, a first combiner, a second combiner, and a phase noise determinator. The first combiner is configured to combine a first signal with the delayed test signal to provide a first combiner output signal. The first signal is based on the test signal or a signal identical to the test signal. The second combiner is configured to combine a second signal with the delayed test signal, wherein the second signal is phase-shifted with respect to the first signal to provide a second combiner output signal. The second signal is based on the test signal. The phase noise determinator is configured to provide phase noise information that depends on the first combiner output signal and the second combiner output signal.

Owner:ADVANTEST CORP

Scan chain circuitry that enables scan testing at functional clock speed

Boundary scan circuitry that includes a plurality of scan cells that each contain two scan registers each for storing a respective test value. During on-chip or inter-chip testing, one of the scan registers is responsive to a functional clock signal so that the test cell generates transition delay test data having at least one state transition made at the speed of the functional clock signal. The transition delay test data allows the integrity of on-chip functional circuitry or the integrity of inter-chip circuitry to be verified at full functional speed.

Owner:GLOBALFOUNDRIES INC

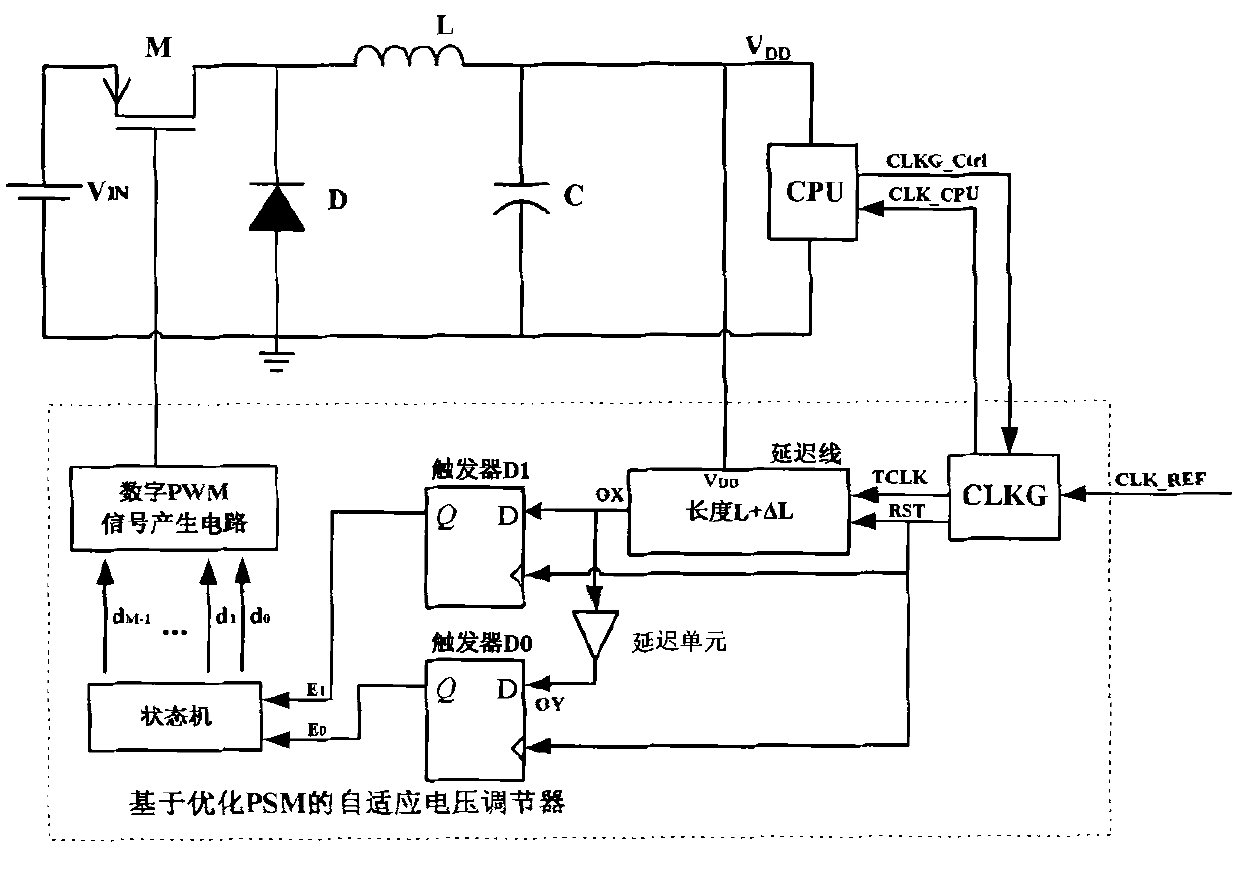

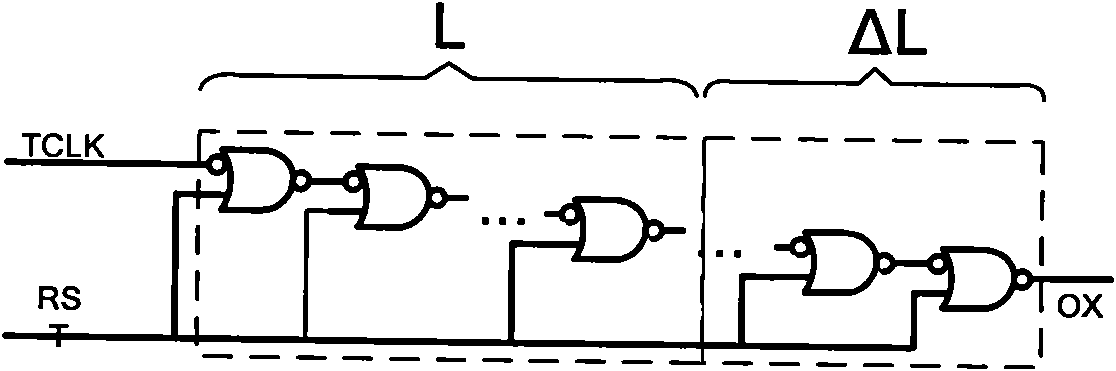

Self-adaption voltage regulator based on optimized PSM modulation mode

InactiveCN101995894AHigh efficiency under light loadImprove robustnessElectric variable regulationPower electronicsOperating frequency

The invention relates to a self-adaption voltage regulator based on an optimized PSM modulation mode, belonging to the technical field of power electronics and being used for self-adaption on-line regulation on a power supply voltage of a load processor (CPU or DSP). In the self-adaption voltage regulator, a key path of the load processor is copied by adopting a delay line, an N frequency division signal of a working clock of the load processor is used as a delay test signal, and a trigger is used for detecting whether the transmission speed of the delay test signal reaches the requirement in the delay line. When the load processor is in a certain working frequency, if the VDD (Voltage Drain Drain) is overhigh, the delay test signal can pass through the delay line, a power switch of an external power inverter is trially shut off for reducing the VDD; and when the delay test signal can not pass through the delay line, optimized PSM modulation signals with different duty ratios are trially adopted for conducting the power switch of the external power inverter for improving the VDD, and finally, the load processor is ensured to work with minimum voltage under a given working clock frequency, thus the power consumption of the load processor is effectively reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

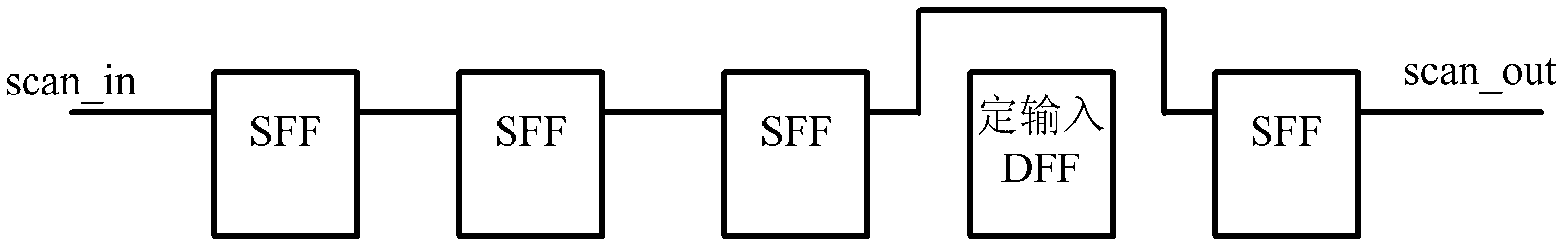

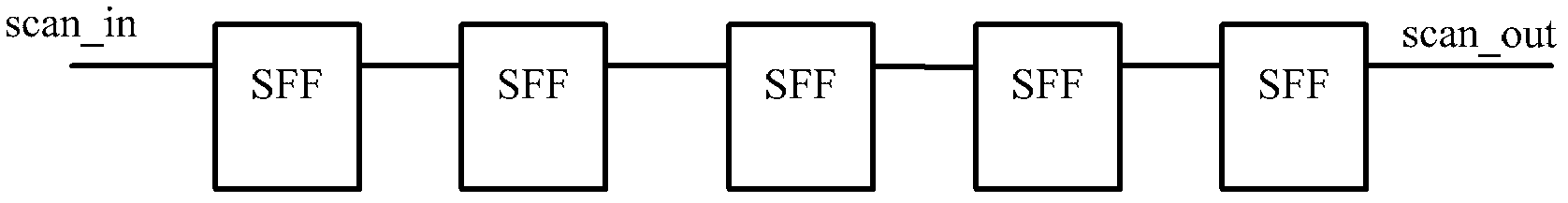

Design method of scanning unit based on partial scanning of improved test vector set

InactiveCN102323538AReduce redundancyReduce hardware redundancyElectrical testingFault coverageOnline test

The invention discloses a design method of a scanning unit based on partial scanning of an improved test vector set, relating to the technical field of SOC (system-on-a-chip) test of digital integrated circuits, and solving the problems of delayed test, hardware redundancy and large required capacity of a memory in the conventional online test method. The method comprises the following steps of: firstly, obtaining an important equivalent output pin which is important to fault detection by stimulating a fault of an equivalent output pin in a combined part of a sequence circuit; secondly, obtaining the improved test vector set by stimulating a fault of an equivalent input pin in the combined part of the sequence circuit; and finally, according to the improved test vector set and an equivalent output pin which is unimportant to the fault detection, dividing triggers into fixed-input triggers and important triggers, and serially connecting the important triggers to form a partial scanningchain. By the method, the obtained scanning unit has a relatively high fault coverage rate and can reduce the hardware redundancy of a test circuit, the digit of bits of the test vector and the memory space.

Owner:HARBIN INST OF TECH

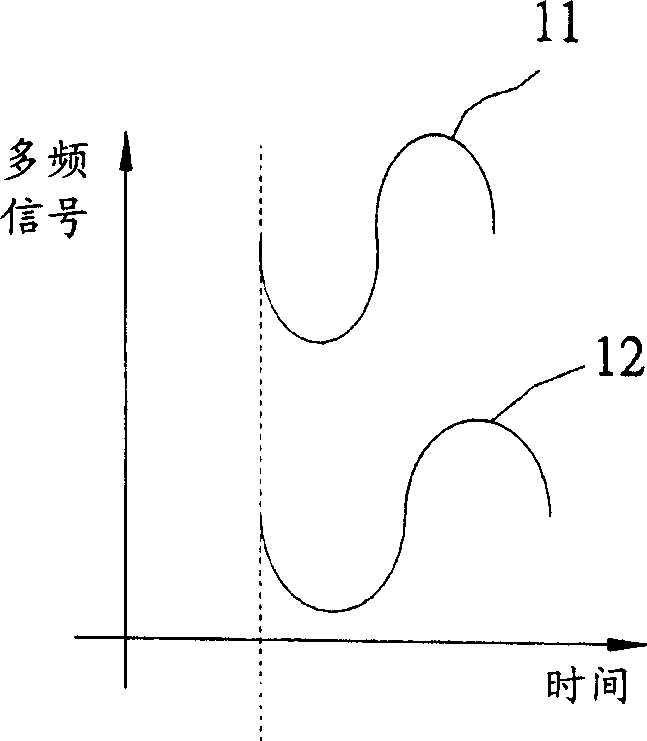

Group delay test method and device thereof

InactiveCN1484035AAccurately find group delayReduce test costsElectronic circuit testingError detection/correctionPhase differenceComputer science

The invention provides a group delay method to test the group delay Tgd. It includes the steps: (A) inputting a known period-T analog single-frequency signal to one input end of the tested device; (B) extracting the input single frequency and the output delayed one and converting them into a first digital signal and a second one, respectively; (C) comparing phase difference of the first and second signals; (D) converting the comparing result into a current I in direct proportion to the phase difference; (E) making the current I flow through a average circuit with a value-known resistance R and obtaining a voltage differenceªñV; and (F) according to known T, I, R andªñV, finding Tgd.

Owner:MEDIATEK INC

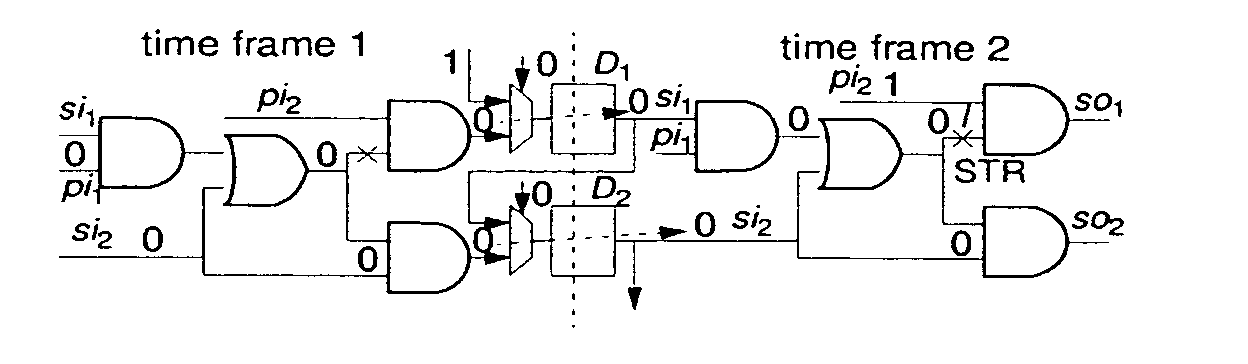

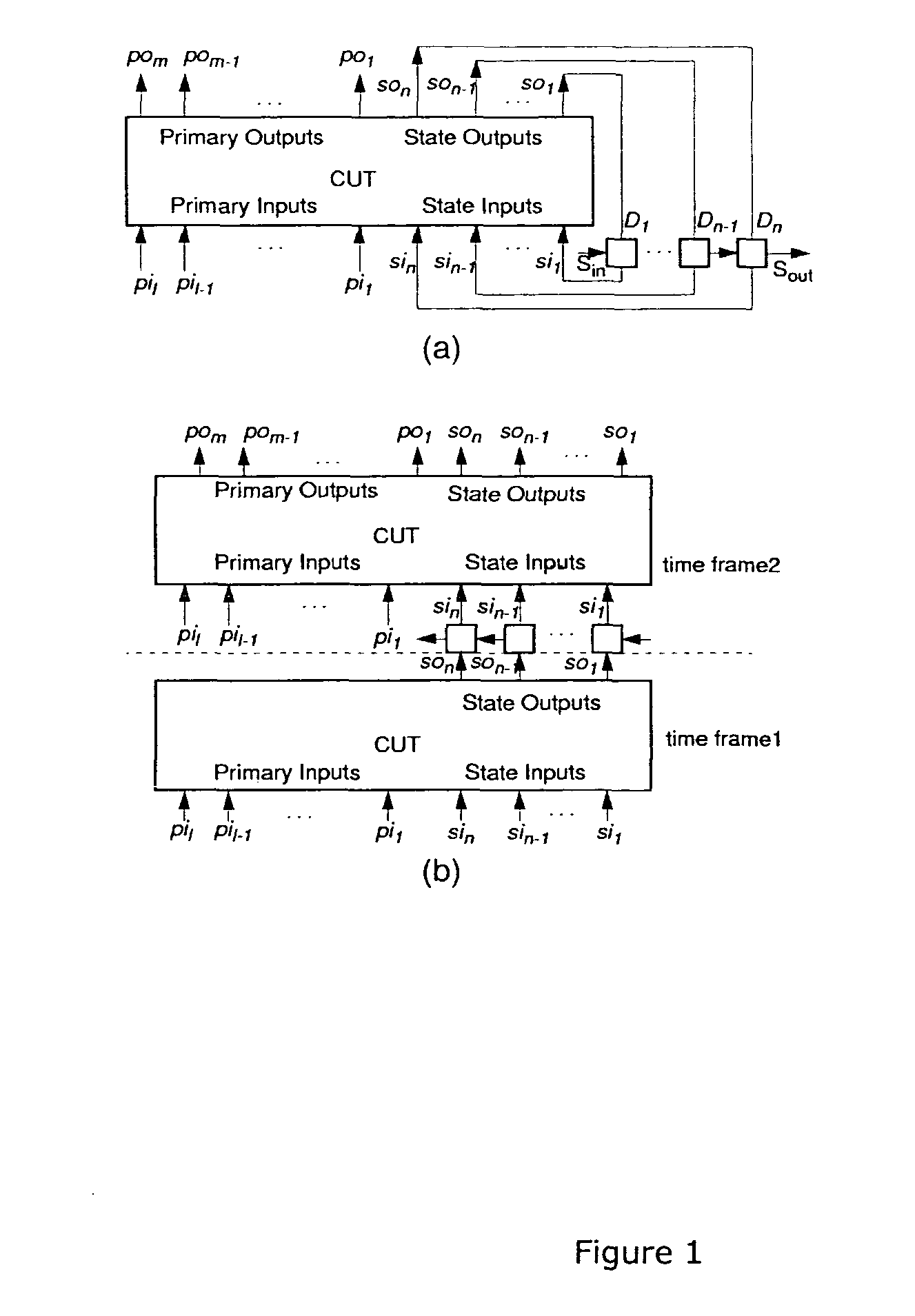

Hybrid scan-based delay testing technique for compact and high fault coverage test set

A scan-based method for testing delay faults in a circuit comprising controlling a subset of state inputs of the circuit by a skewed-load approach and controlling all inputs other than said subset of state inputs by a broad-side approach.

Owner:NEC CORP

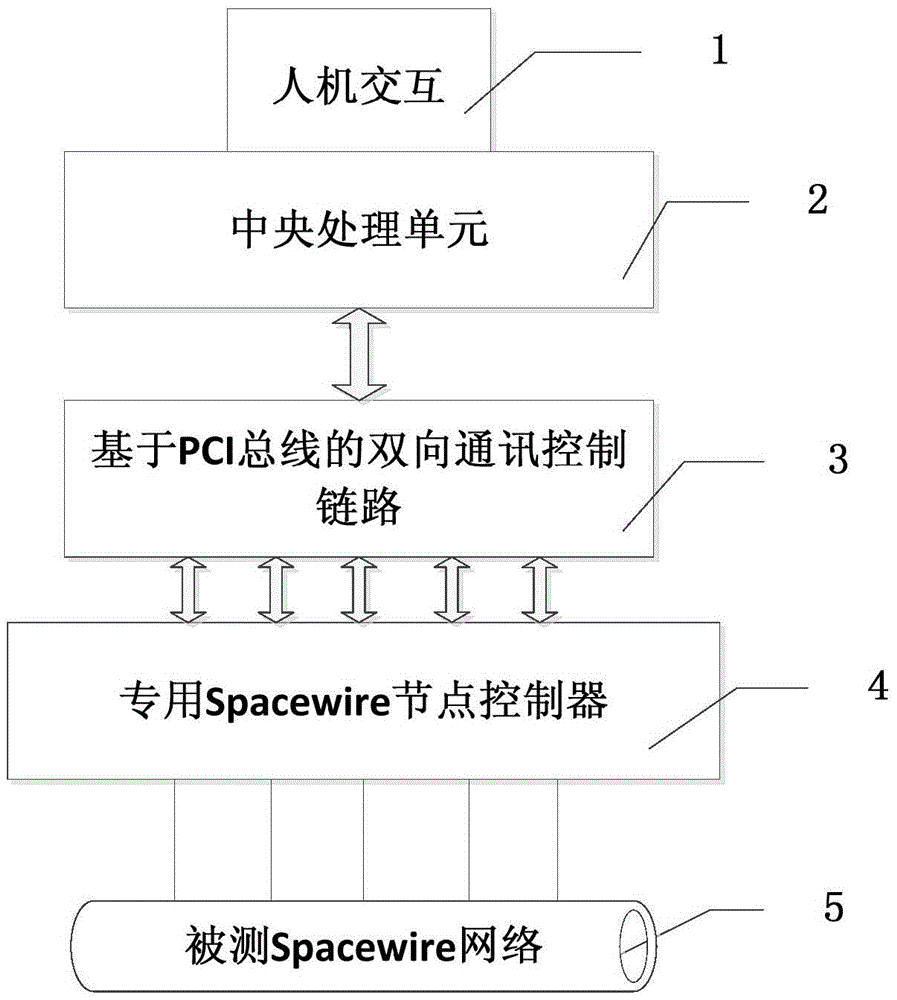

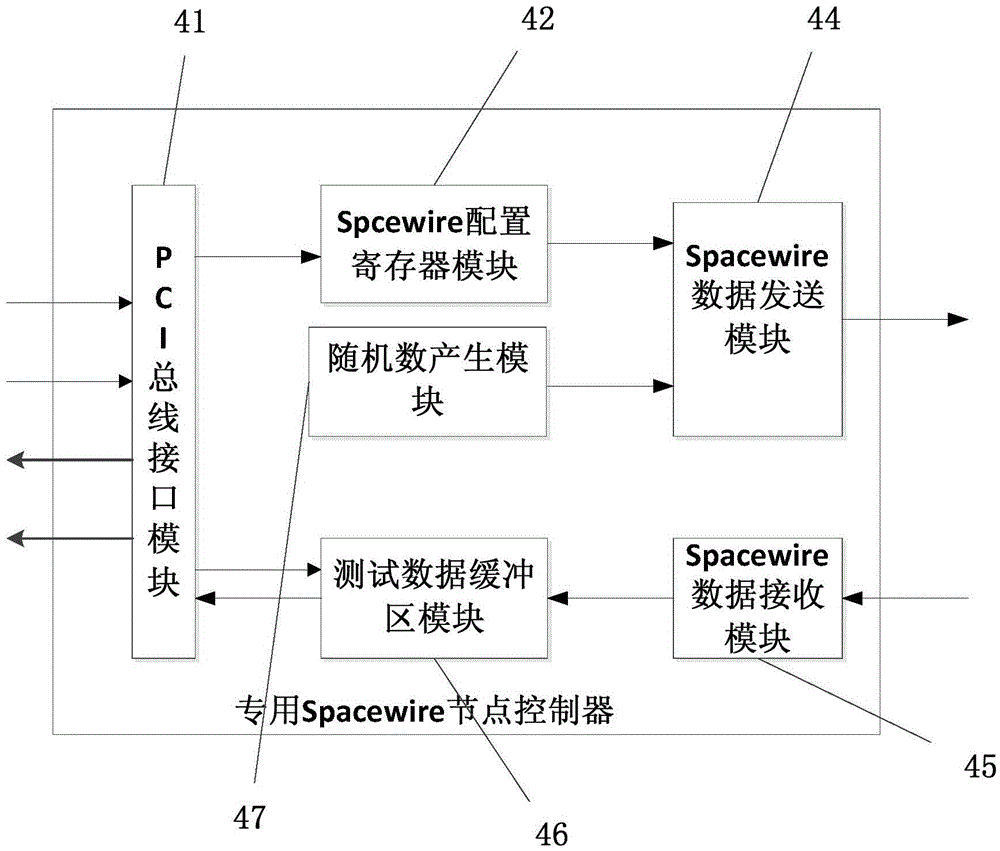

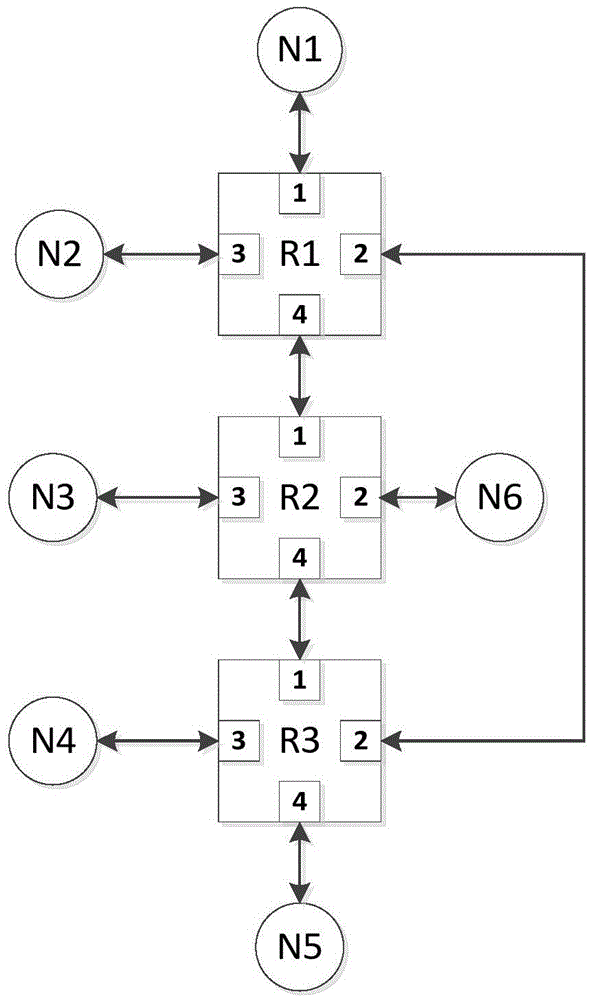

Spacewire network delay testing and optimizing system

ActiveCN105681123AGuaranteed accuracyImprove reliabilityData switching networksInteraction interfaceDependability

The invention provides a Spacewire network delay testing and optimizing system. The Spacewire network delay testing and optimizing system comprises a human-computer interaction interface, a central processing unit, a two-way communication control link based on a PCI bus and a special Spacewire node controller. The central processing unit generates data packets according to configuration parameters input by a user through the human-computer interaction interface, the two-way communication control link based on the PCI bus transmits the data packets to the special Spacewire node controller, the special Spacewire node controller computes delay parameters of each data packet in a Spacewire network in real time, and the central processing unit globally optimizes the Spacewire network according to the delay parameters and provides the obtained optimization result to the human-computer interaction interface. According to the Spacewire network delay testing and optimizing system, a delay test of the Spacewire network is implemented, the tested delay parameters are accurate, the reliability is high, and the real time performance is strong; besides, the to-be-tested Spacewire network is optimized, and if the user optimizes the Spacewire network according to the optimization result, the efficiency of the Spacewire network can be effectively improved.

Owner:北京信息控制研究所 +2

Network system, network apparatus, route change method, and program storage medium storing program thereof

A test packet generator of an entry device generates a delay test packet including priority information. A test packet transmitter of the entry device transmits the delay test packet to an exit device through a route corresponding to the priority information. A test packet receiver of the exit device receives the delay test packet. A reply packet transmitter of the exit device returns a reply-delay test packet toward the entry device through the same route in the counter direction. A reply packet receiver of the entry device receives the reply-delay test packet. A delay calculator of the entry device calculates a delay time on the basis of the time of transmitting the delay test packet and the time of receiving the reply-delay test packet. A route changer of the entry device changes routing appropriately on the basis of the delay time.

Owner:FUJITSU LTD

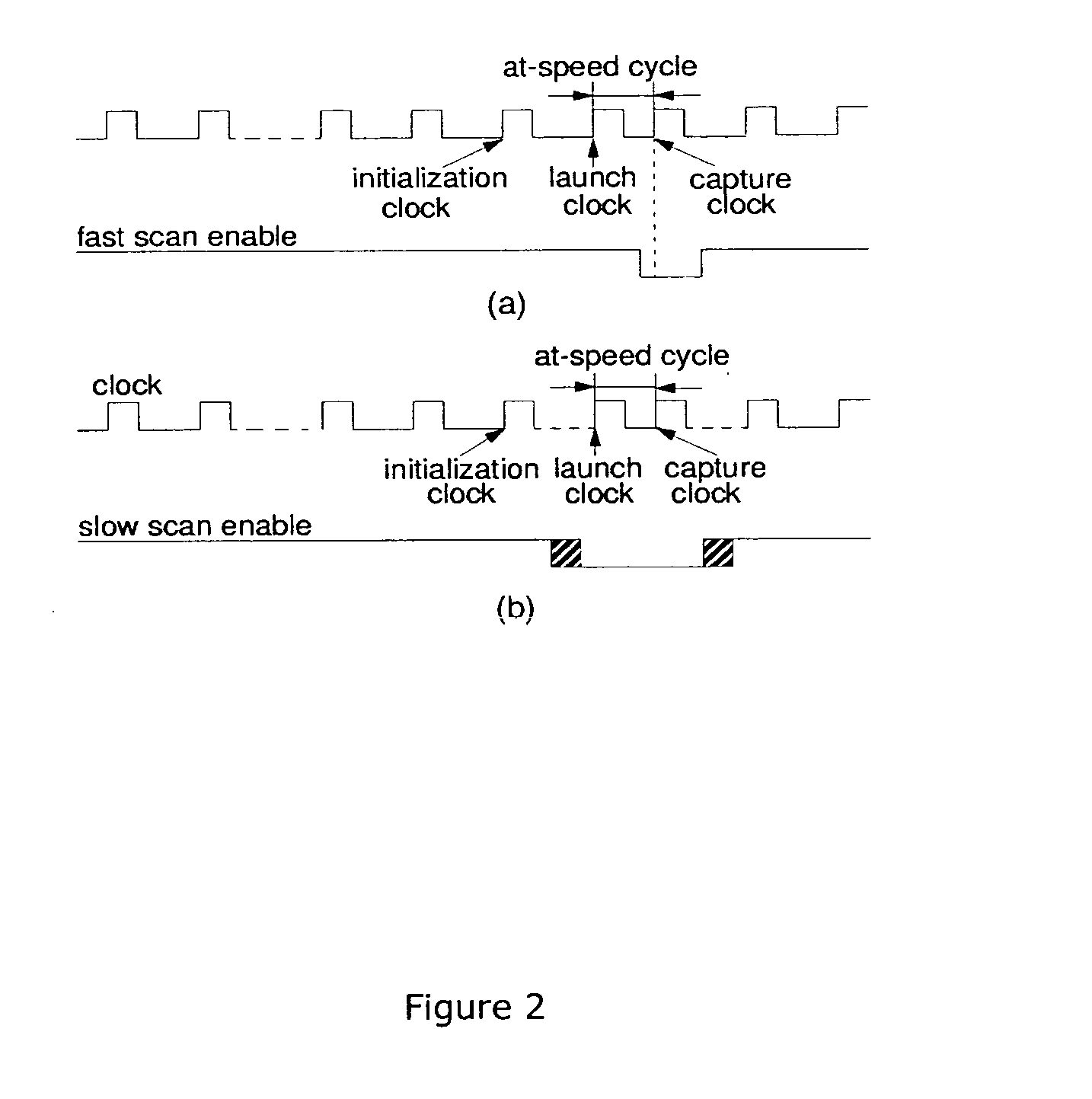

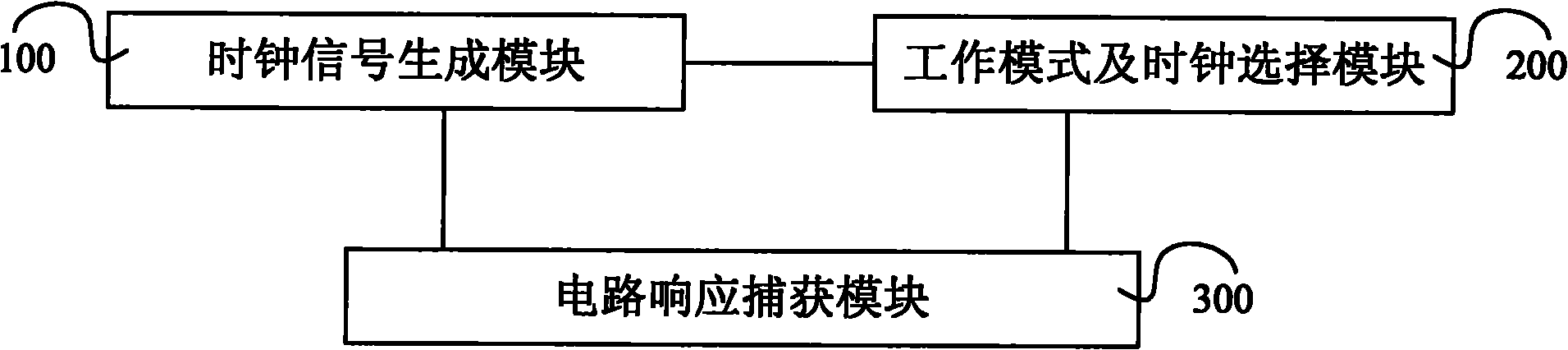

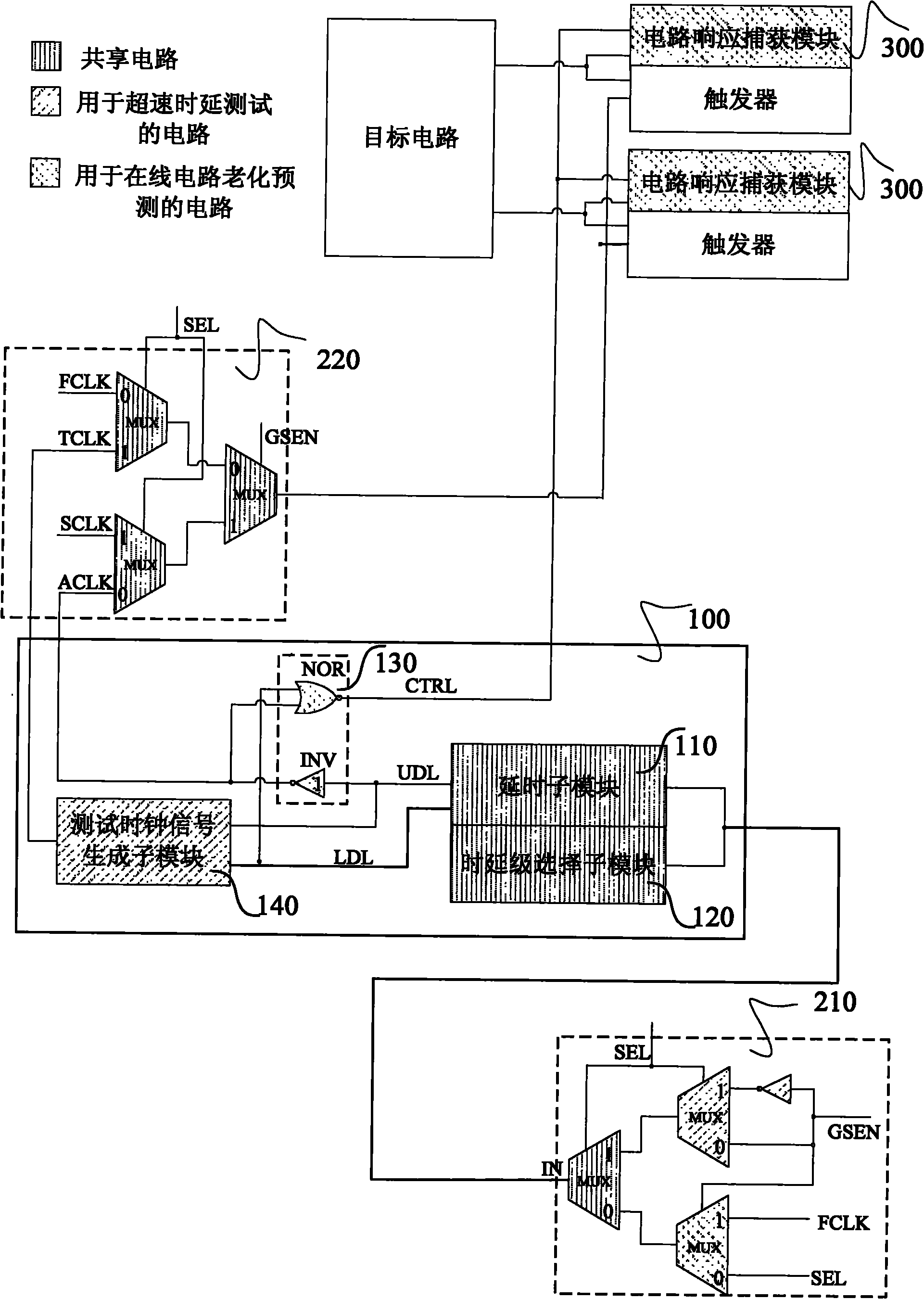

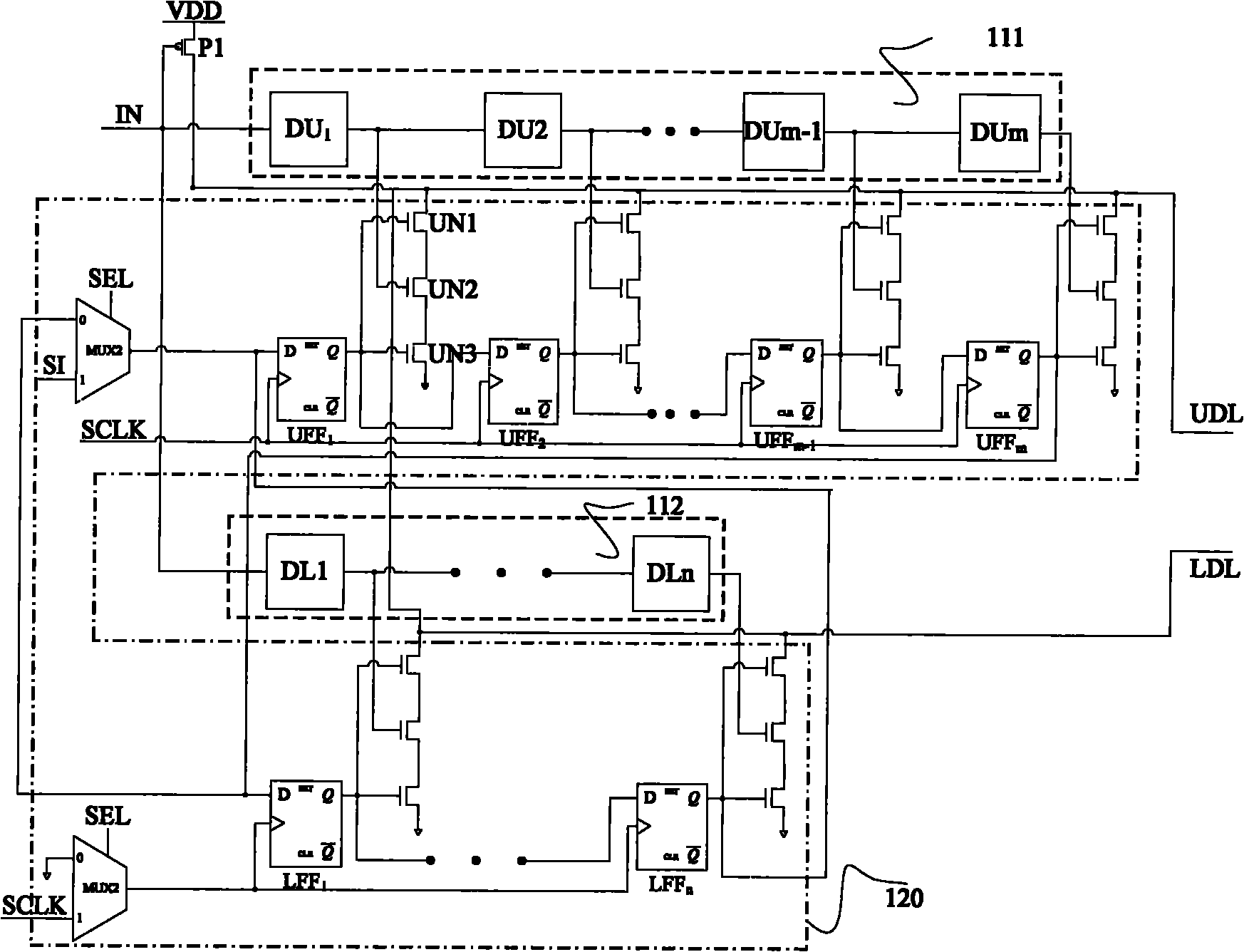

Ageing predetermination and overspeed delay testing bifunctional system and method thereof

ActiveCN101852839AFlexible size adjustmentReduce Clock DriftElectronic circuit testingControl vectorControl signal

The invention relates to an ageing predetermination and overspeed delay testing bifunctional system and method thereof. The system comprises a clock signal generating module, an operating mode and clock selecting module and a circuit response capturing module; wherein the clock signal generating module is used for generating a programmable clock signal according to a first control vector and generating a plurality of test clock signals according to a second control vector; the operating mode and clock selecting module is used for determining the operating mode of the system according to a control signal, selecting a signal among the programmable clock signal, a system functional clock signal and a test clock signal and inputting the selected signal to the system clock tree of a target circuit to carry out operation in corresponding operating mode, and the operating modes include normal operating mode, ageing predetermination mode and overspeed delay testing mode; and the circuit response capturing module is used for capturing the response of the target circuit in the capturing interval when the current mode is the ageing predetermination mode and is also used for generating a corresponding alarm signal according to the fact that whether signal step appears in the capturing interval. The invention can carry out overspeed delay testing and online circuit ageing predetermination.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

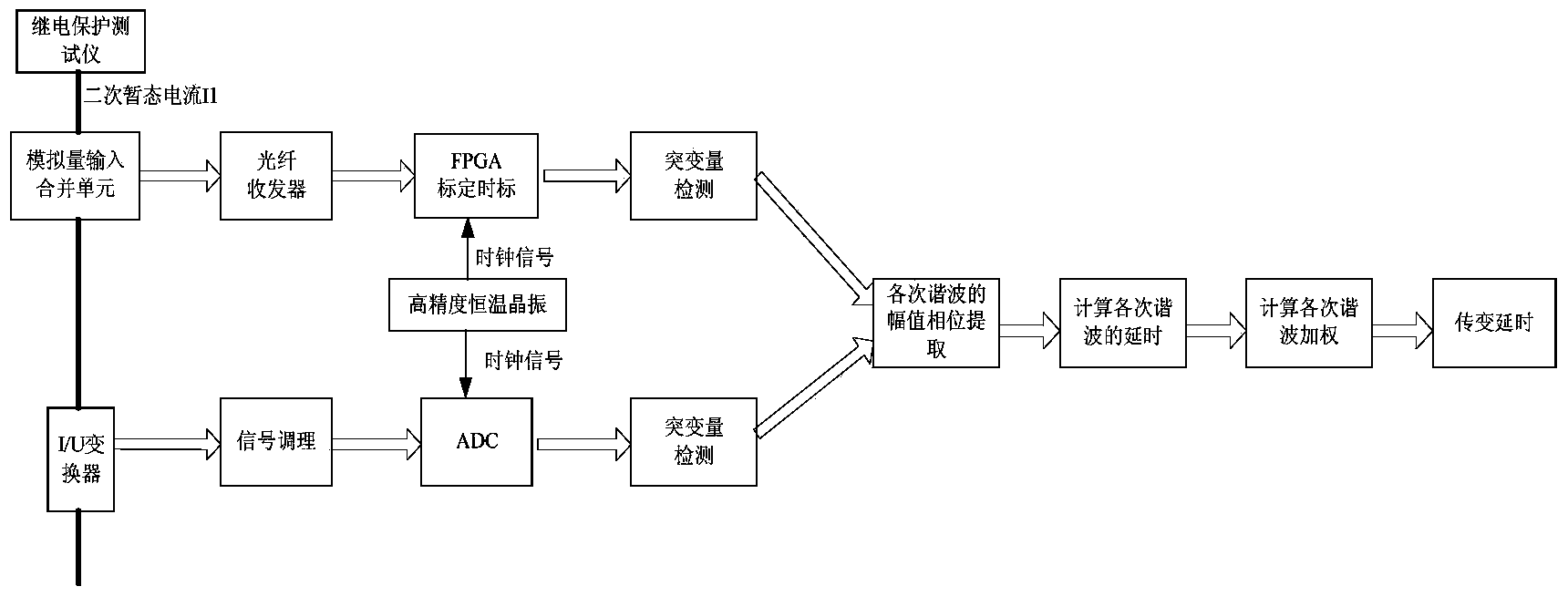

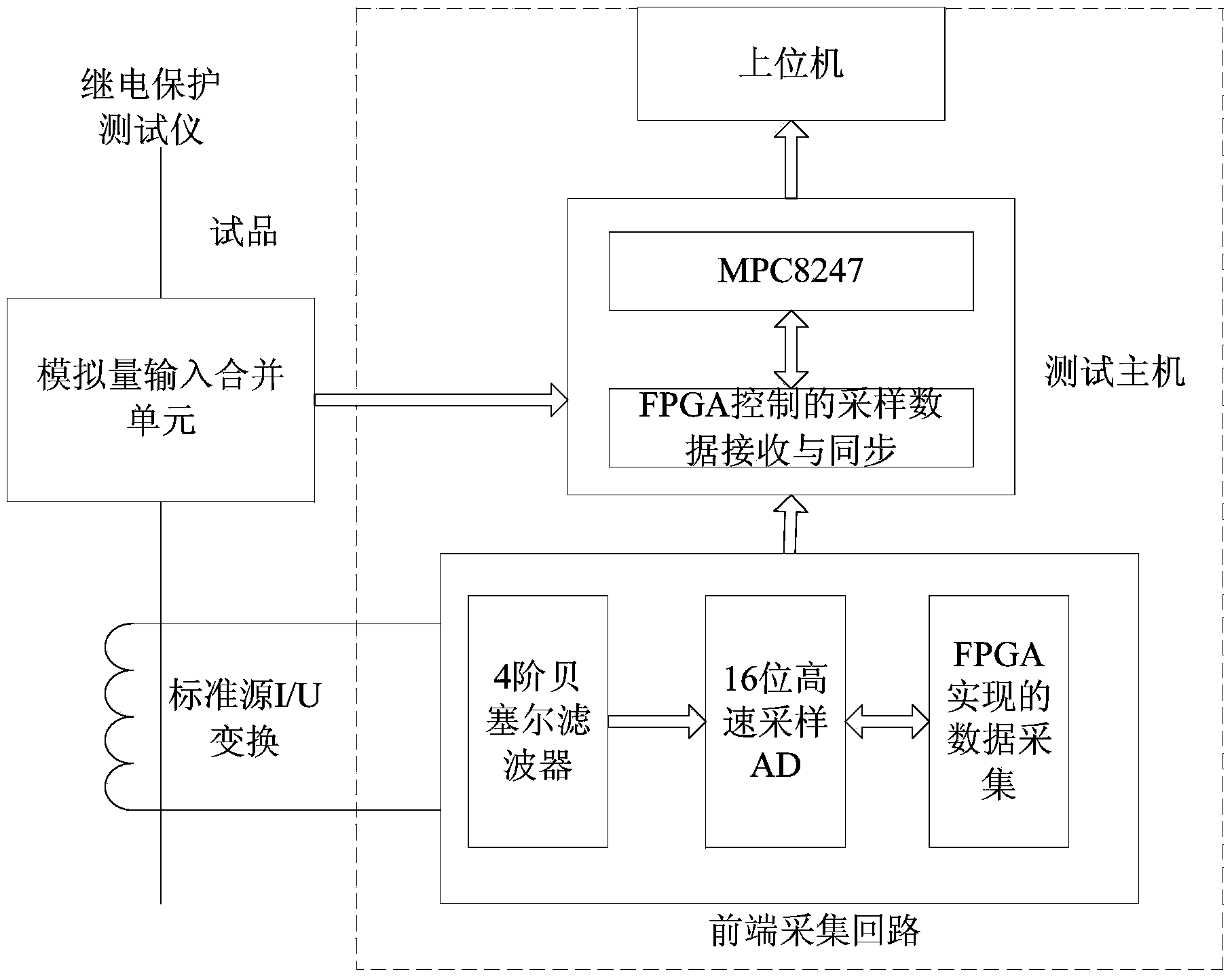

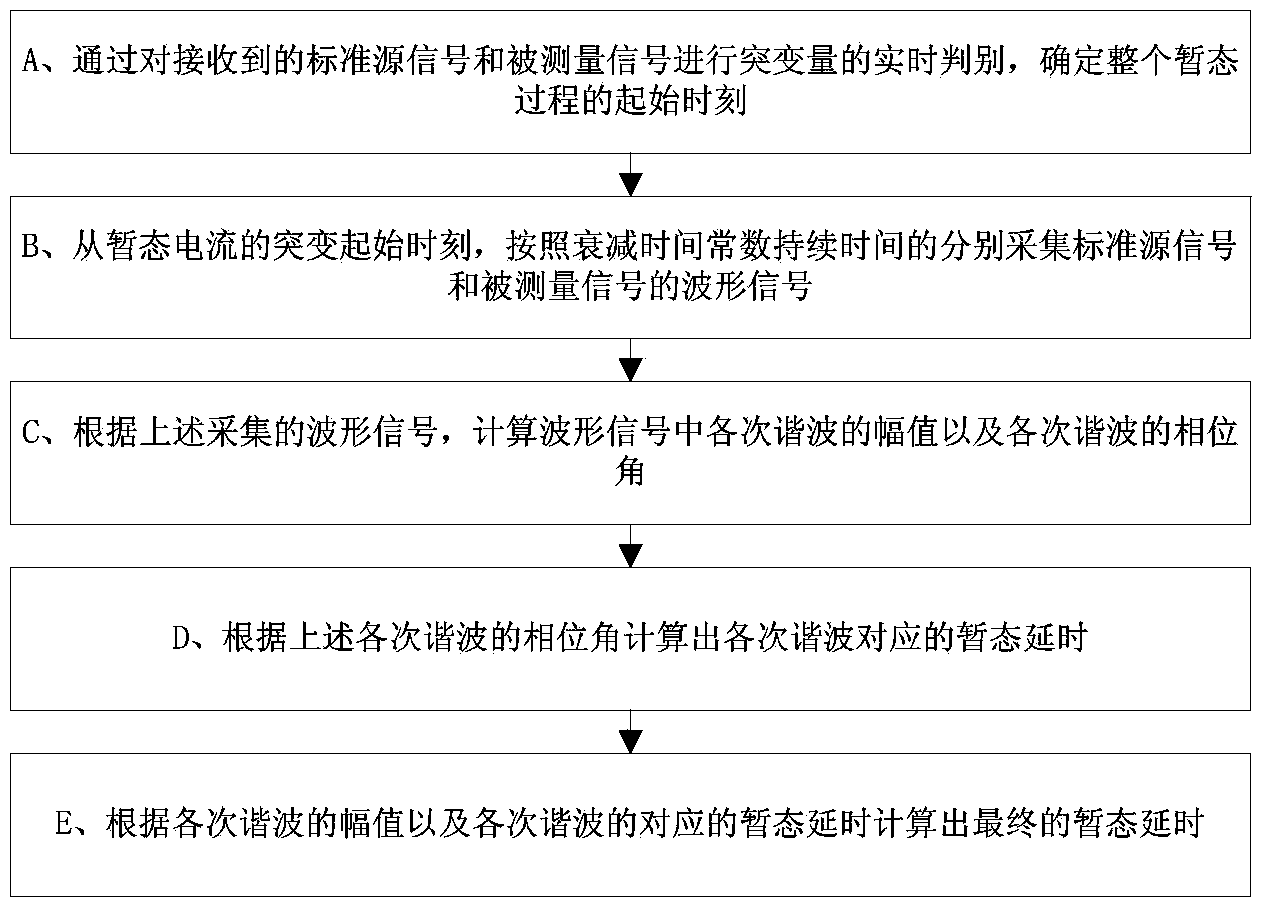

Analog quantity merging unit transient state delay test method based on frequency scanning

ActiveCN104007346AImprove sampling accuracyImprove general performanceElectrical testingTransient stateLow-pass filter

The invention discloses an analog quantity merging unit transient state delay test method based on frequency scanning. Sudden-change quantities of a received standard source signal and a signal to be measured are judged in real time, a starting moment of a transient state process is determined, waveform signals are collected, the amplitude and the phase angle of each harmonic are calculated, the transient state delay corresponding to each harmonic is calculated, and ultimately, the ultimate transient state delay is calculated according to the amplitude of each harmonic and the transient state delay corresponding to each harmonic. Transient state transmission time is calculated through a weighting coefficient, test currents do not need to be output specially, universality is high, and the method is suitable for all merging units with low-pass filter coefficients, port modes and port protocols currently. A high-precision constant-temperature crystal oscillator is used for controlling timing sequence and eliminating errors, the transient state starting moment of tested data is guaranteed, and sampling precision of higher harmonics is improved by means of a four-step Bessel filter. The analog quantity merging unit transient state delay test method based on frequency scanning can be widely used in the field of relay protection and verification.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD +2

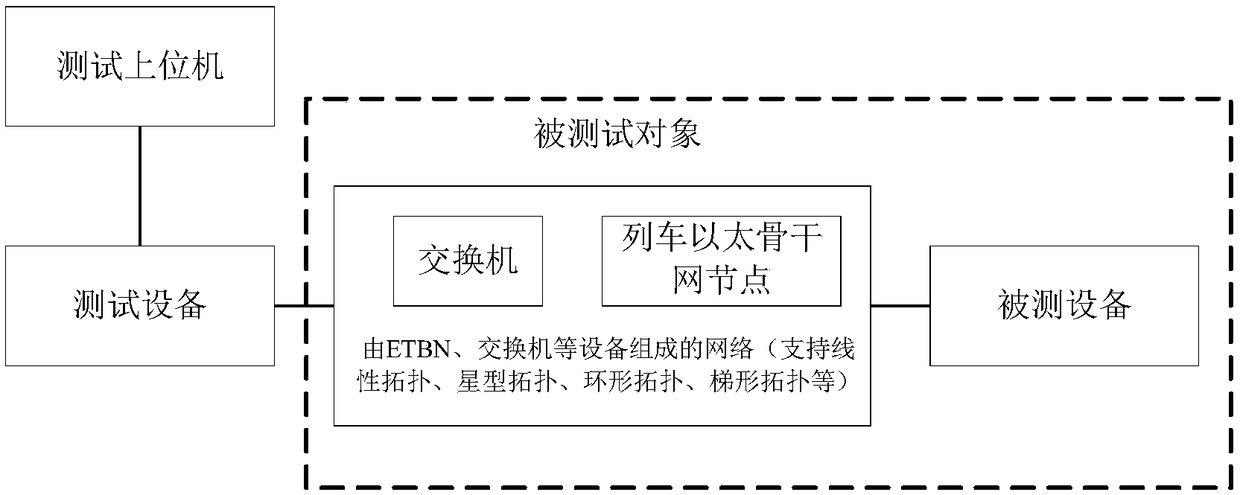

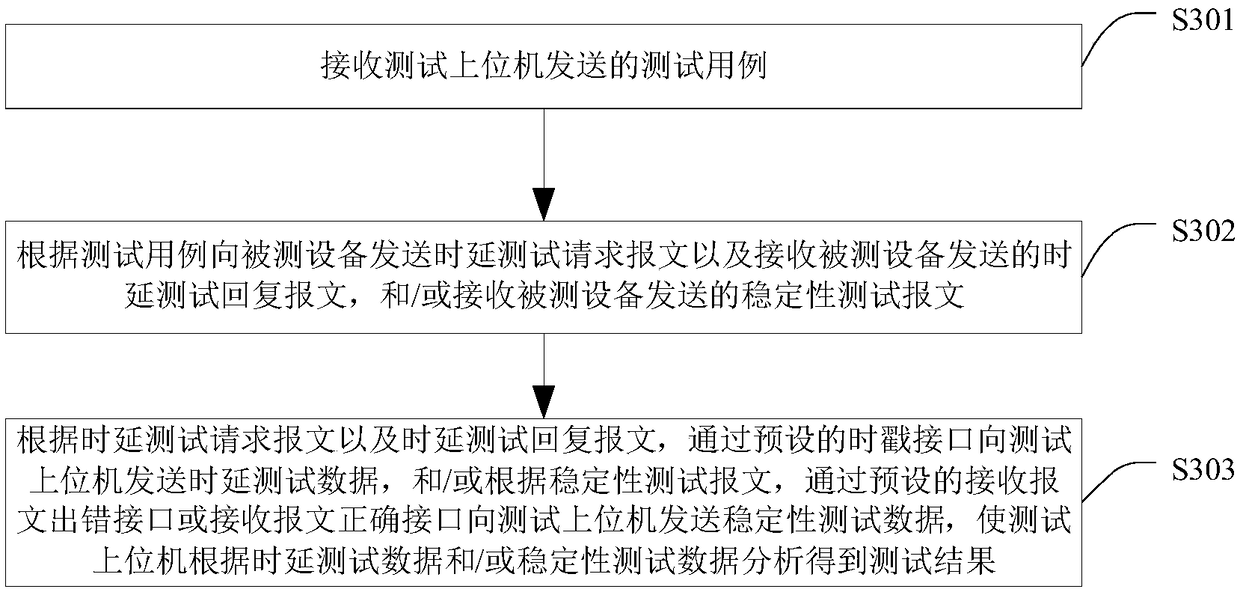

Real-time Ethernet device performance test method, device and system

ActiveCN109194551AImplement performance testingImplementation LatencyData switching networksTimestampEquipment under test

The present invention provides a real-time Ethernet device performance test method which is applied to a test device. The method comprises the steps of: receiving a test example sent by a test upper computer; according to the test example, sending a delay test request message to a monitored device, receiving a delay test reply messages sent by the monitored device, and / or receiving a stability test message sent by the tested device; according to the delay test request message and the delay test reply message, sending delay test data to the test upper computer through a preset timestamp interface, and / or according to the stability test message, sending stability test data to the test upper computer through a preset interface message error interface or a receiving message correction messageto allow the test upper computer to perform analysis to obtain a test result according to the delay test data and / or the stability test data. The method provided by the invention achieves the Ethernetstability device and the delay test of the monitored device and mainly a terminal-type device.

Owner:上海仁童电子科技有限公司

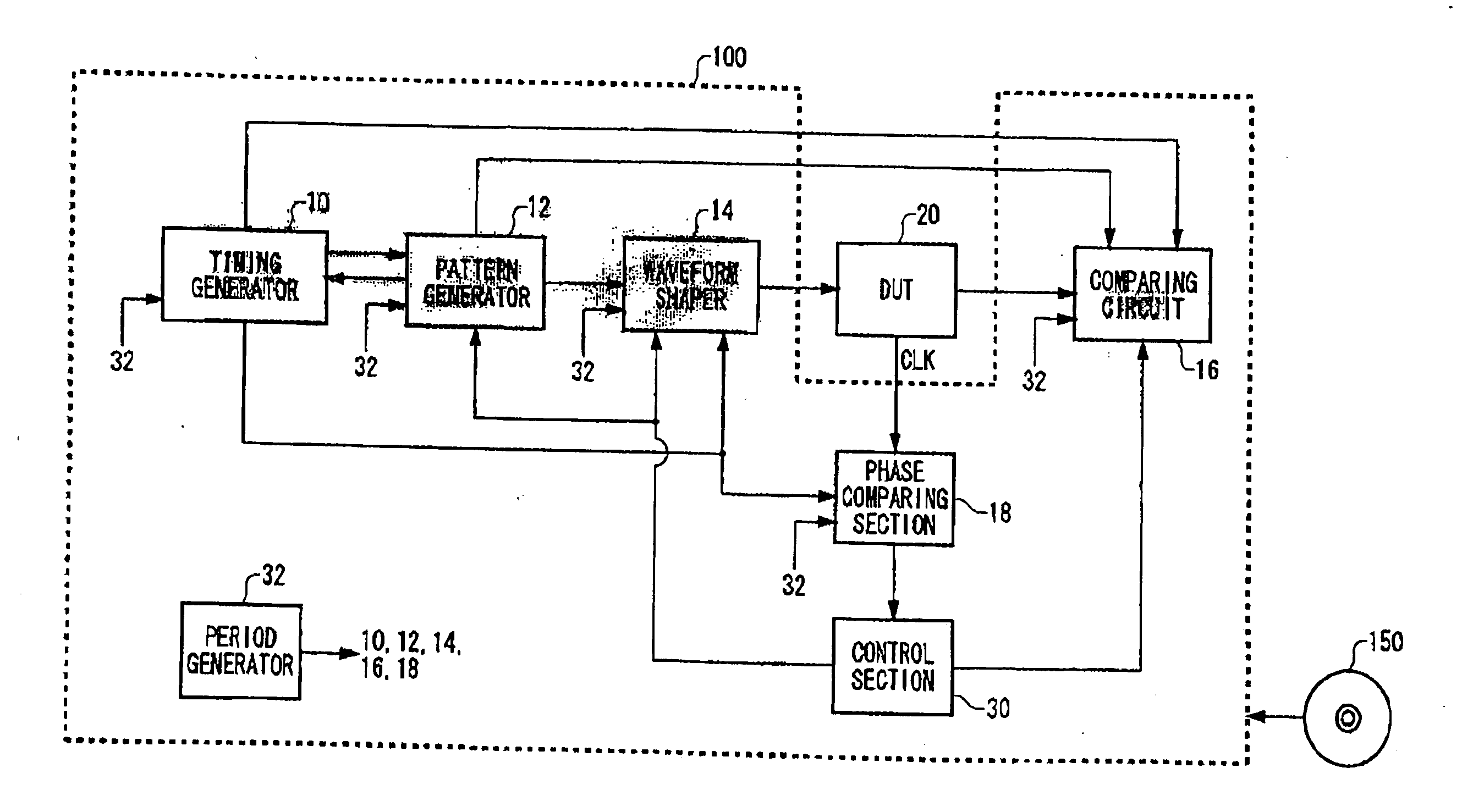

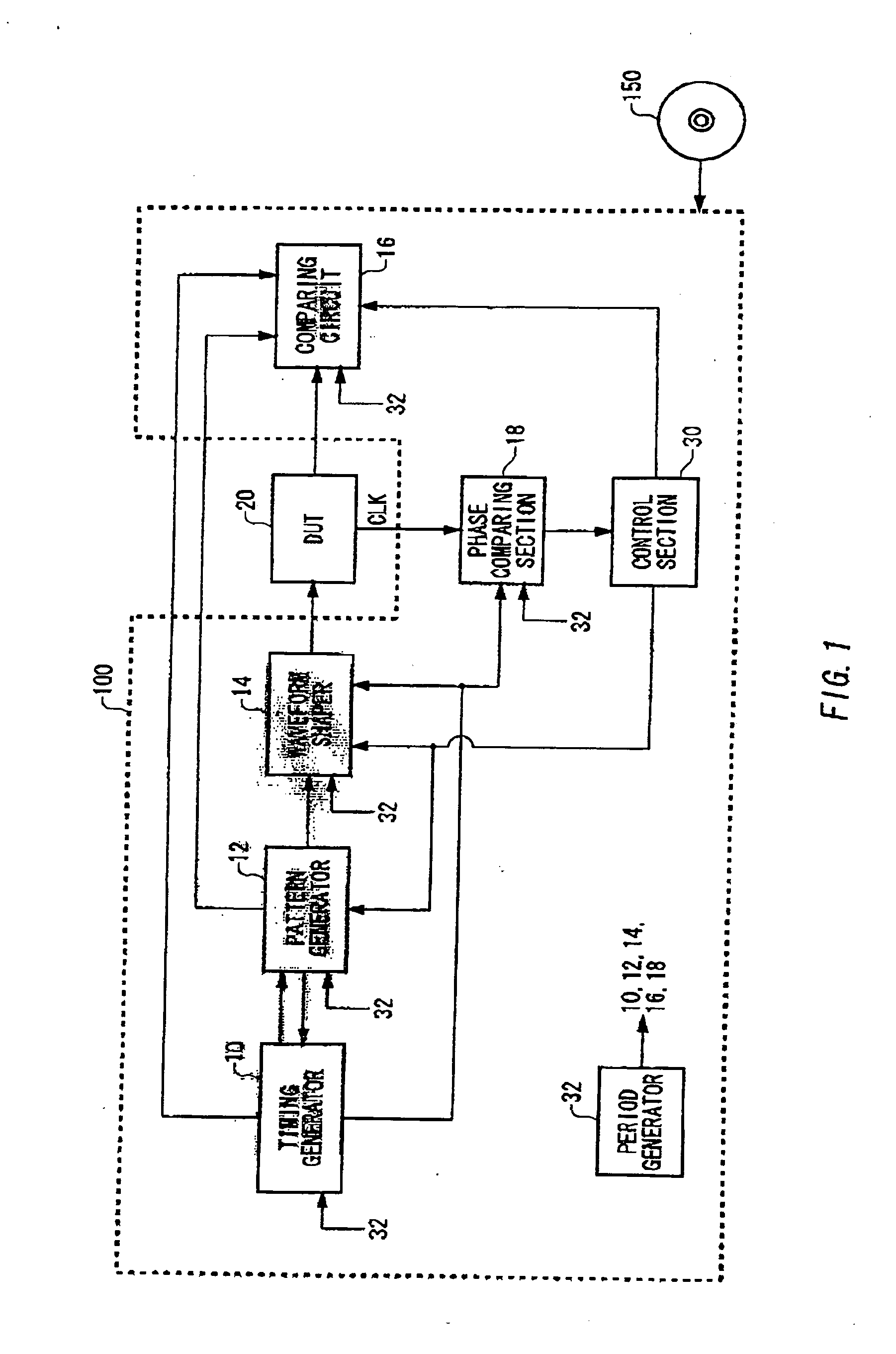

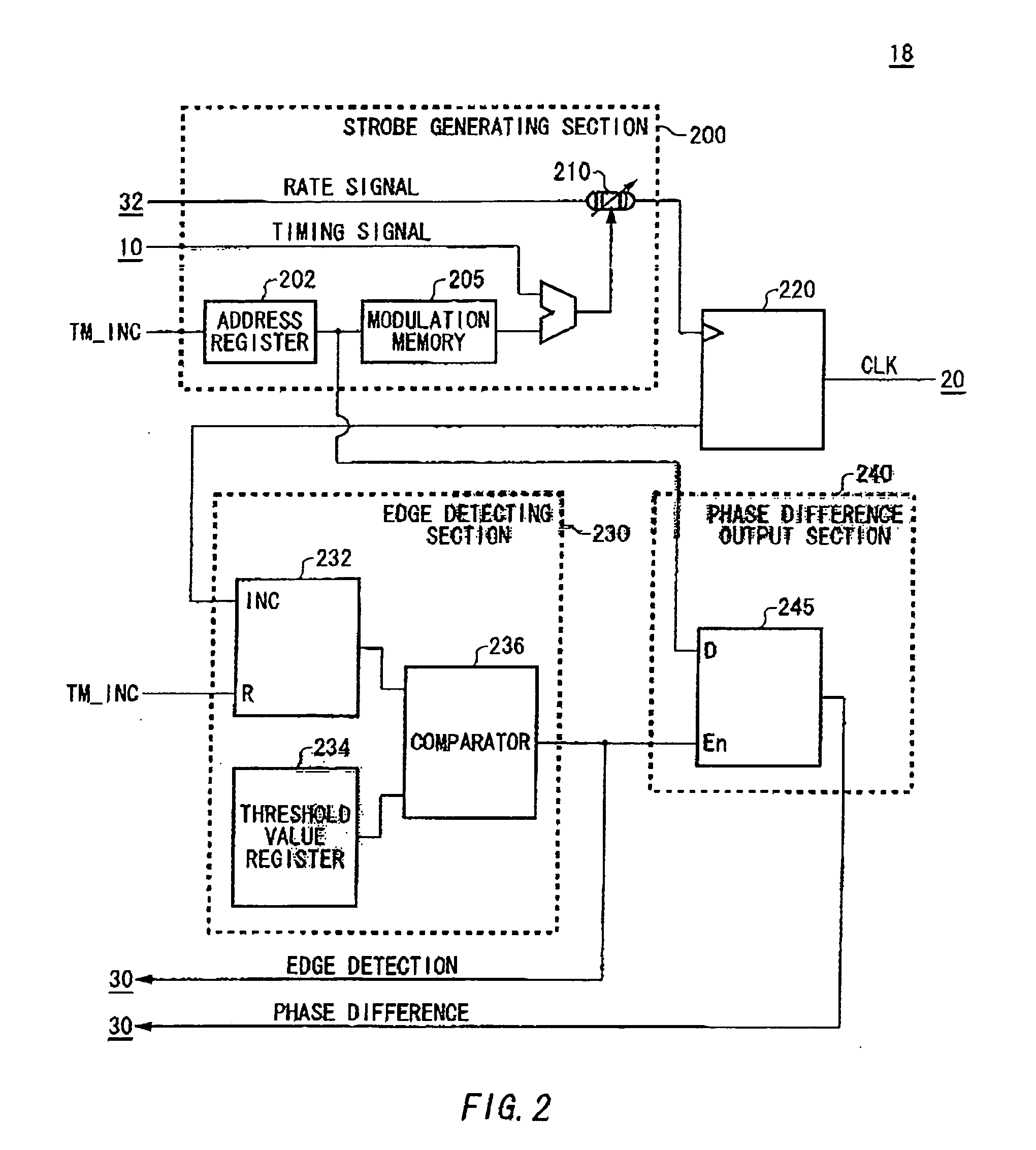

Test apparatus, test method, and program

InactiveUS20070266290A1Noise figure or signal-to-noise ratio measurementElectronic circuit testingEquipment under testPhase difference

There is provided a test apparatus that tests a device under test. The test apparatus includes a period generator that generates a rate signal determining a test period according to an operating period of the device under test, a phase comparing section that inputs an operational clock signal for the device under test generated from the device under test and detects a phase difference between the operational clock signal and the rate signal using the rate signal as a standard, a test signal generating section that generates a test signal to be supplied to the device under test in synchronization with the rate signal, a delaying section that delays the test signal in accordance with the phase difference to substantially synchronize the delayed signal with the operational clock signal, and a test signal supplying section that supplies the delayed test signal to the device under test.

Owner:ADVANTEST CORP

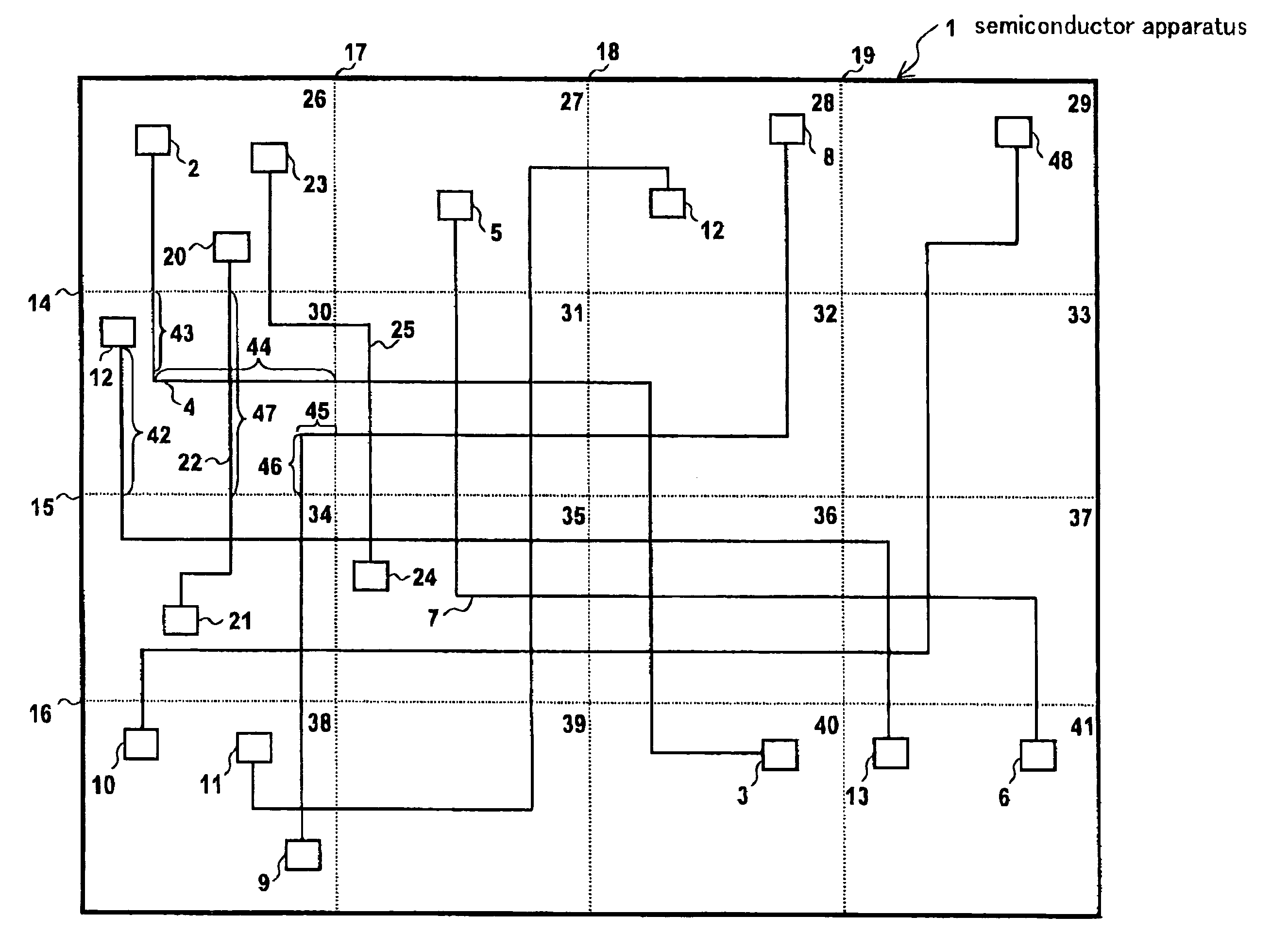

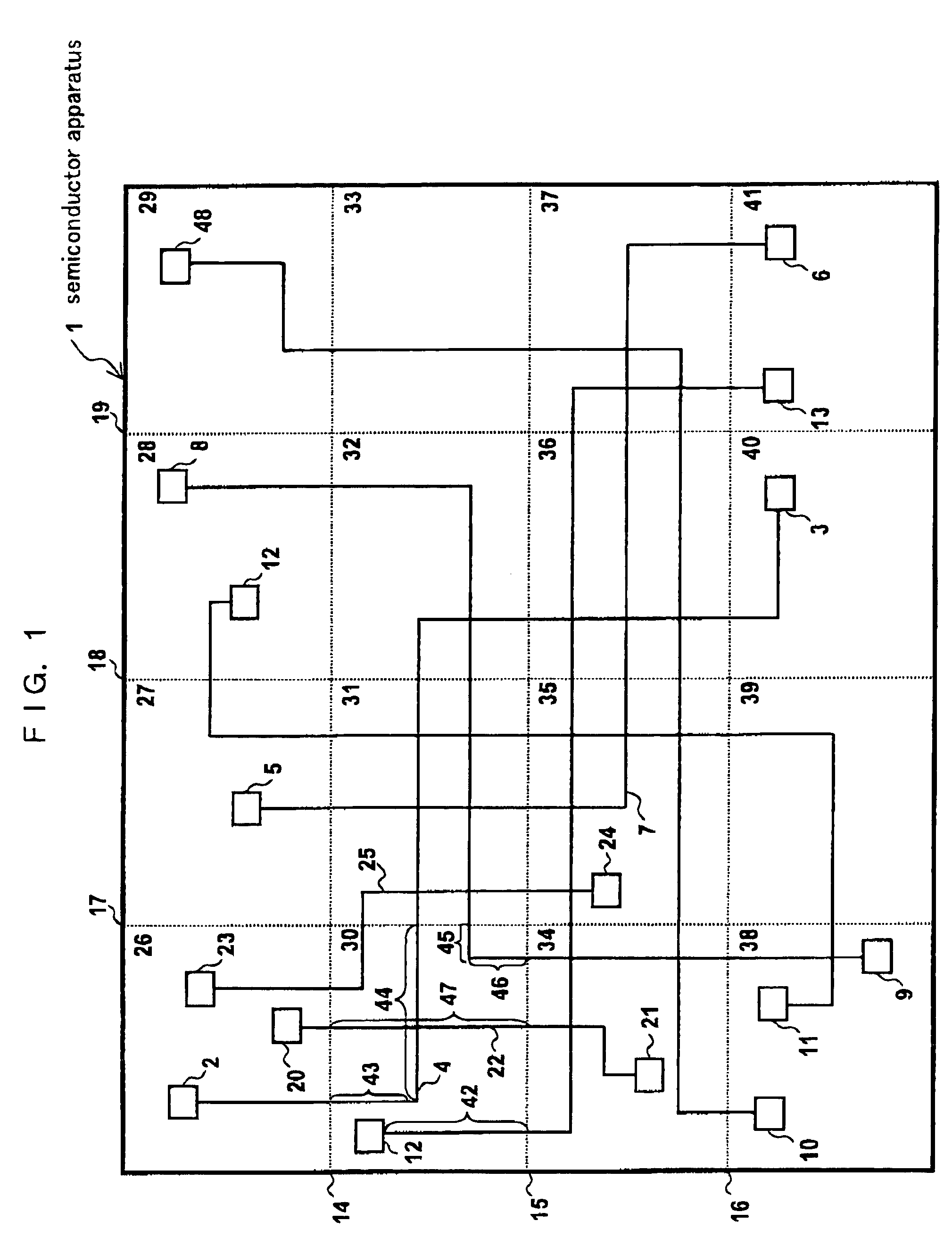

Method of testing semiconductor apparatus

InactiveUS7290183B2Precise screeningElectronic circuit testingSolid-state devicesProcessor registerDelayed time

A method of testing a semiconductor apparatus includes a step of dividing a region in the semiconductor apparatus into a plurality of divided regions, a step of extracting all of paths starting at registers and terminating at other registers present in the respective divided regions as candidate paths, a step of calculating delay times in signal transmissions of the candidate paths and selecting the candidate path having a maximum delay time in each divided region as a critical path, and a step of conducting a delay test for the critical path in each divided region to thereby accurately screen the semiconductor apparatus.

Owner:SOCIONEXT INC

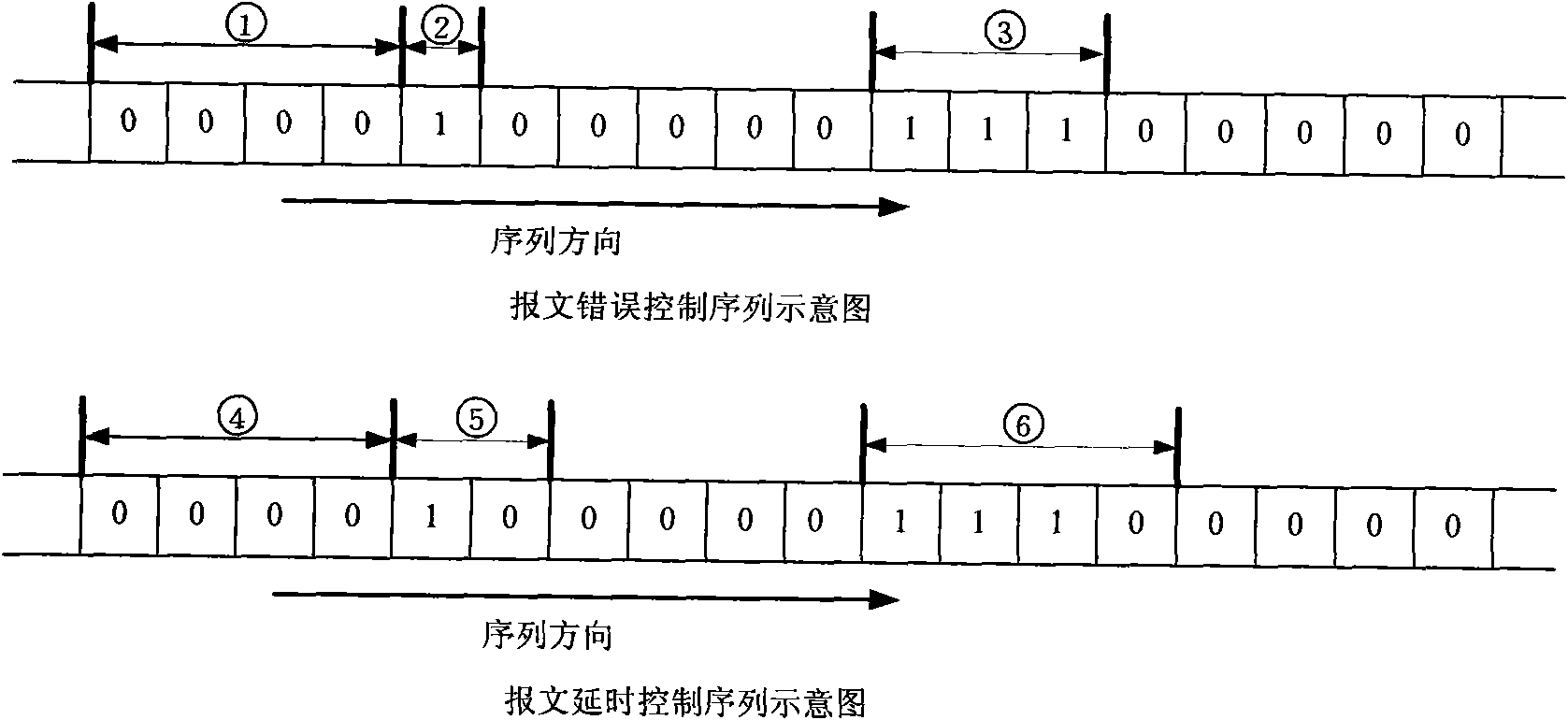

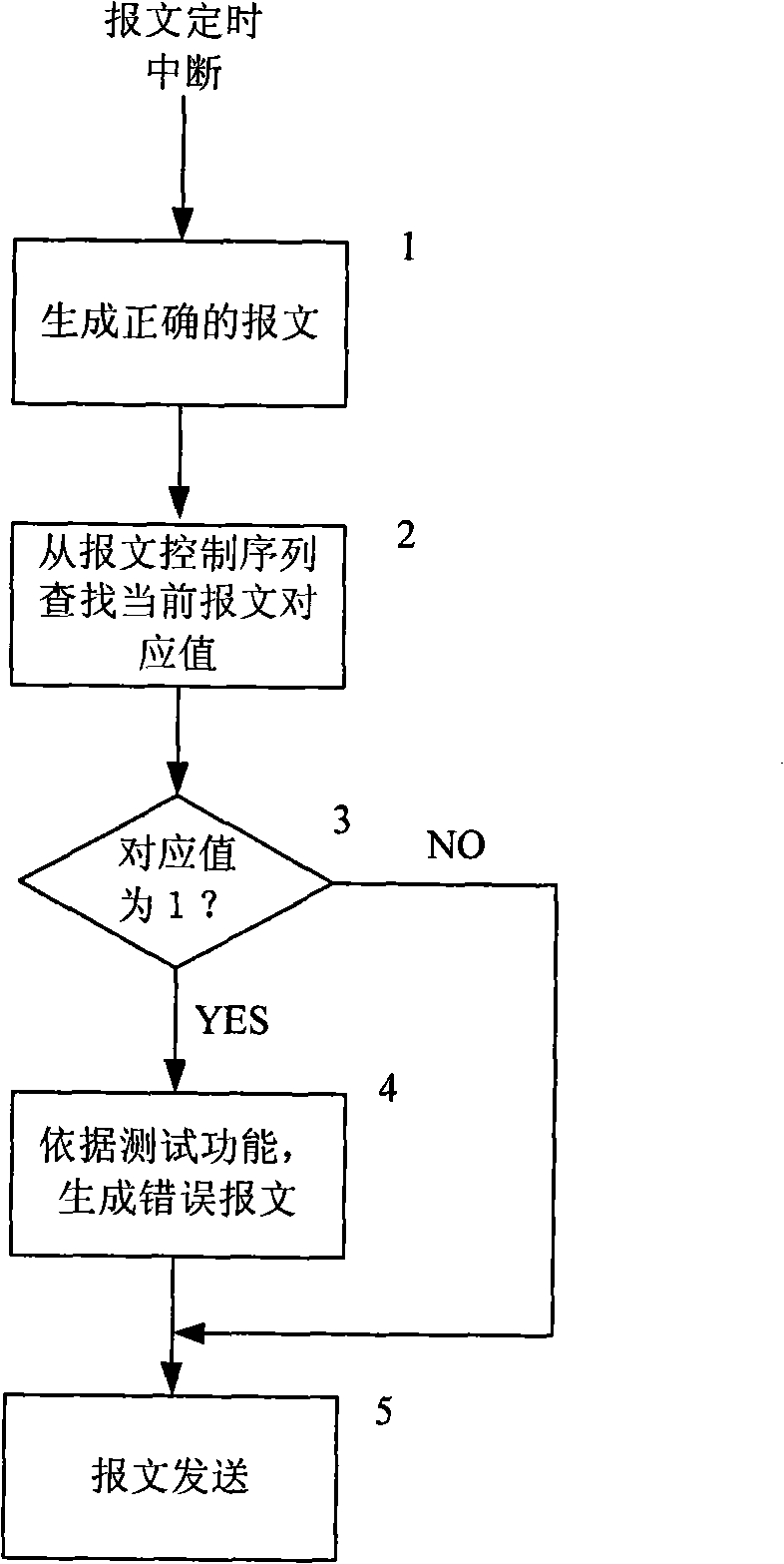

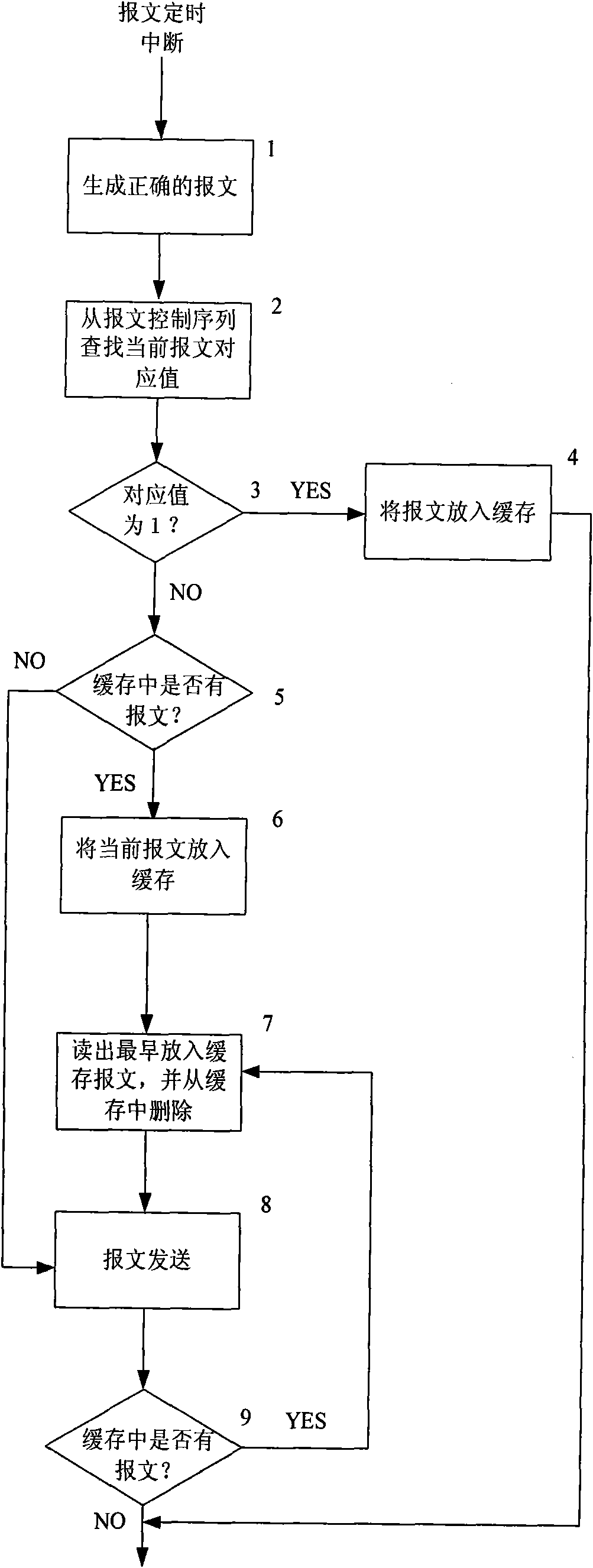

Negative testing method applicable to standard and digital relay protective devices

ActiveCN101582844AThe method is simpleSimple methodData switching networksTester deviceProficiency testing

The invention relates to a negative testing method applicable to standard and digital relay protective devices, which is characterized by simulating possible abnormal conditions in a data interaction process of a digital relay protection device according to the configuration of a user and testing the abnormal condition handling capacities of the digital relay protection device, wherein abnormal condition handling capacities comprise a capacity for handling test message destination address errors and data errors and a capacity for handling delayed test message transmission. The test of whether a digital protection device has an abnormal optical fiber communication condition handling capacity under a condition of sound operation of optical fibers in an initial test stage is difficult, so artificially simulation of abnormal optical fiber communication conditions is necessary for testing the abnormal optical fiber communication condition handling capacity of the digital protection device. Through the customization of output messages of a digital relay protection tester, possible abnormal communication conditions can be simulated artificially, so the problem of testing the abnormal communication condition handling capacity of the digital relay protection device is solved.

Owner:JIANGSU WISCOM TECHNOLOGY CO LTD

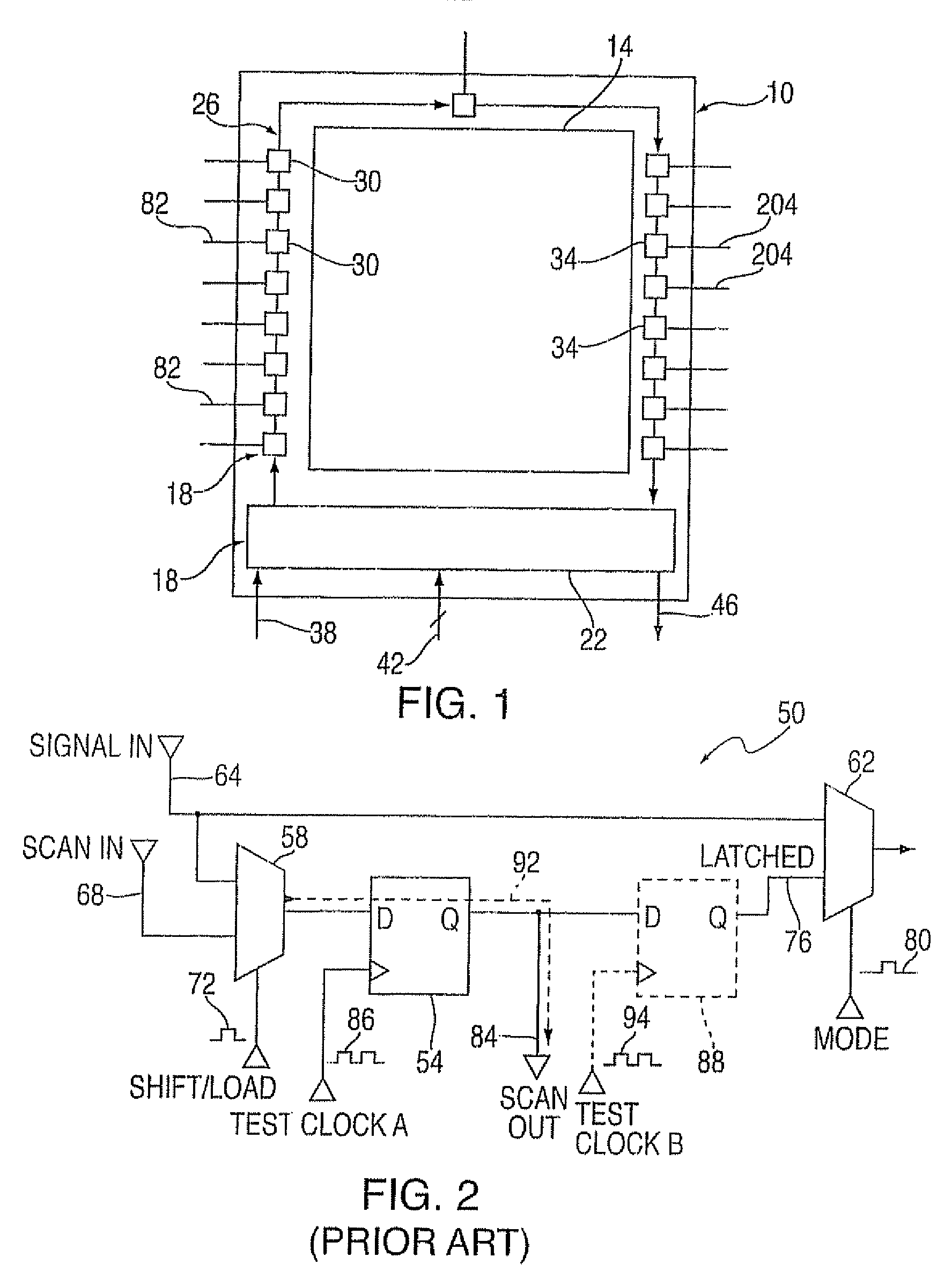

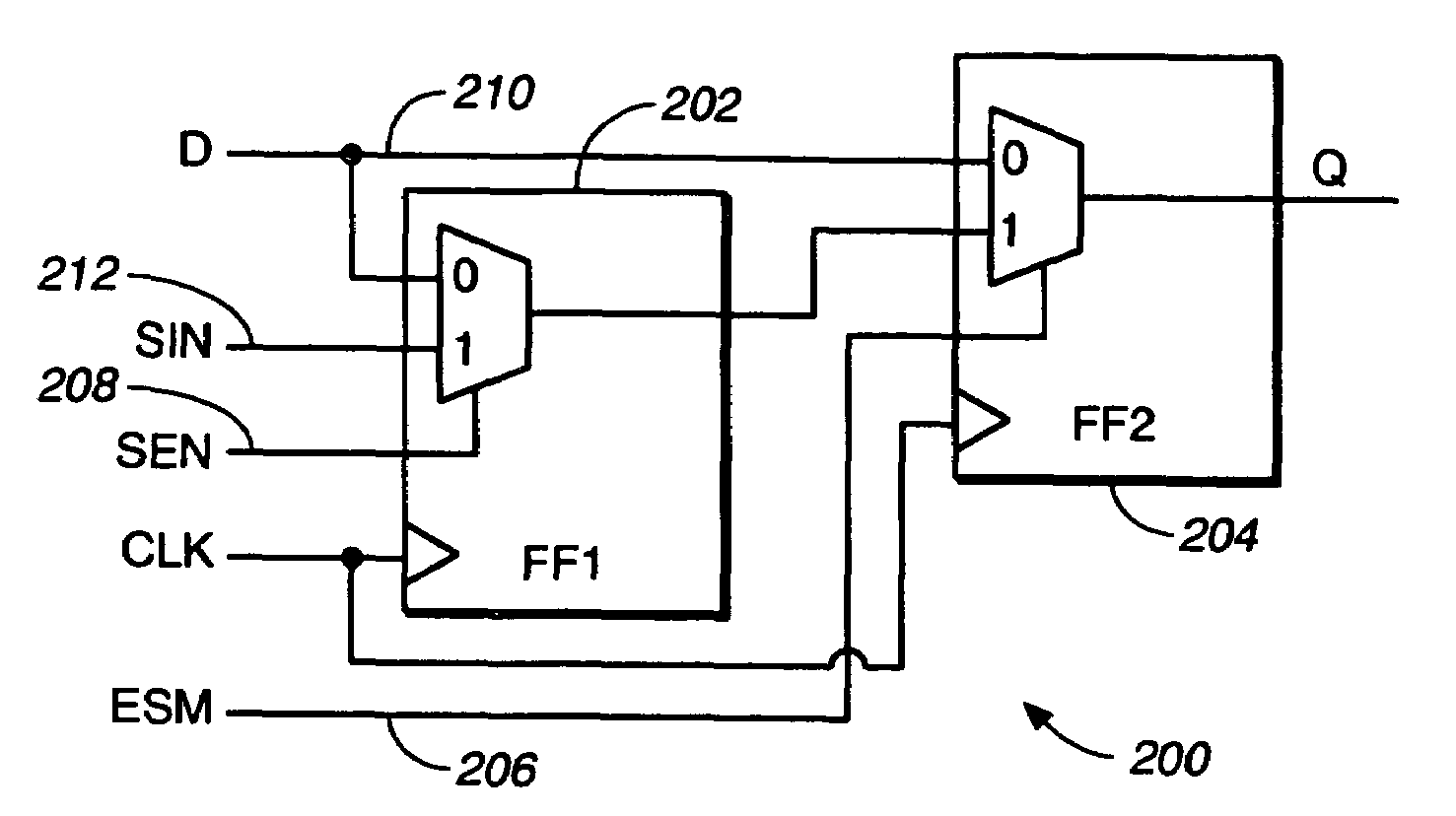

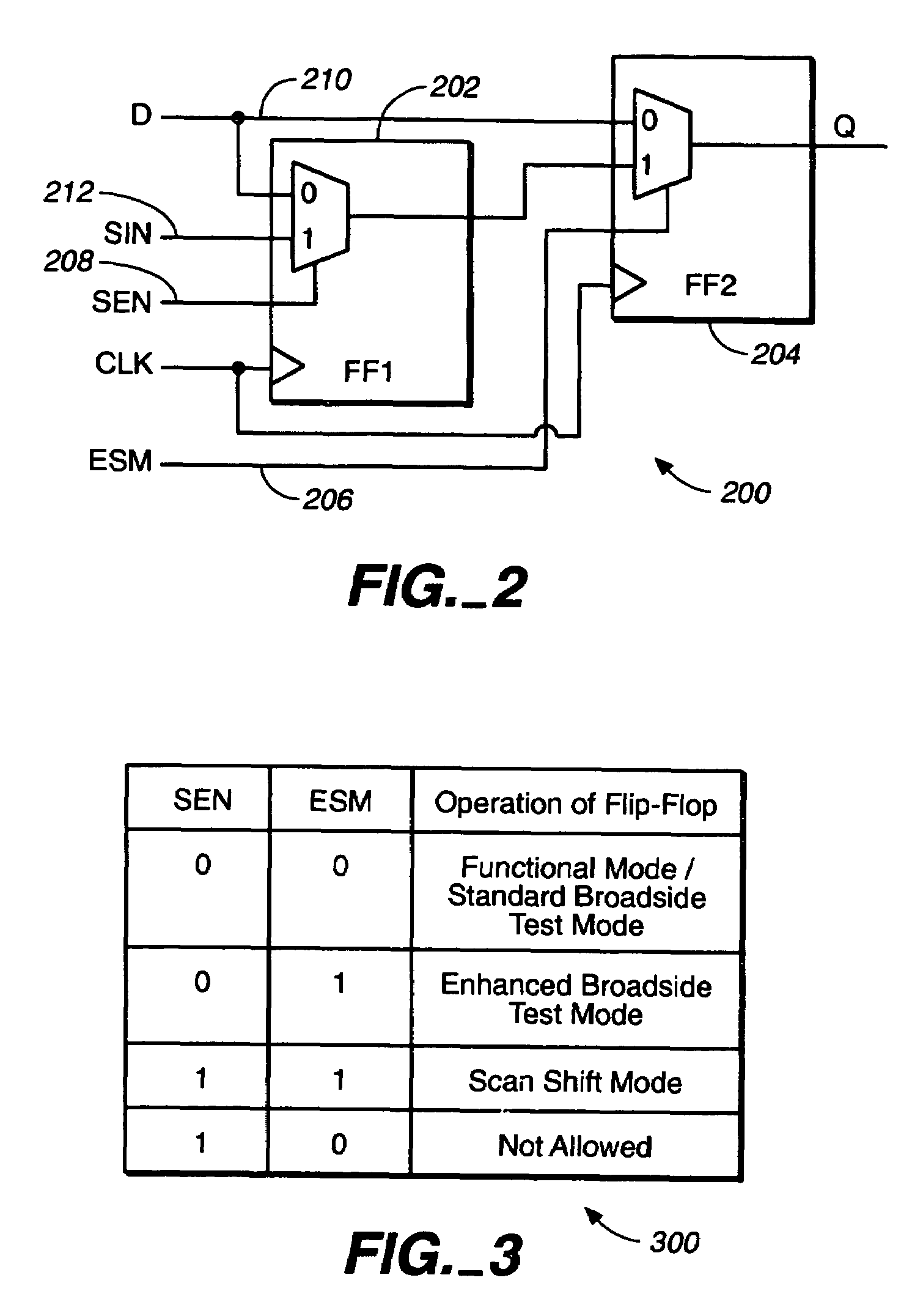

System and method for improving transition delay fault coverage in delay fault tests through use of an enhanced scan flip-flop

InactiveUS7461307B2Expand coverageTransition delay test coverage may be improvedElectronic circuit testingFault coveragePort triggering

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

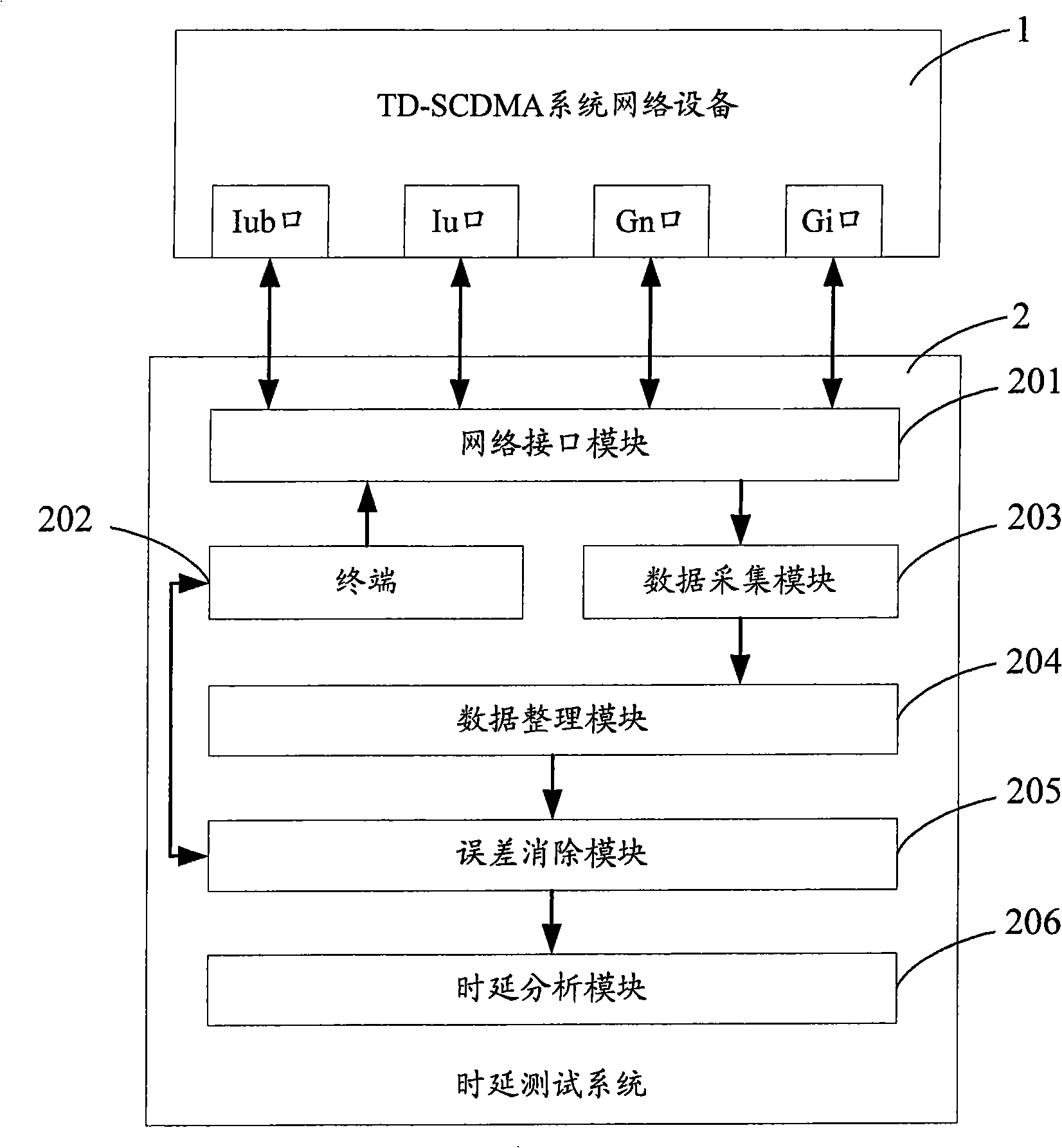

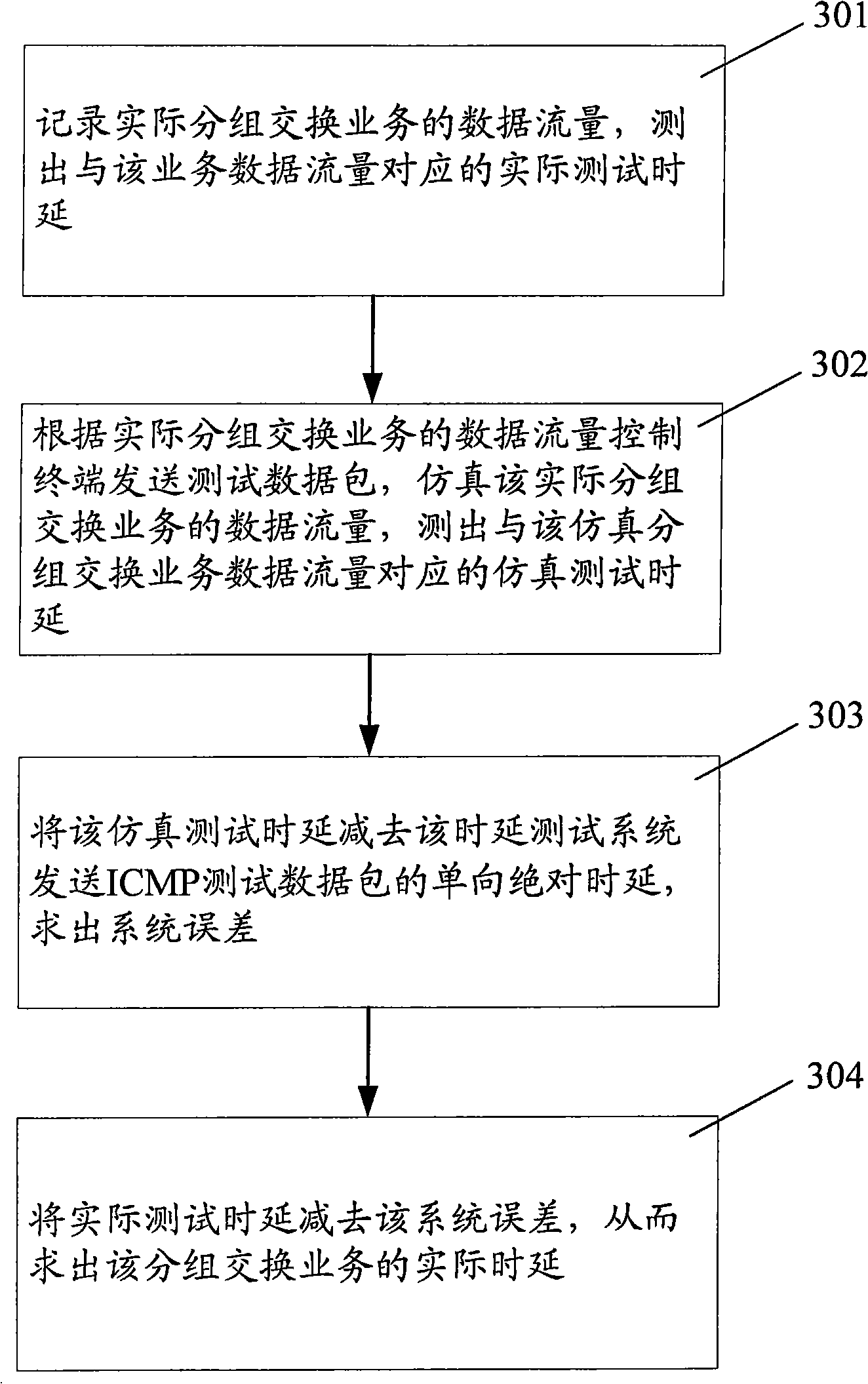

System for data traffic delay time test and error cancelling method

ActiveCN101316151AOvercome the disadvantage of being unable to accurately unify the time reference pointOvercoming the disadvantages of time errorError preventionData switching by path configurationTime delaysData acquisition

The invention discloses a data service time delay testing system, which includes a network interface module, a terminal, a data acquisition module, a data reduction module and an error elimination module. The invention also discloses a method for eliminating the error during the data service time delay test, the method records the data traffic of the PS service and measures the actual time delay; a test data package simulating the data traffic of the PS service is transmitted by the terminal according to the data traffic of the actual PS service to test the time delay of the simulation test; the systematic error can be obtained by subtracting the one-way absolute time delay when the time delay testing system transmits the test data package from the time delay of the simulation test; then the actual time delay of the PS service can be obtained by subtracting the systematic error from the time delay of the actual test. The invention enables the customer to accurately measure the data time delay of the PS service in the TD-SCDMA system, which can provide precise analysis and positioning basis for the QOS problem during the application of the PS service.

Owner:DATANG MOBILE COMM EQUIP CO LTD

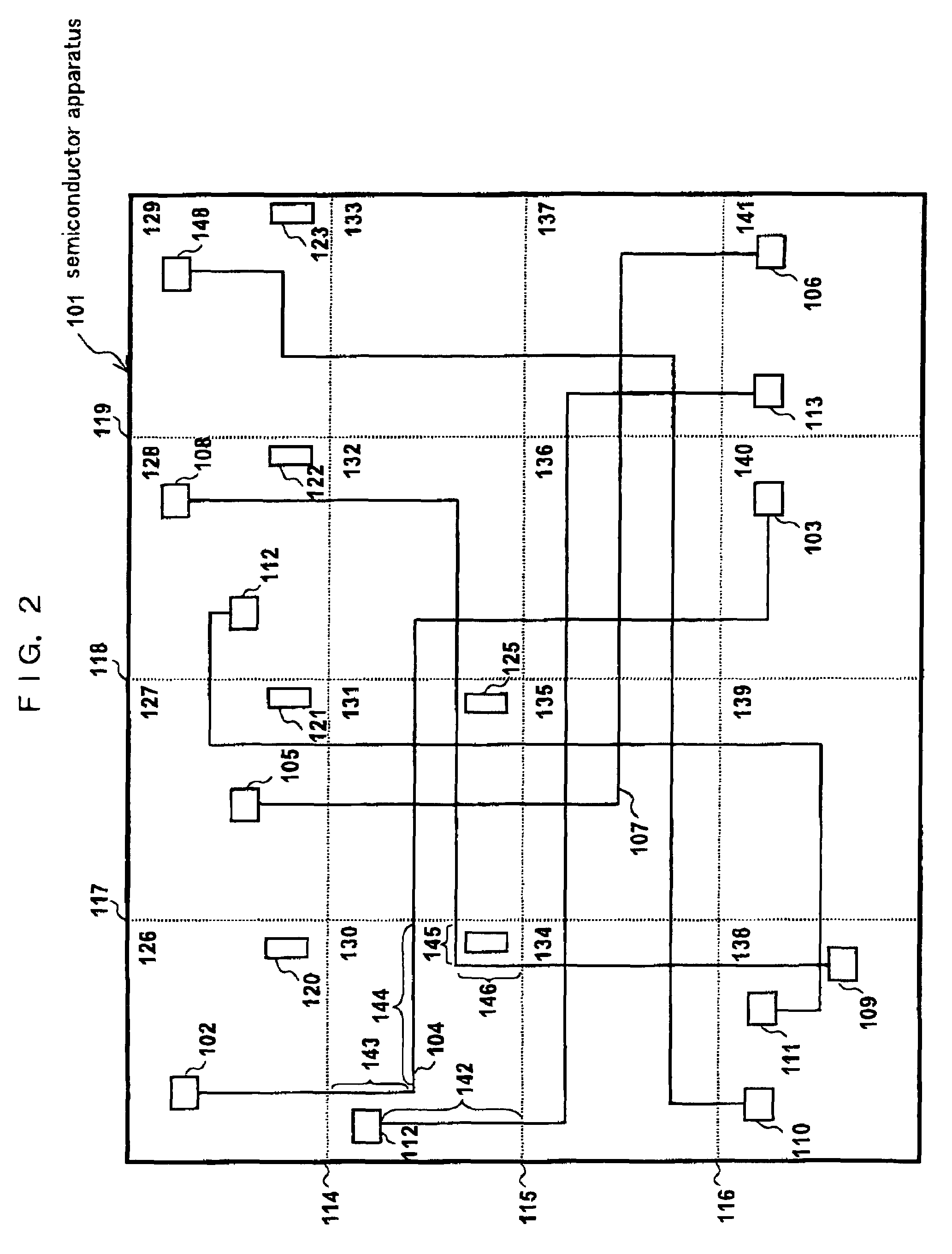

Semiconductor device

InactiveUS20080231313A1Measurement accuracyImprove reliabilityReliability increasing modificationsElectrical testingData signalEngineering

A semiconductor device according to the present invention includes an internal circuit executing a predetermined processing based on signal input from an external device, an output buffer driving line connected to an output terminal based on signal output from the internal circuit, a feedback line branched off from signal line in buffer transmitting data signal to an output stage circuit of the output buffer, and a delay test circuit connected to the feedback line.

Owner:RENESAS ELECTRONICS CORP

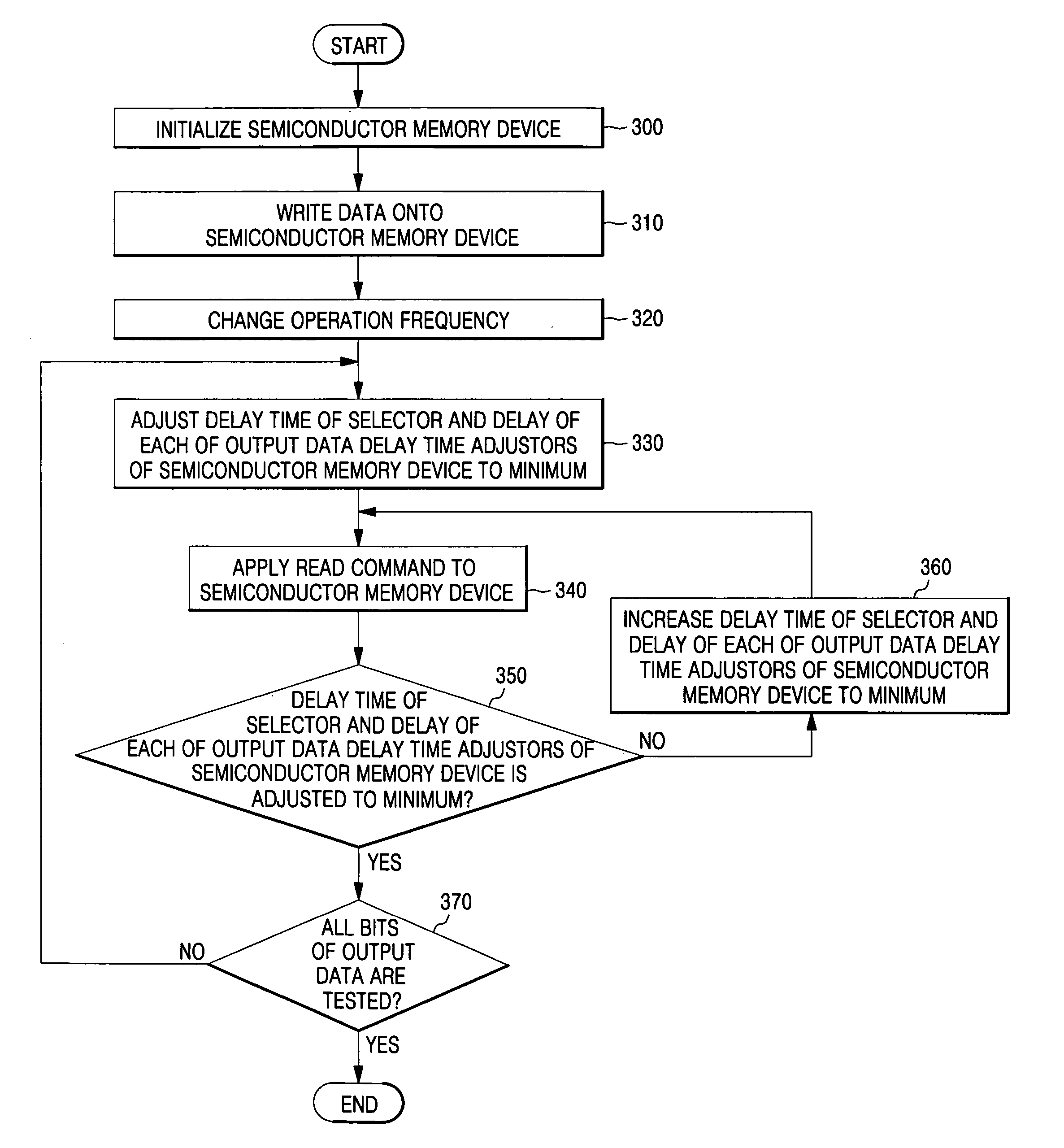

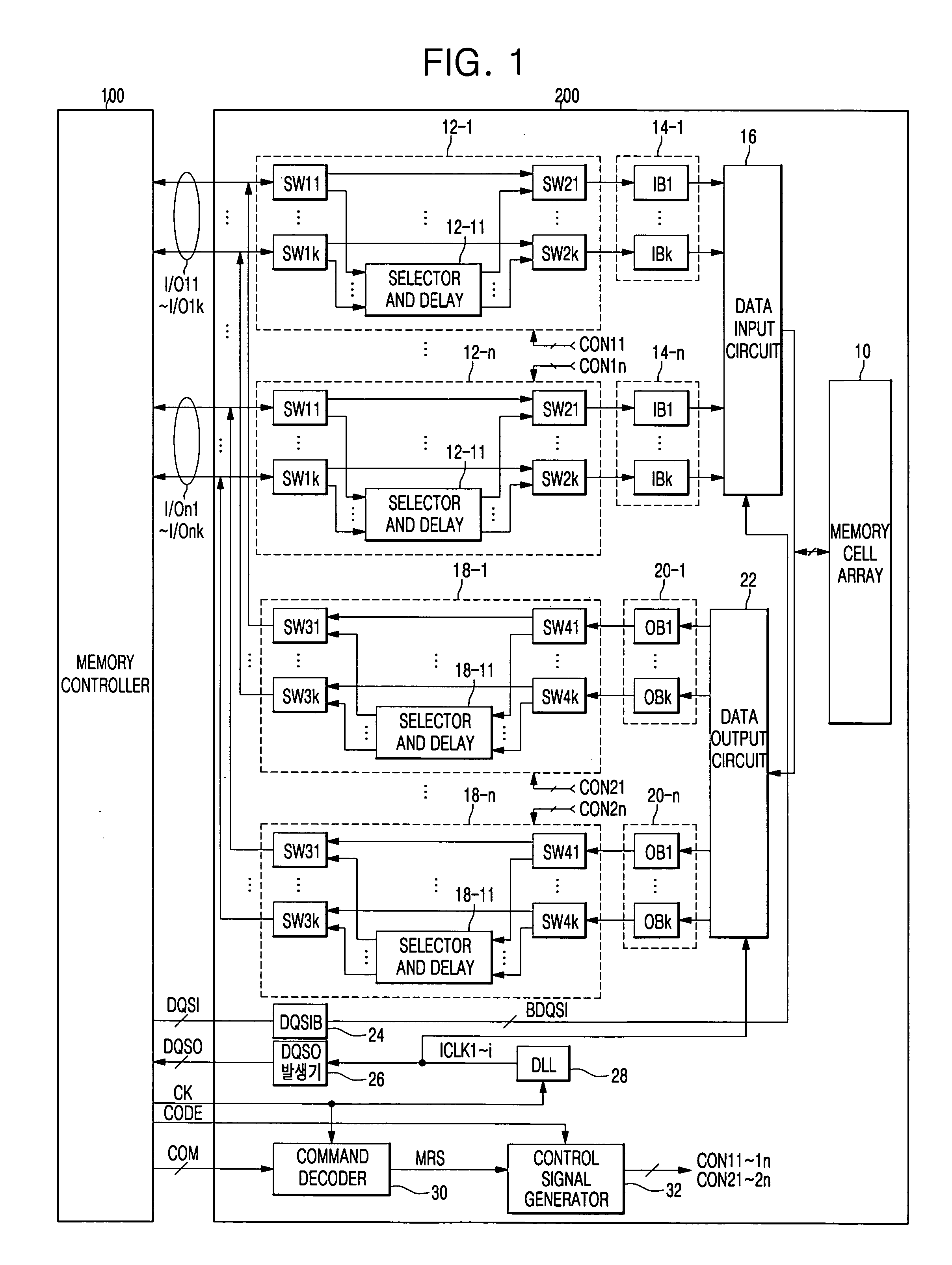

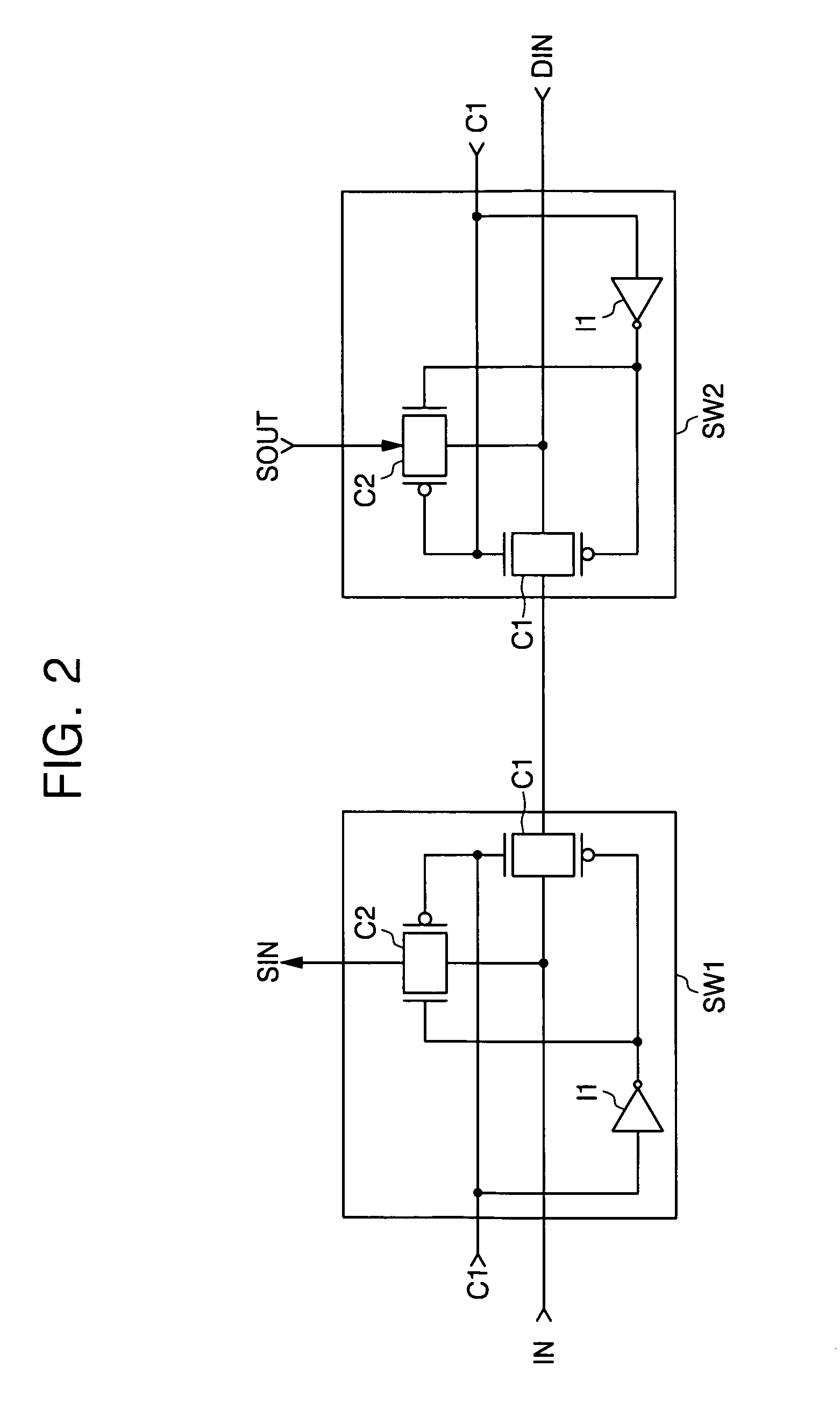

Semiconductor memory device and memory system using same

There is provided a semiconductor memory device and a memory system using the same. The semiconductor memory device includes an input data delay time adjustor for varying an input delay time, selecting one bit of a n-bit input data, delaying the selected one bit by the input delay time and outputting the delayed bit, in response to a control signal during an input data delay test operation; and an output data delay time adjustor for varying an output delay time, selecting one bit of a m-bit output data, delaying the selected one bit by the output delay time and outputting the delayed bit, in response to the control signal during an output data delay test operation, wherein the input data delay time adjustor is arranged for n-bit input data, and wherein the output data delay time adjustor is arranged for m-bit output data.

Owner:SAMSUNG ELECTRONICS CO LTD

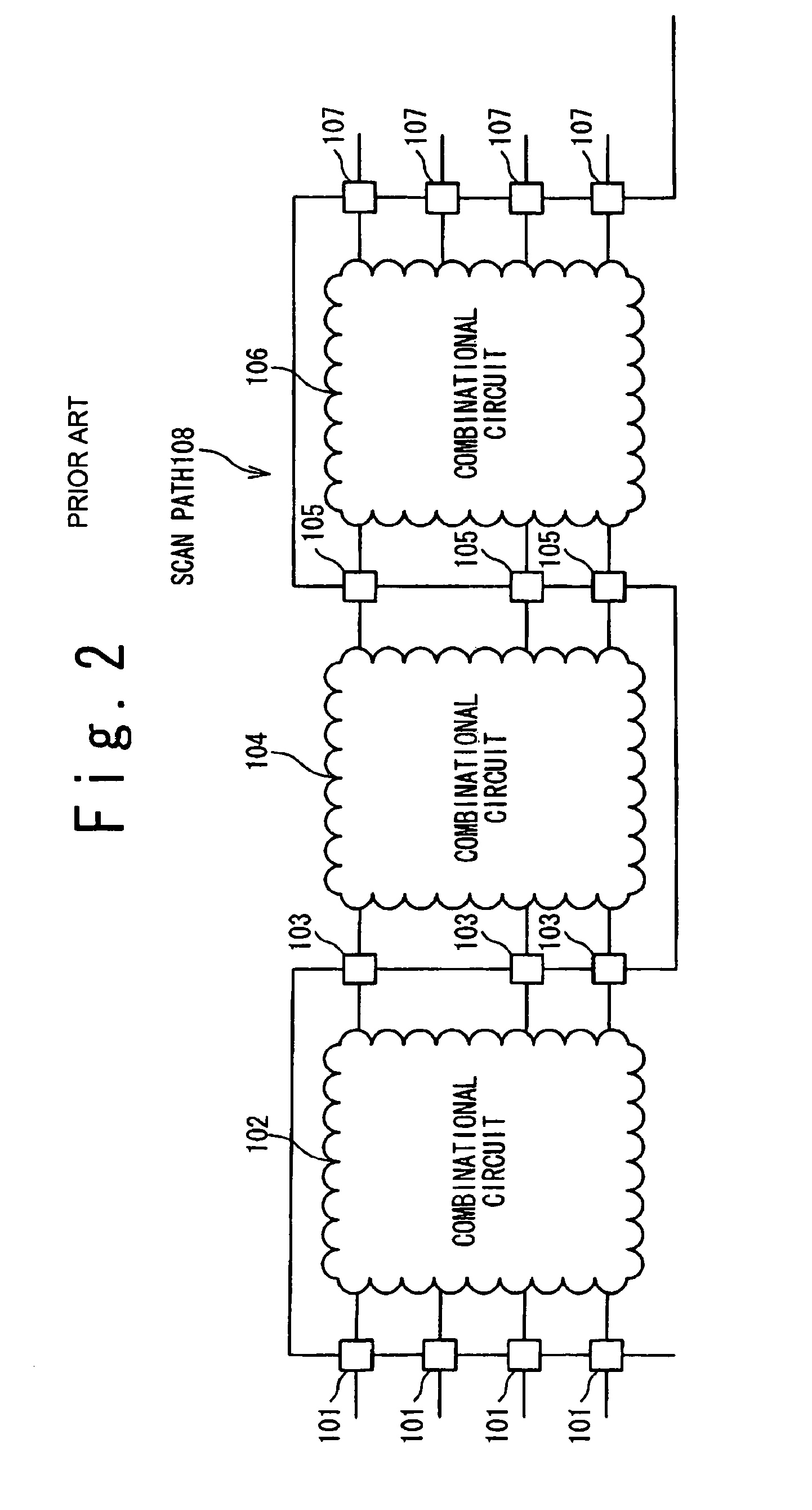

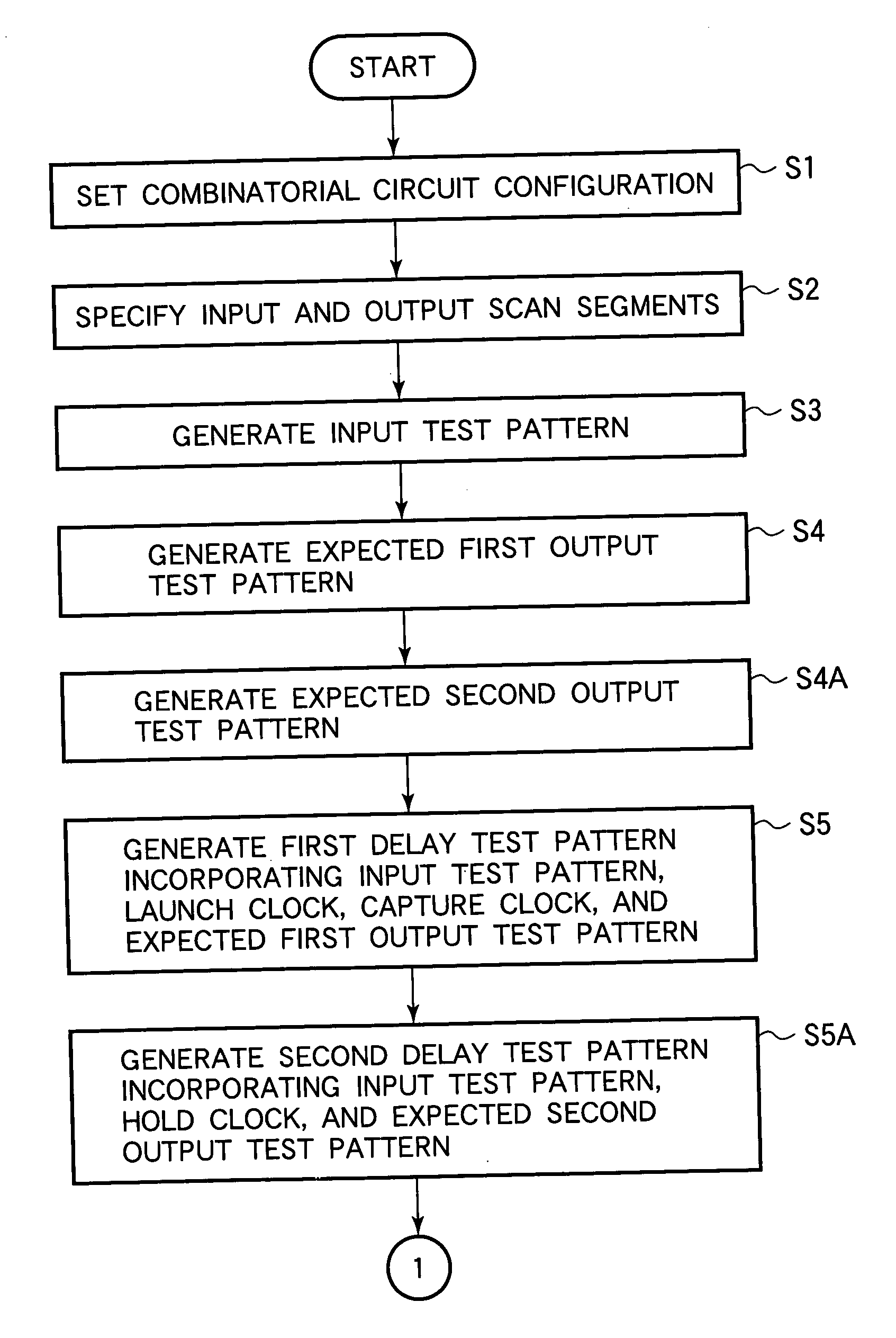

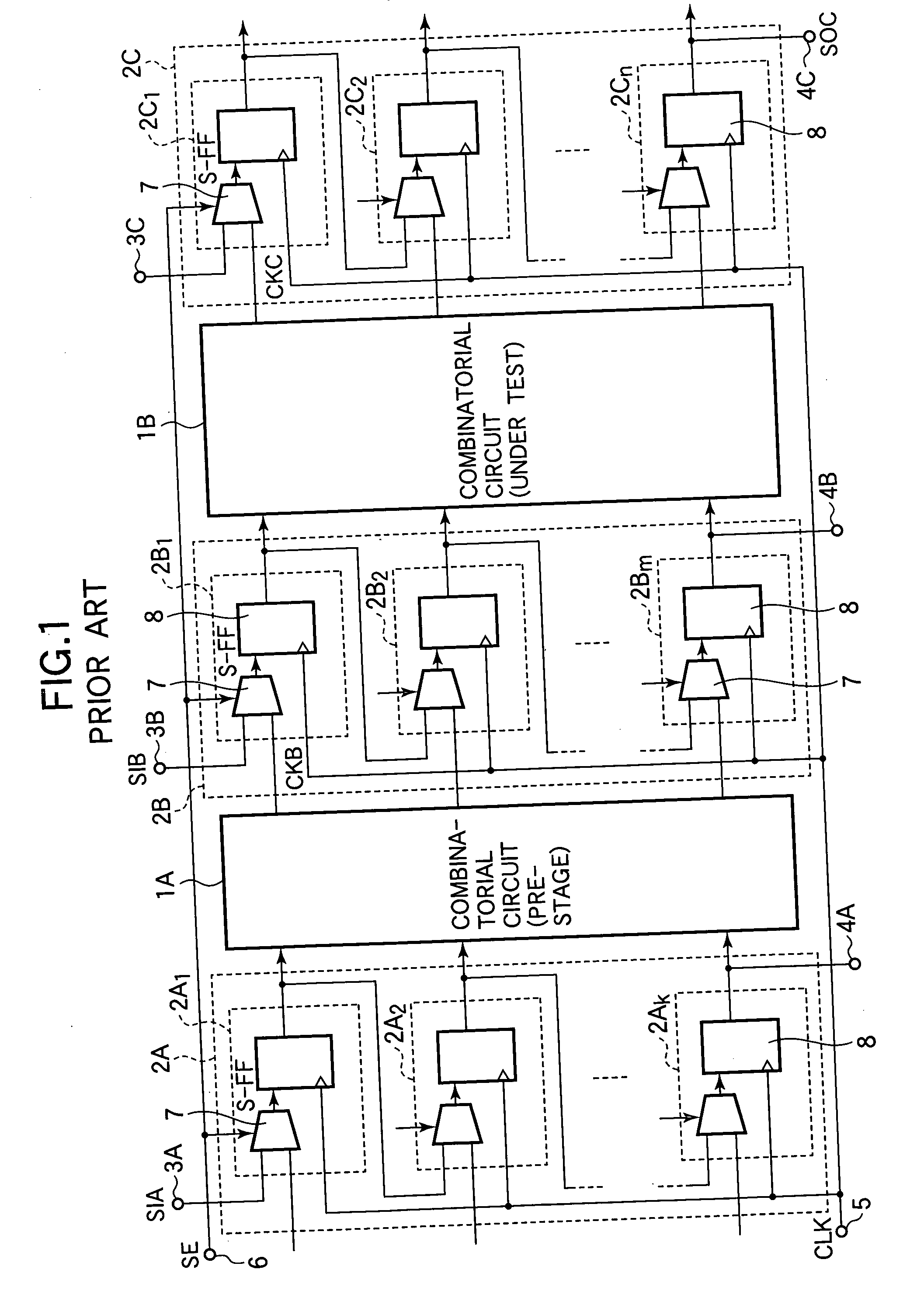

Delay test method for large-scale integrated circuits

The propagation delay of a combinatorial circuit in a large-scale integrated circuit is tested by carrying out two scan tests. Both scan tests generate the same input signal transitions to the combinatorial circuit. One scan test scans the outputs of the combinatorial circuit after the transitions propagate through the combinatorial circuit, using separate launch and capture clock pulses. The other test scans the outputs of the combinatorial circuit before the transitions propagate through the combinatorial circuit, using the same clock pulse for both launch and capture. Use of both tests ensures that propagation delay faults are not masked by large capture clock delays.

Owner:OKI ELECTRIC IND CO LTD