Ageing predetermination and overspeed delay testing bifunctional system and method thereof

A technology of aging prediction and delay testing, which is applied in the field of semiconductor technology and can solve the problems of waste of hardware circuit resources, discarding, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

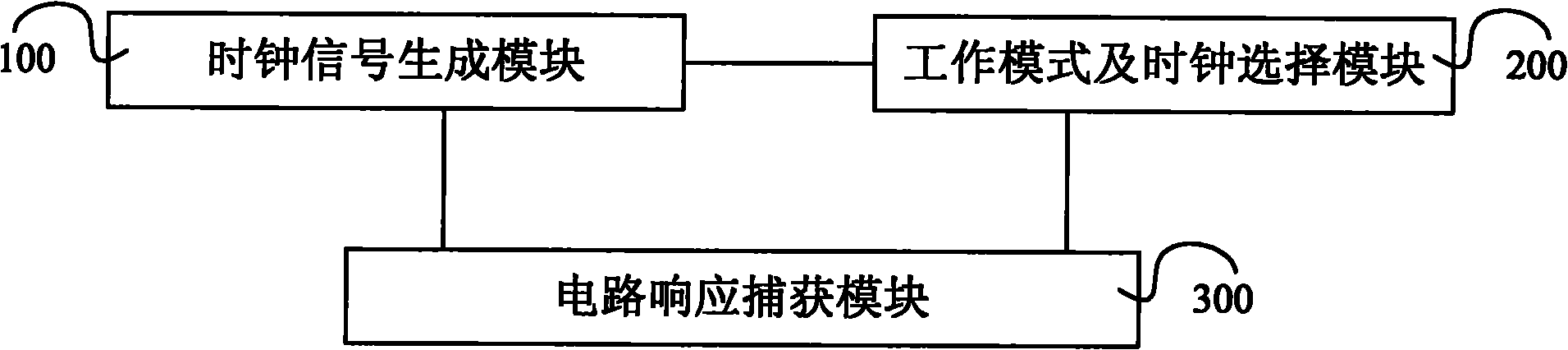

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

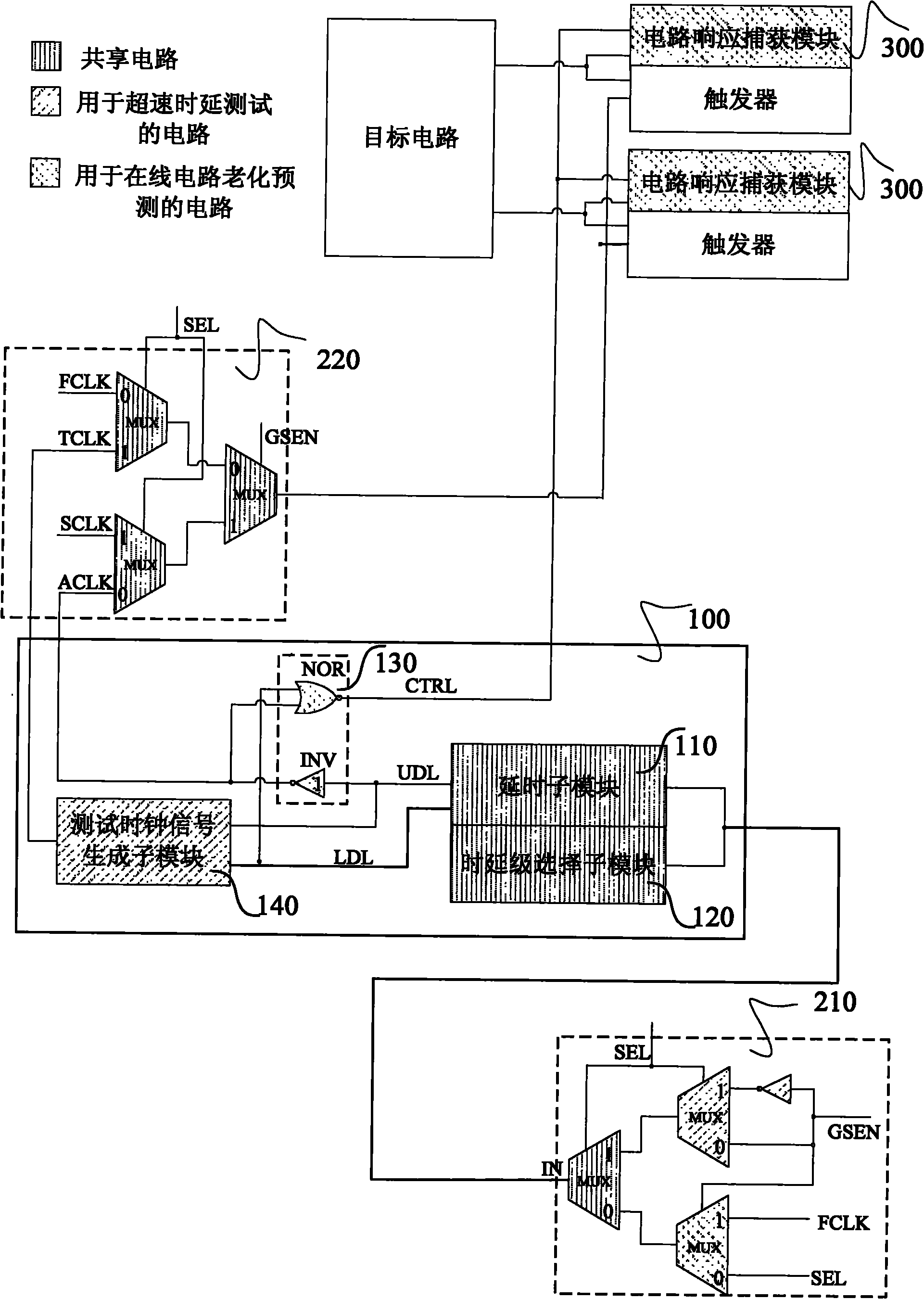

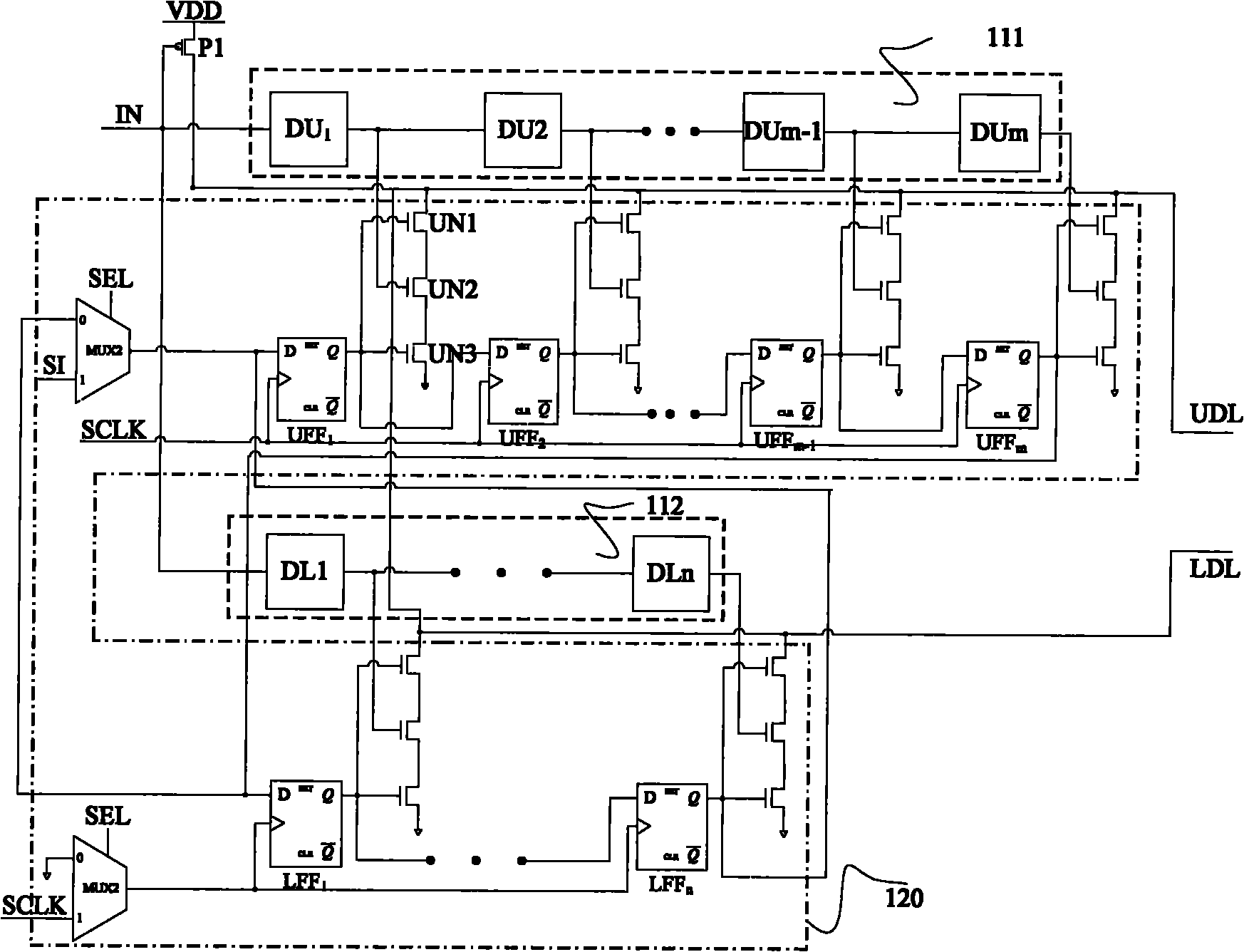

[0128] All scannable flip-flops connected to the upper delay sub-module and the lower delay sub-module are cascaded to form a circular shift register.

[0129] When the initial state of the aging prediction mode is moved into the first control vector, the first control vector is a specific two-hot code; when the first state of the overspeed delay test mode is moved into the second control vector, the second control vector is another A specific two-hot code.

[0130] It is shifted into the circular shift register under the control of SCLK (scanning clock) signal. Since only two bits of this specific two-hot code are 1 and the other bits are all 0, only one output terminal of the scannable flip-flops connected to the upper delay sub-module and the lower delay sub-module is 1 and the other The outputs of the flip-flops are all 0s. Therefore, at the same time, only one group of stacked NMOS transistors in the upper and lower delay sub-modules are all in the conduction state. Th...

specific Embodiment approach

[0153] The aging effect sensor is in a stable state and a capture state in the aging prediction working mode;

[0154] The aging effect sensor is further used to switch between the stable state and the capture state according to the response capture clock signal, the response of the target circuit is not captured in the stable state, the output signal is kept at a low level, and the In the capture state, the response of the circuit is captured within the capture interval, and if the response of the target circuit jumps within the capture interval, the output signal will change from low level to high level to generate an up transition as an alarm signal.

[0155] The structure of the circuit response capturing module in one embodiment is as follows Figure 5 shown.

[0156] In the normal working mode, since the output signal LDL of the down-delay sub-module 112 in the clock generation module 100 is kept at a high level, the CTRL signal is kept at a low level. The low level o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More