Pulse coupling based silicon-nanowire complementary metal oxide semiconductors (CMOS) neuronal circuit

A technology of silicon nanowires and pulse coupling, applied in circuits, logic circuits, pulse technology, etc., can solve problems such as difficult to determine network coefficients, uncertain number of iterations, complex pulse threshold processing, etc., to improve computing speed and facilitate information classification Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

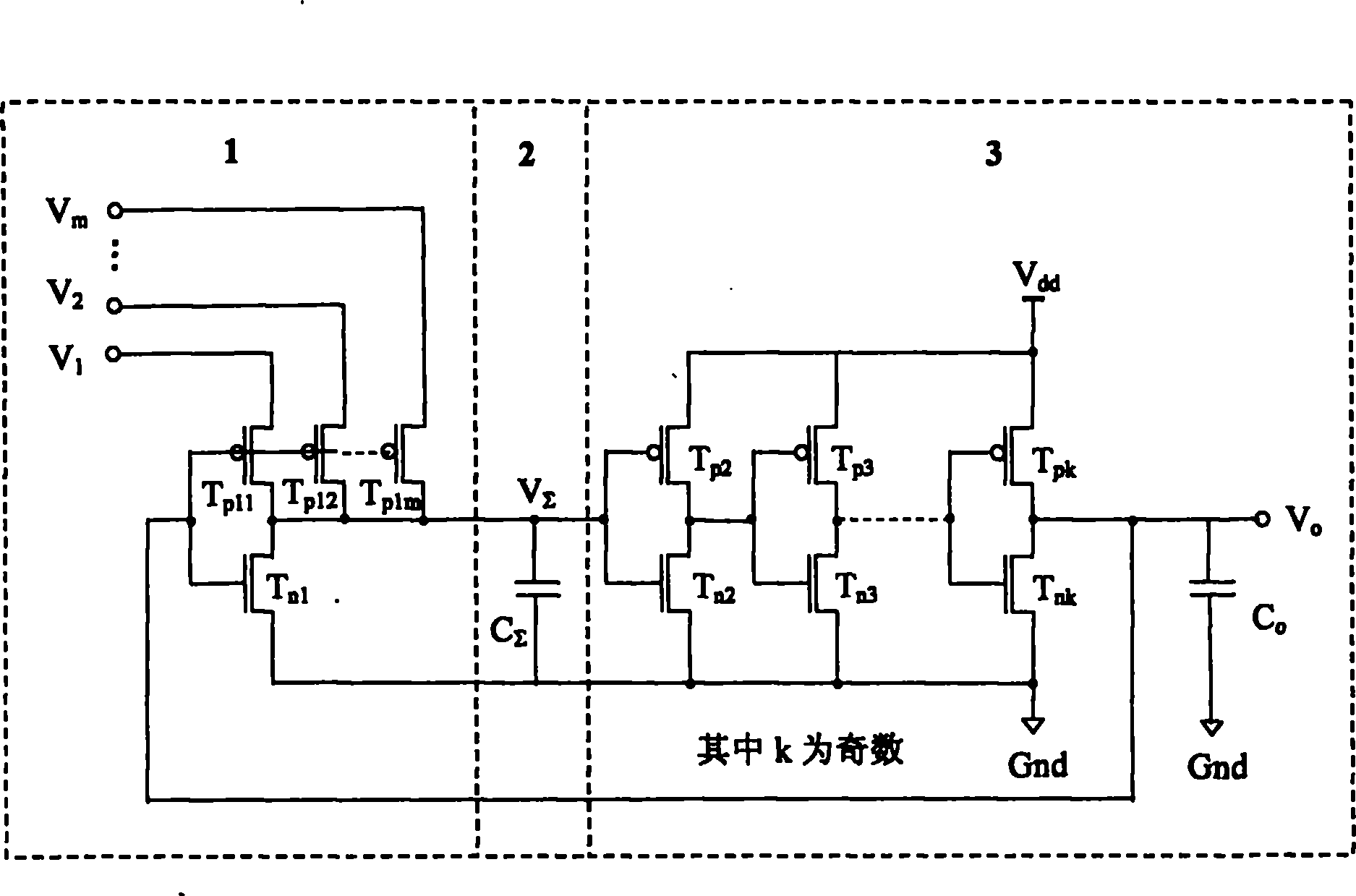

[0032] figure 1 The shown pulse-coupled silicon nanowire CMOS neuron circuit is composed of dendritic circuit 1, integral summer 2 and pulse generating circuit 3 connected in sequence, specifically including:

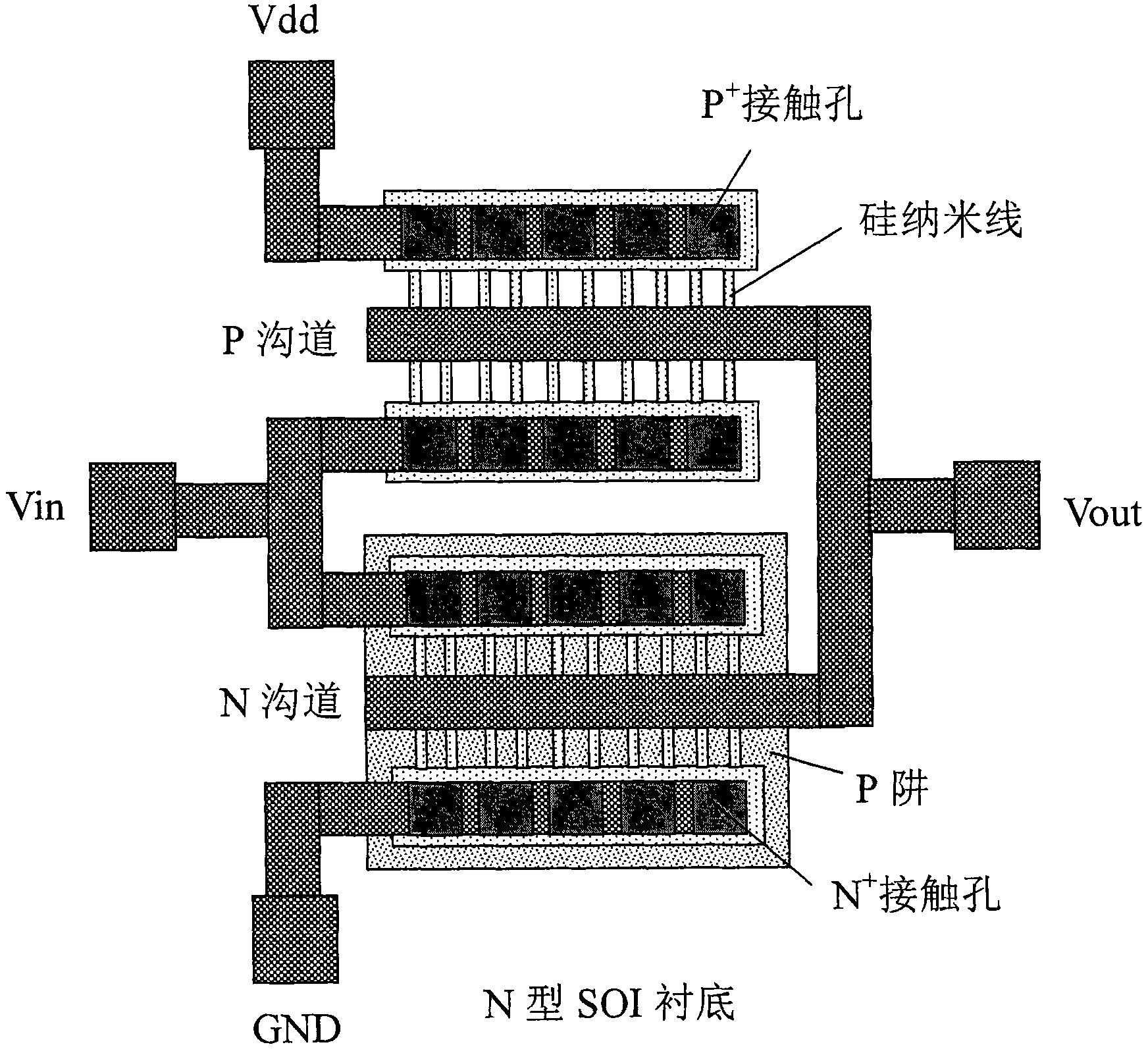

[0033] A dendritic circuit 1, the dendritic circuit 1 is composed of a group of parallel-connected P-type silicon nanowire MOS transistors T p11 ...T p1m with an N-type silicon nanowire MOS transistor T n1 The silicon nanowire CMOS circuit is formed by connecting the drain nodes in series, and the pulse voltage signal is input;

[0034] An integral summer 2, the integral summer 2 is composed of a capacitor C ∑ constituted, the capacitor C ∑ P-type silicon nanowire MOS transistor T in a dendrite circuit p11 .....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More