ROM layout method and system

A technology of read-only memory and layout method, which is applied in the field of read-only memory devices and memory devices, can solve problems such as device degradation, and achieve the effect of reducing the effect of device degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

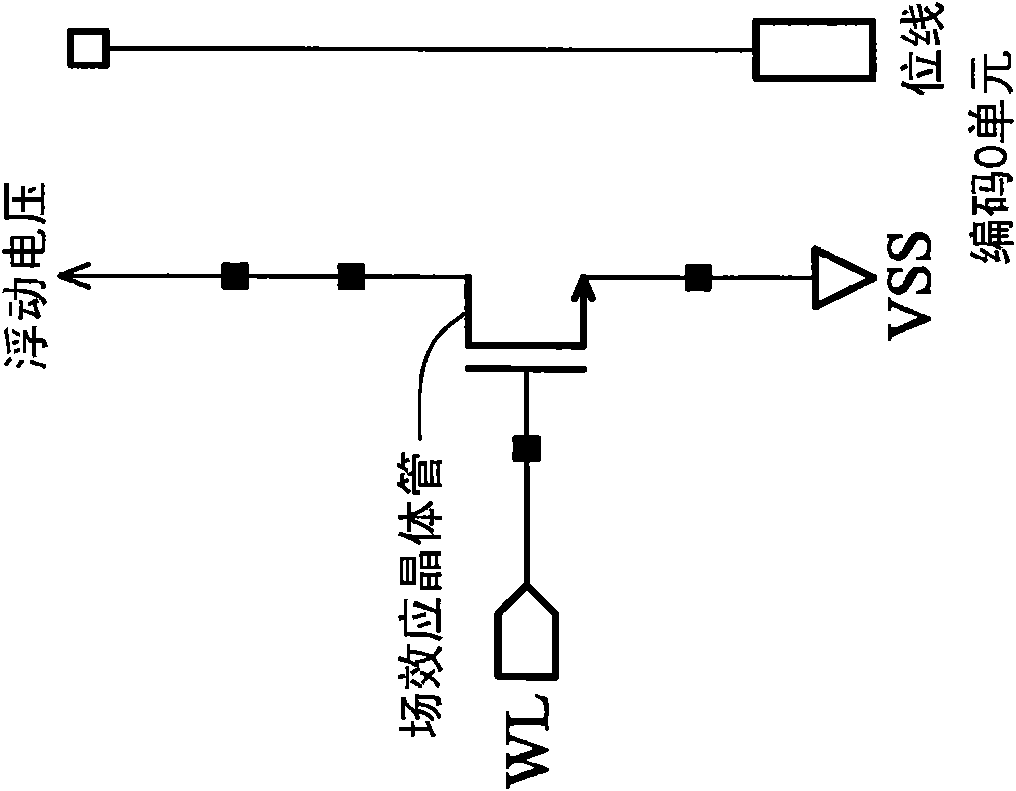

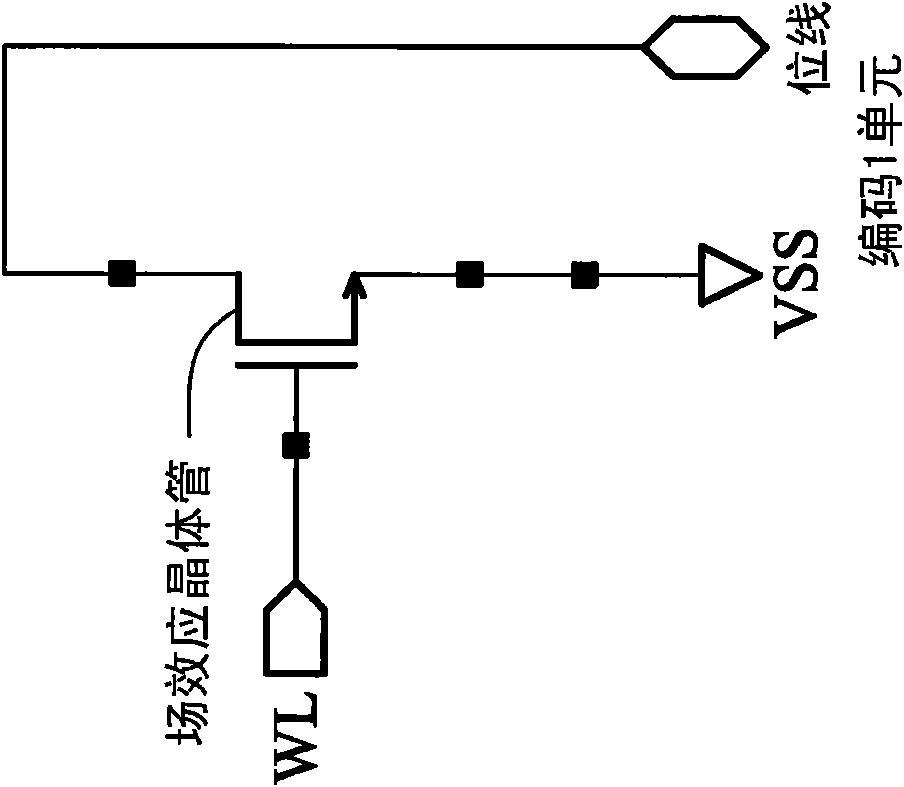

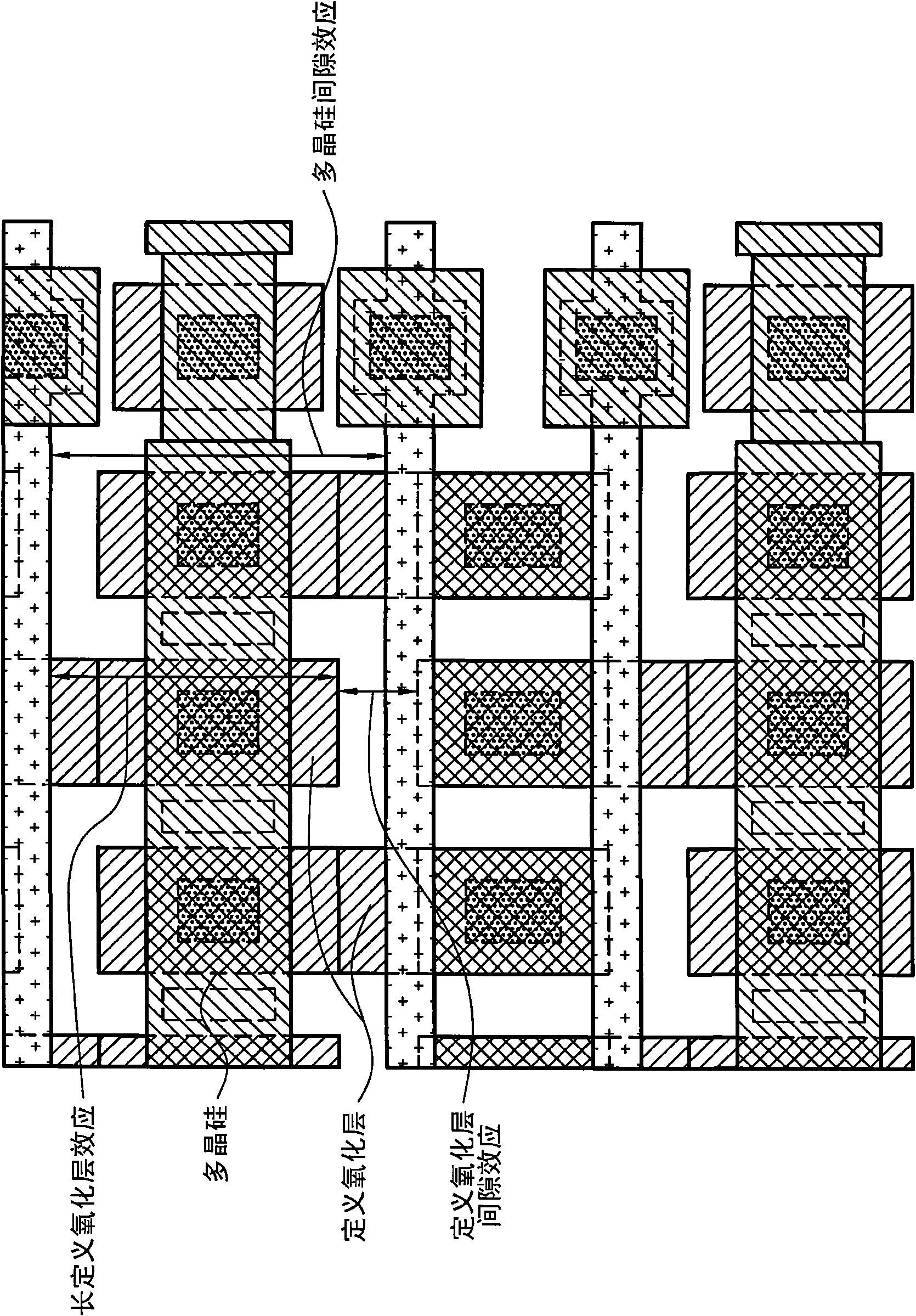

[0048] In previous technologies (eg, sub-32nm technologies), the defined oxide islands can be replaced by redundant devices consisting of continuous defined oxide (continuous OD) and grounded polysilicon to allow equal clearance for Limit the degradation caused by the long definition oxide effect, polysilicon gap effect, and definition oxide gap effect mentioned above. exist image 3One embodiment is shown, a bit cell layout with a continuously defined oxide layer and uniform poly spacing. Grounded polysilicon (e.g., a polysilicon gate coupled to ground) is often used as a redundant device in sub-32nm technology to separate bit-for-bit to avoid shorting of bit cells (e.g., shorting of a coded 1 bit cell to a coded 0 bit cell, and vice versa). These redundant devices are used when the defined oxide layer no longer configures isolated islands.

[0049] However, modeling this grounded polysilicon redundant device using a continuously defined oxide layer in a circuit diagram cr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More