DSP (Digital Signal Processing) chip-oriented instruction scheduling method

An instruction scheduling and chip technology, applied in the field of compilers, can solve problems such as being limited to a specific function, large amount of audio and video data, etc., to achieve the effect of improving efficiency and optimizing processing programs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

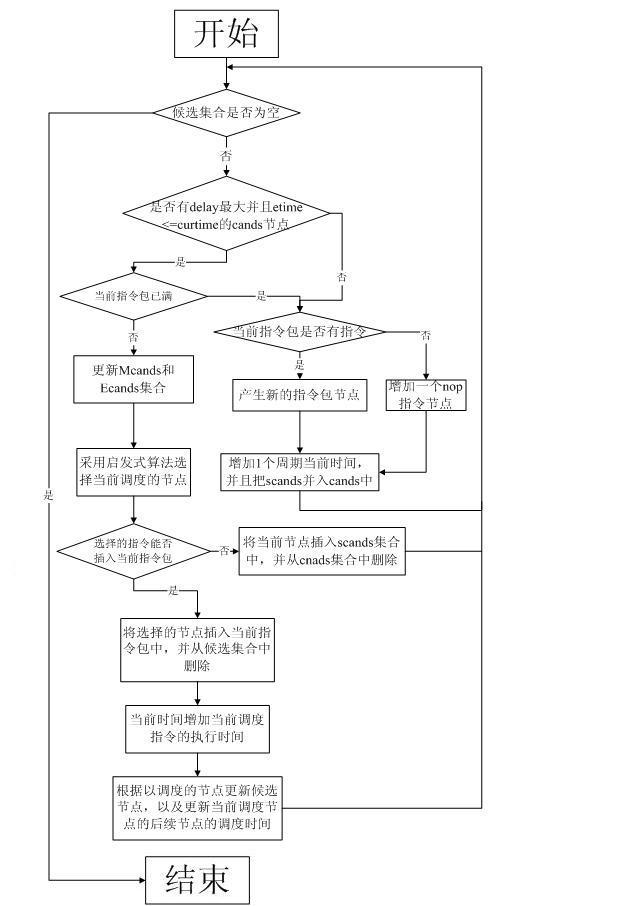

[0017] The present invention will be further elaborated below in conjunction with the accompanying drawings.

[0018] First call the GCC (compiler for programming under the linux system) compiler to generate the assembly code file corresponding to the computer language code, and then based on the assembly file, perform the following series of instruction scheduling methods for DSP chips to generate the same name The assembly code file is finally handed over to the linker to generate an executable file.

[0019] Such as figure 1 A schematic diagram of the steps of the shown DSP chip-oriented instruction scheduling method, which includes the following steps:

[0020] Step A. constructing topological sorting between assembler basic block statements;

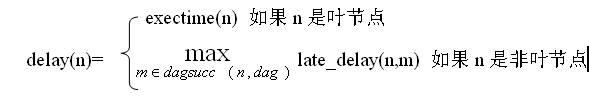

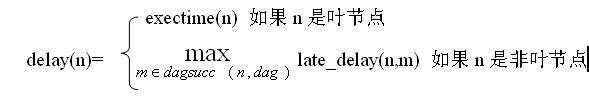

[0021] Step B. On the basis of the topological sort obtained in step A, calculate the delay value delay of each instruction in the assembly language program basic block;

[0022] Step C. Traversing the data dependency graph from ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap