Chip for measuring ohmic contact degradation of semiconductor device and method

An ohmic contact and semiconductor technology, used in semiconductor devices, single semiconductor device testing, semiconductor/solid-state device manufacturing, etc., can solve the problems of inability to assess the degradation of ohmic contact resistance, loss of semiconductor materials, and inability to directly apply assessment current to achieve accurate Effective ohmic contact, accurate and effective evaluation, and the effect of meeting the requirements of high current impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

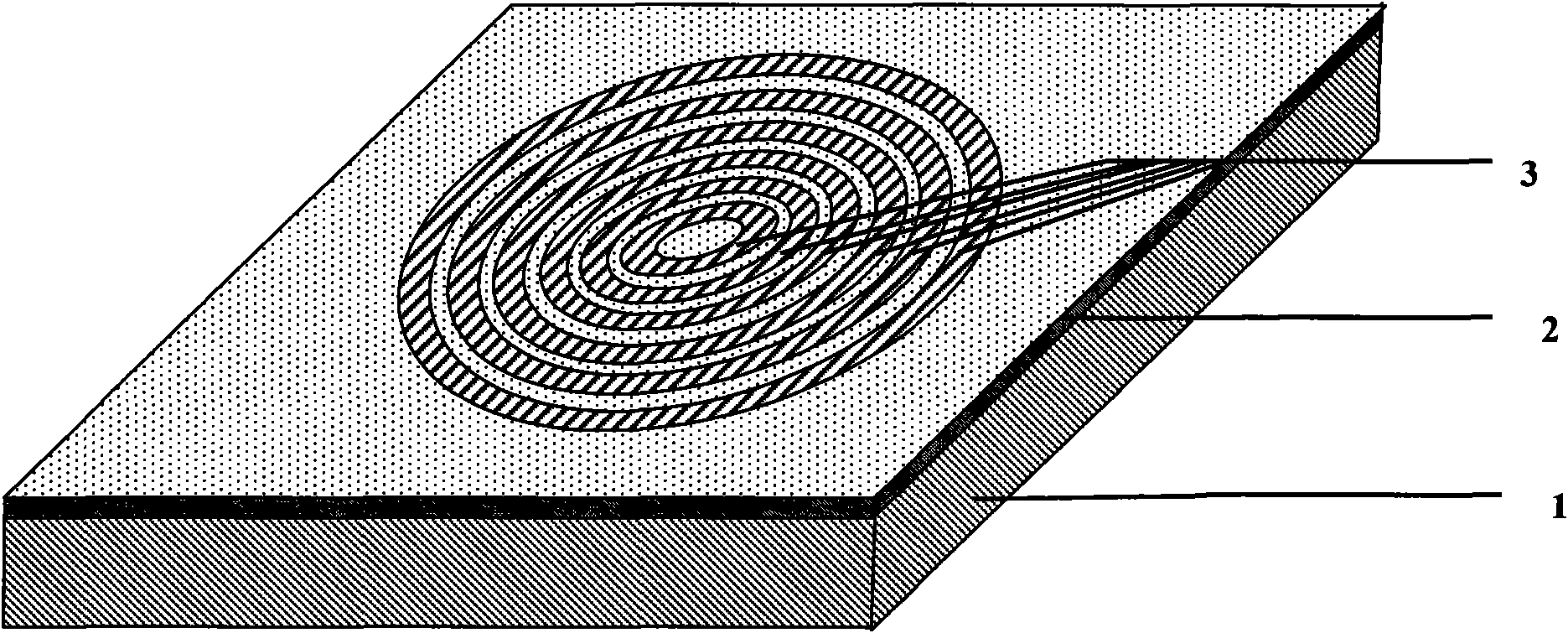

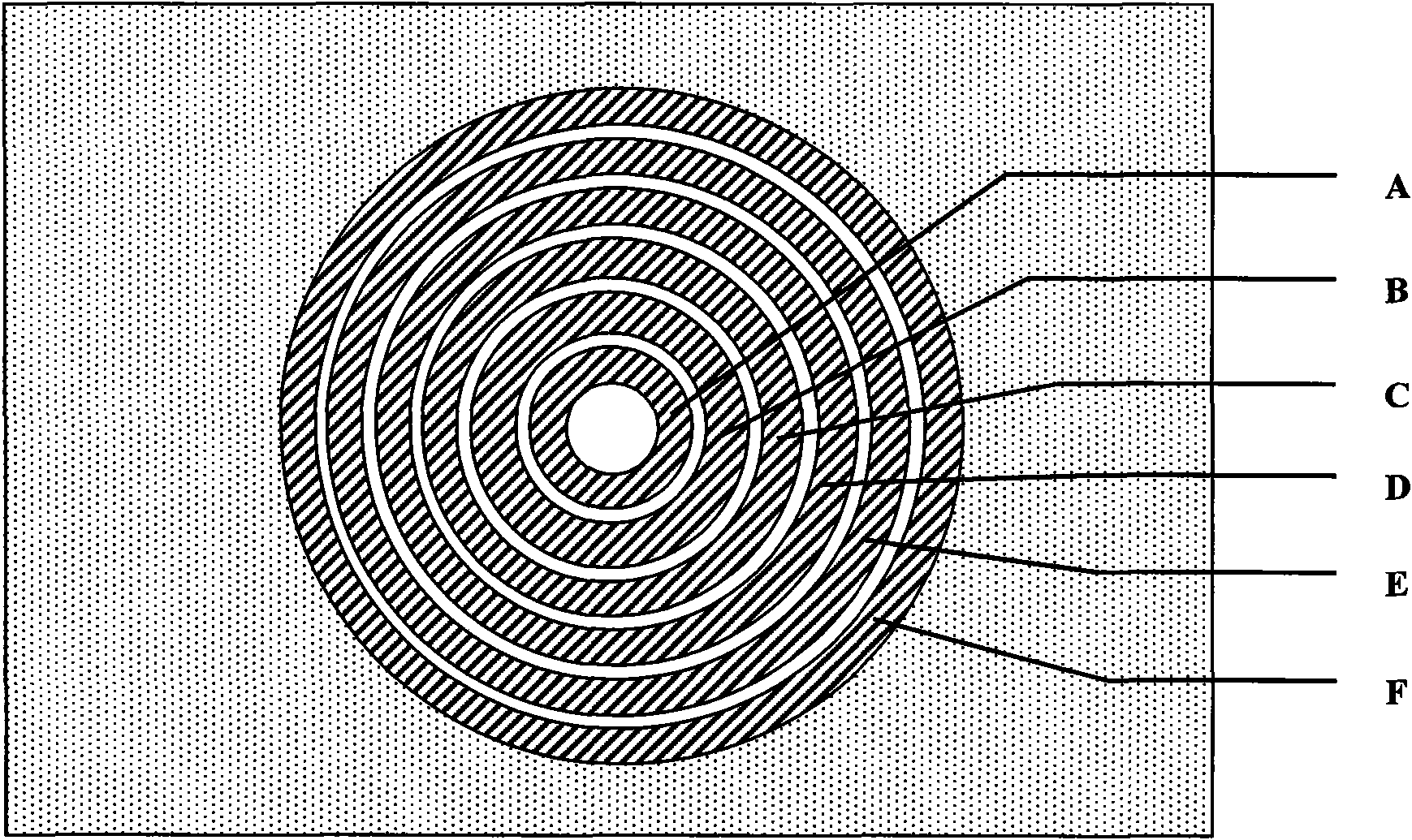

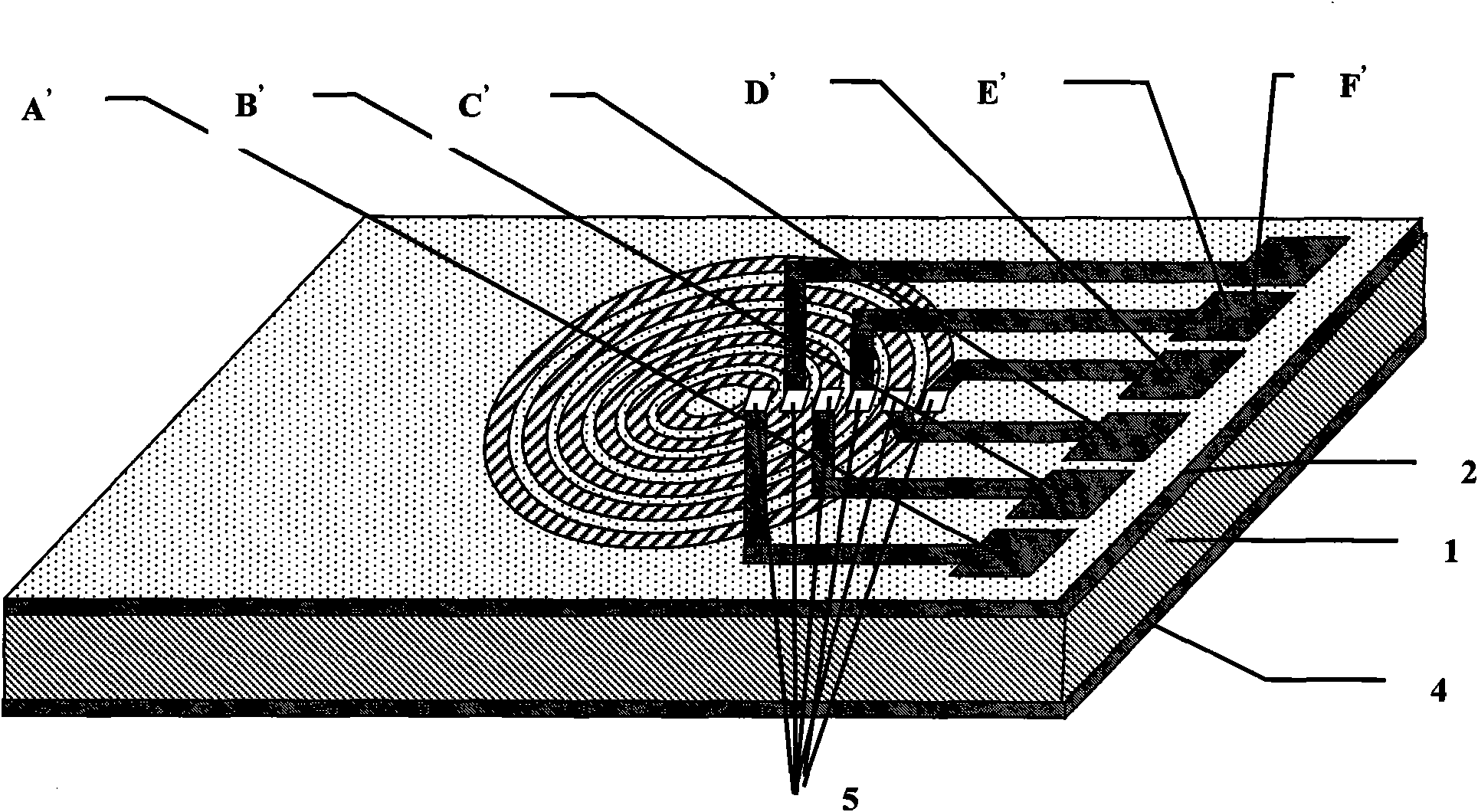

[0027] See image 3 The chip for measuring the ohmic contact degradation failure of semiconductor devices used to achieve the purpose of the present invention includes preparing a semiconductor epitaxial material 2 on a semiconductor wafer substrate 1, and the thickness of the semiconductor wafer substrate is 50 μm. Using a specific ohmic contact process, prepare the ring electrode 3 fixed to the surface of the semiconductor epitaxial material 2, the electrode 3 includes 6 ring electrodes (A, B, C, D, E, F), and prepare the back electrode on the back of the substrate 1 4. A layer of insulating dielectric film is deposited on the surface of the prepared chip, and external electrode windows are carved on the ring electrodes (A, B, C, D, E, F) by photolithography technology, and these windows are arranged in a straight line. And contact electrodes A', B', C', D', E', F' with large external areas. Generally, the thickness of the prepared ohmic contact semiconductor epitaxial mat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com