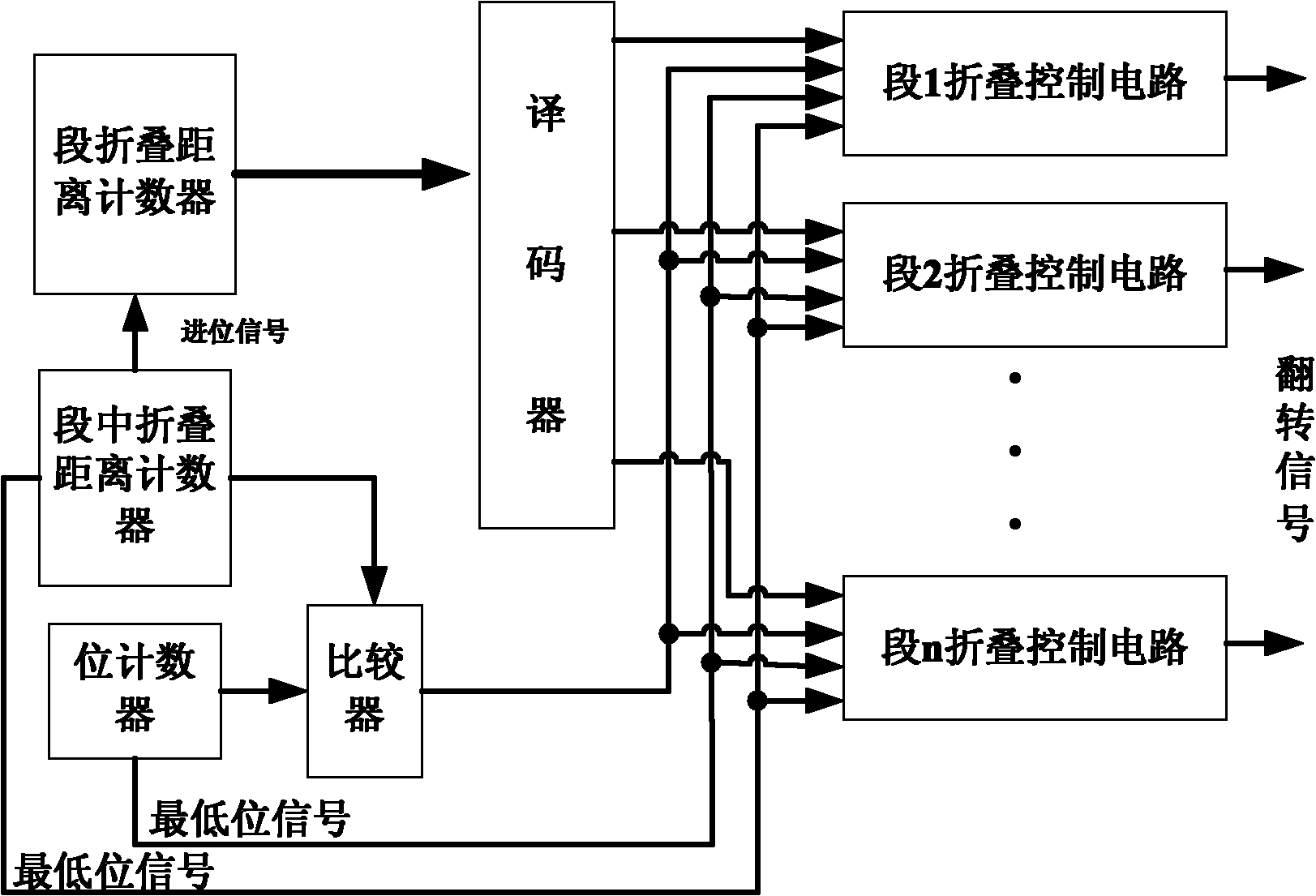

Re-sowing test plan based on parallel folding counter

A test scheme and counter technology, applied in digital circuit testing, electronic circuit testing, etc., can solve the problems of large amount of test data, few chip test points, long test time, etc., to reduce storage capacity, reduce test time, and save test. effect of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] Implement the present invention and carry out as follows:

[0045] Step 1: Data compression process before testing

[0046] A, adopt automatic test mode generation tool ATPG to generate the test set T determined for the fault of tested circuit requirement test, and record LFSR seed set as seed set S, and described seed set S is initially empty;

[0047] b. In the test set T, select a test vector P, generate all the folding seeds corresponding to the test vector P, encode all the folding seeds with LFSR, record all the successfully encoded folding seeds and the coded The LFSR seeds of the LFSR; record the test vectors included in the test set T in the fold counter state sequence generated by all successfully encoded fold seeds; the fold seeds that can cover the most test vectors in the test set T and the corresponding LFSR seeds are Retain it, and add the reserved LFSR seed to the seed set S;

[0048] c. Find out in the test set T a test vector compatible with the fold...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More