Instruction prefetch-based multi-core shared memory control equipment

A technology for controlling equipment and instruction prefetching, applied in the address formation of the next instruction, instruments, machine execution devices, etc., can solve the problems of low data throughput, increased delay, and large memory access delay, so as to improve transmission efficiency, The effect of reducing time loss and increasing throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

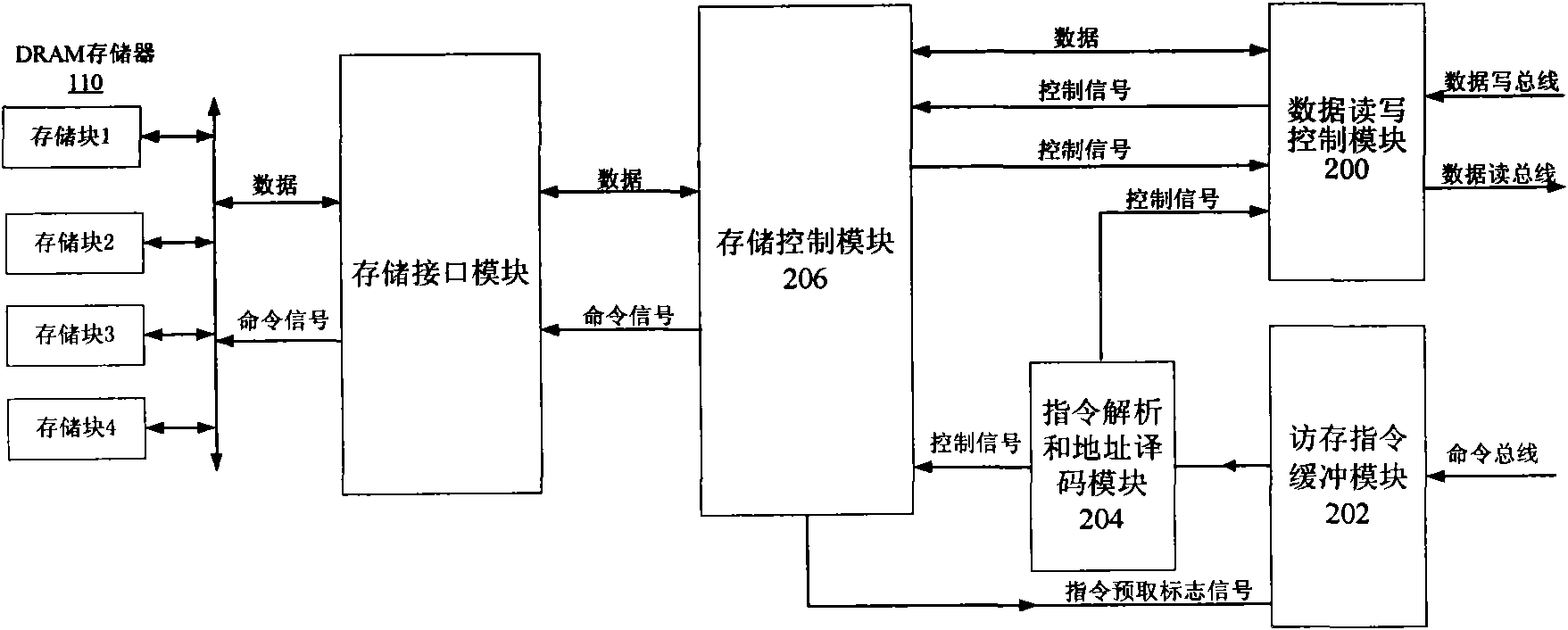

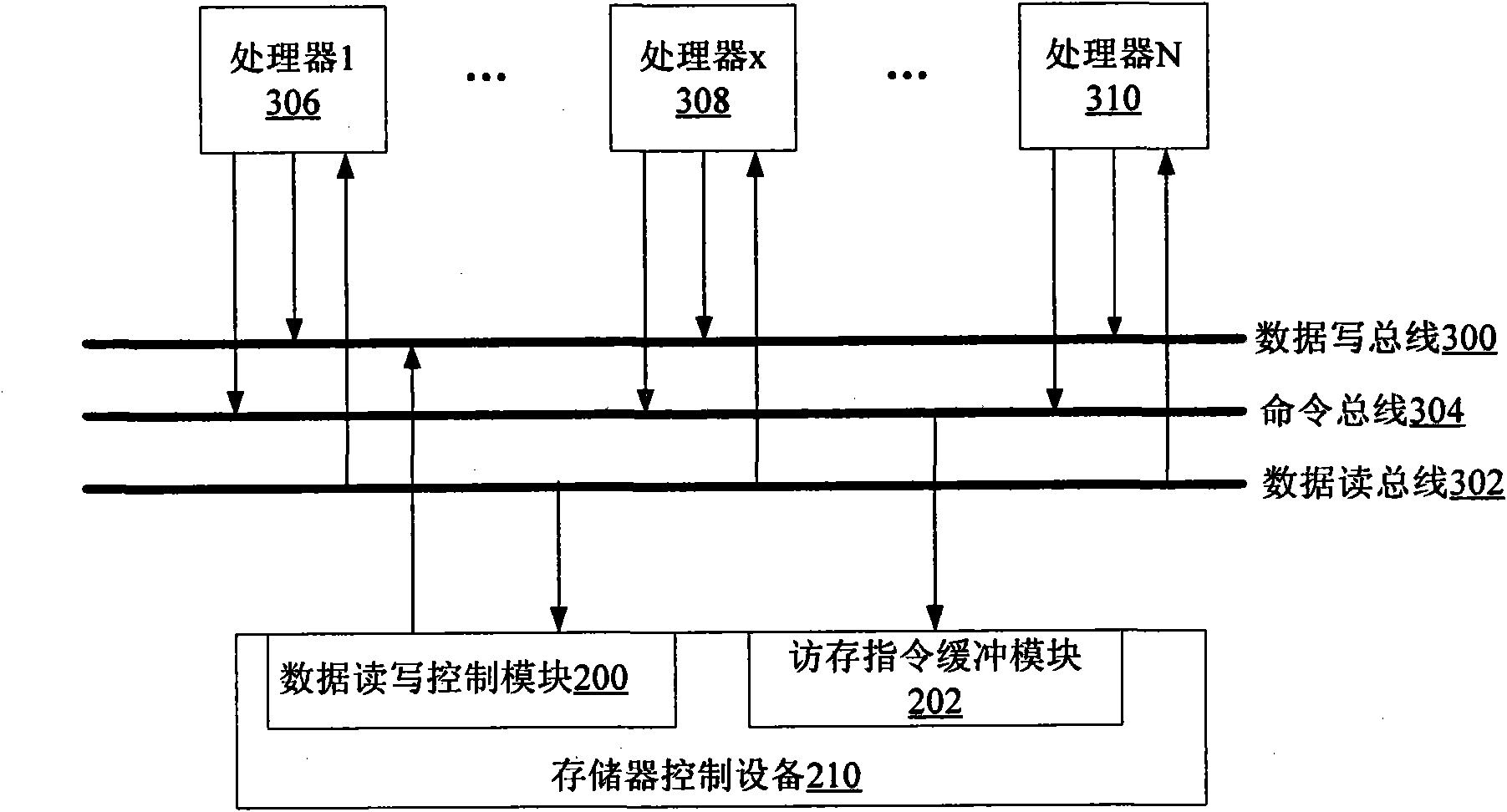

[0055] Such as figure 2 Shown is a schematic diagram of a multi-core shared memory control device based on instruction prefetching. In the embodiment of the present invention, memory access commands and read / write data are processed separately using different bus structures, so that parallel execution of memory access can be realized to the greatest extent. The command bus 304 is a unidirectional bus, which is only responsible for transferring memory access instructions sent from multiple processors. In the embodiment of the present invention, the instruction format of the memory access instruction includes the instruction type of the instruction, the ID number of the processor, the address of the memory to be accessed, the address of the internal register of the processor, and the number of data to be transferred.

[0056] In order to improve data throughput performance, the data bus is divided into a data read bus 302 and a data write bus 300 in the embodiment of the prese...

Embodiment 2

[0058] The storage control device instruction prefetch implementation in this embodiment is as follows: Figure 4 shown. The implementation involves the storage control module 206 , the memory access instruction buffer module 202 and the instruction parsing and address decoding module 204 .

[0059] The storage control module 206 includes a read and write control logic 400 , a control information register 402 , an address comparator 404 and a flag register 406 . The read-write control logic 400 is responsible for controlling the transition of the internal state of the storage control device, realizing correct reading and writing of data, and deciding when to send the instruction prefetch flag signal 408 . The read / write control logic 400 determines the next state according to the information of the current instruction 412 stored in the control information register 402 and the content of the flag register 406 . The control information register 402 is responsible for saving th...

Embodiment 3

[0086] The DRAM storage control device in the embodiment of the present invention is equipped with a data read / write control module 200 . The implementation of the data reading and writing control module 200 is as follows: Figure 8 shown. The data reading and writing control module 200 includes: an internal bus interface 812, which receives control signals from the storage control module 206 and the instruction parsing and address decoding module 204 and the data read from the DRAM memory 110, and the control signals include memory access instructions. Type, processor ID number, specified multi-thread processor internal register address and data bus request signal; data read bus address data register 806: responsible for saving the address of the specified multi-thread processor register on the data read bus, data read bus request signal and Data read bus data; data write bus address register 808: responsible for saving the designated multi-thread processor register address ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More