Three-dimensional packaging method

A three-dimensional packaging and substrate technology, applied in semiconductor devices, electrical components, circuits, etc., to achieve the effect of low injection cost and easy integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] Next, a specific implementation manner of a three-dimensional packaging method of the present invention will be described in detail with reference to the accompanying drawings.

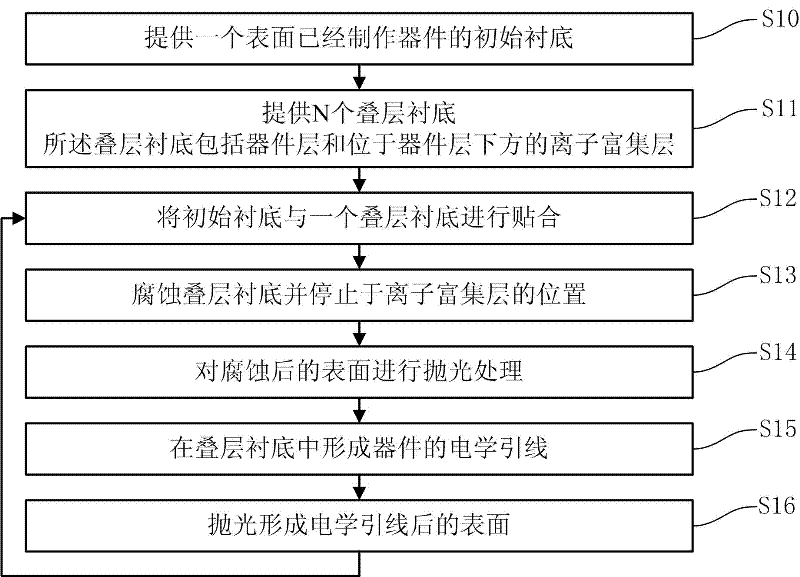

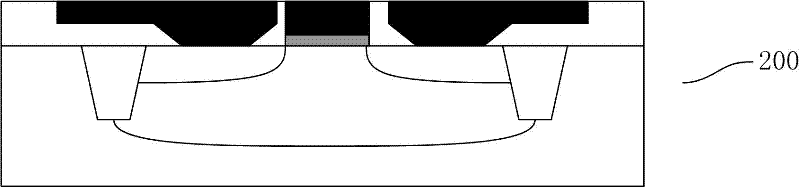

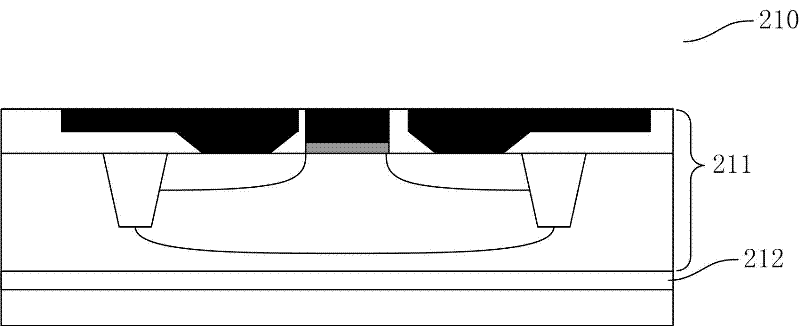

[0013] attached figure 1 Shown is a schematic diagram of the implementation steps of the method described in this specific embodiment, including: step S10, providing an initial substrate whose surface has been fabricated with devices; step S11, providing N stacked substrates, the stacked substrates including devices layer and the ion-enriched layer below the device layer; Step S12, attaching the initial substrate to a stacked substrate; Step S13, corroding the stacked substrate and stopping at the position of the ion-enriched layer; Step S14, Polishing the corroded surface; Step S15, forming electrical leads of the device in the laminated substrate; Step S16, polishing the surface after forming the electrical leads, forming a three-dimensional packaging structure with two device layers. The ab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More