Method for depositing gate dielectric, method for preparing MIS capacitor and MIS capacitor

A gate dielectric and gate dielectric layer technology, applied in the field of MIS capacitors, can solve the problems of deterioration of electrical characteristics and increase of equivalent gate oxide thickness, and achieve the effect of improving electrical performance and reducing thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

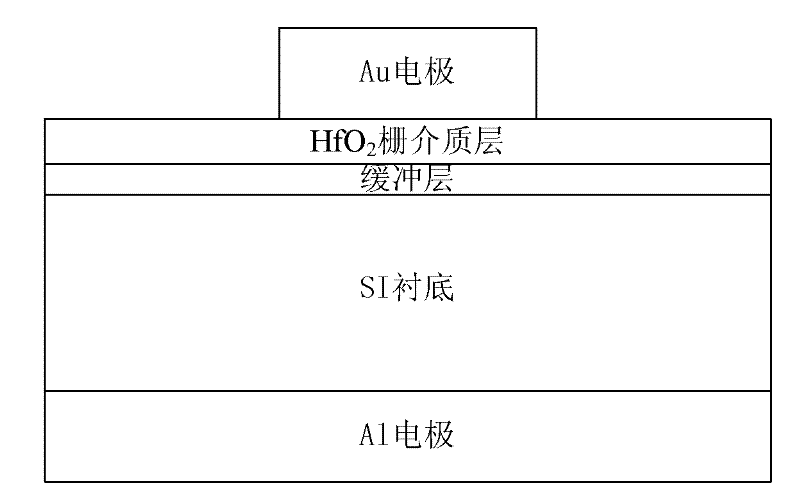

[0013] The present invention will be described in detail below in conjunction with the accompanying drawings.

[0014] The method for plasma-enhanced atomic layer deposition gate dielectric of the present invention comprises the following steps:

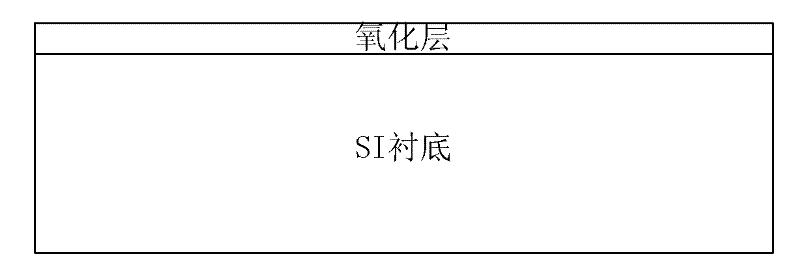

[0015] First, a semiconductor substrate is cleaned. For example, put a cut Si substrate into (NH 4 OH:H 2 o 2 :H 2 O=2:1:7) ultrasonic cleaning for 15 minutes in order to remove metal contamination on the surface of the Si substrate, followed by rinsing with deionized water, and then putting the Si substrate into a dilute HF solution (HF:H 2 (0=1:50) for about 3 minutes to remove the oxide on the surface of the Si substrate, then clean the surface of the Si substrate with deionized water, and finally dehydrate with alcohol, thereby completing the cleaning of the Si substrate.

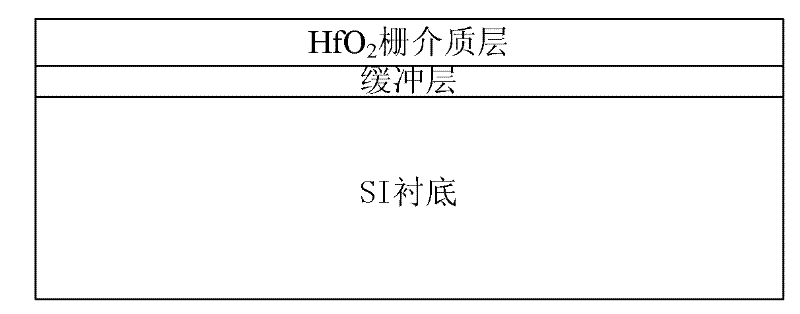

[0016] Next, the cleaned semiconductor substrate was treated with O 2 The plasma and the nitrogen-containing plasma pretreat the surface of the semicond...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More