Patents

Literature

47 results about "MIS capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A MIS capacitor is a capacitor formed from a layer of metal, a layer of insulating material and a layer of semiconductor material. It gets its name from the initials of the metal-insulator-semiconductor structure. As with the MOS field-effect transistor structure, for historical reasons, this layer is also often referred to as a MOS capacitor, but this specifically refers to an oxide insulator material.

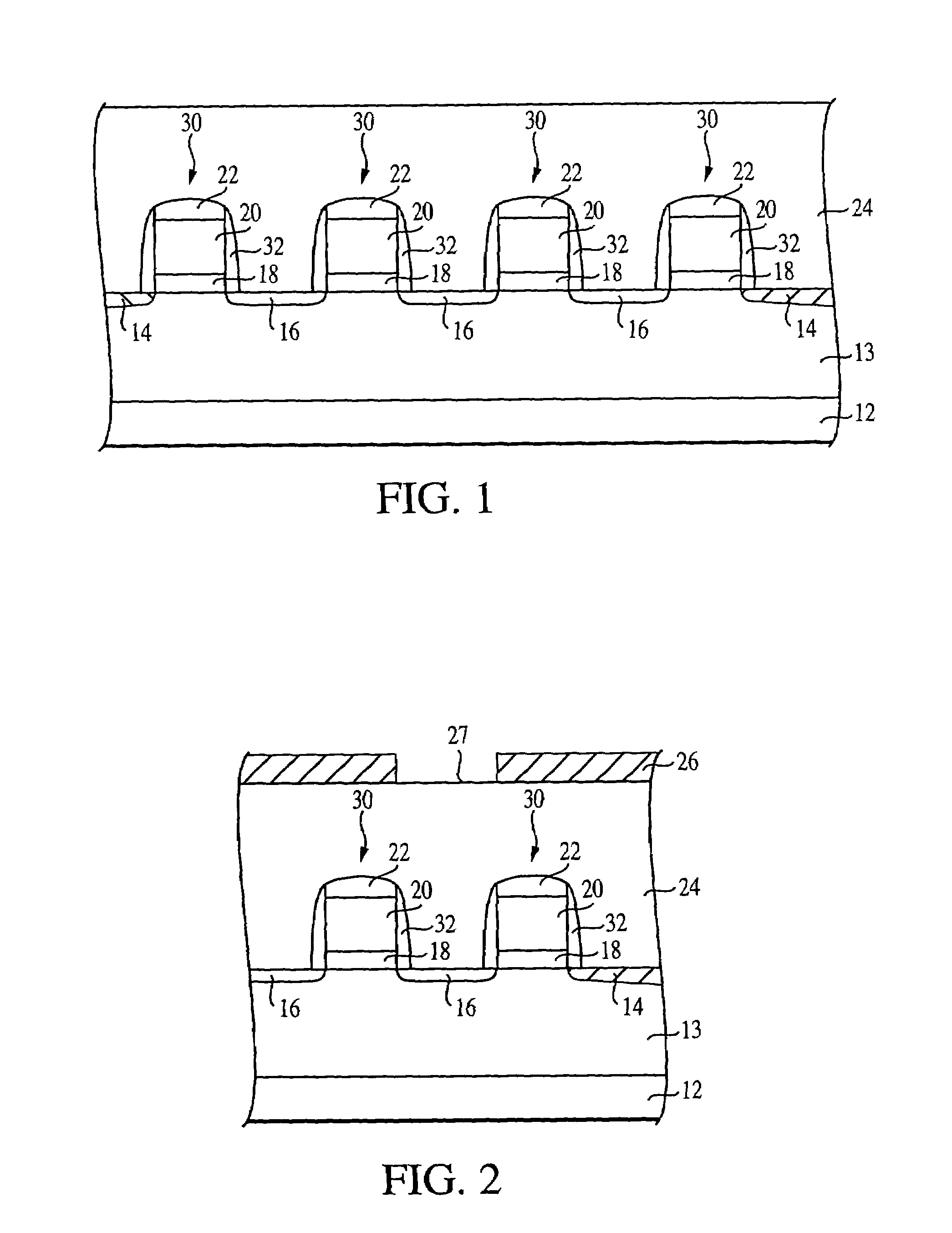

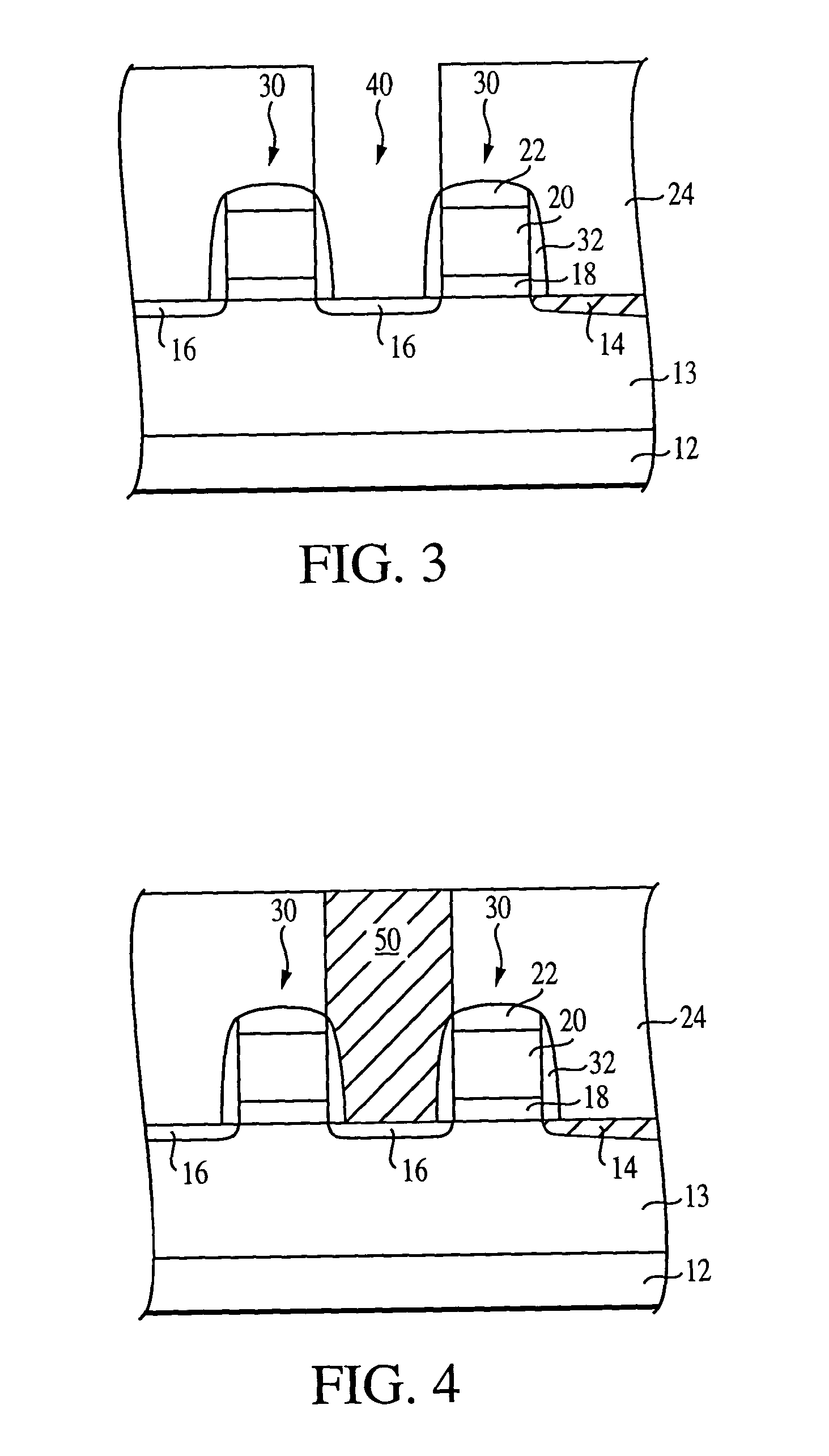

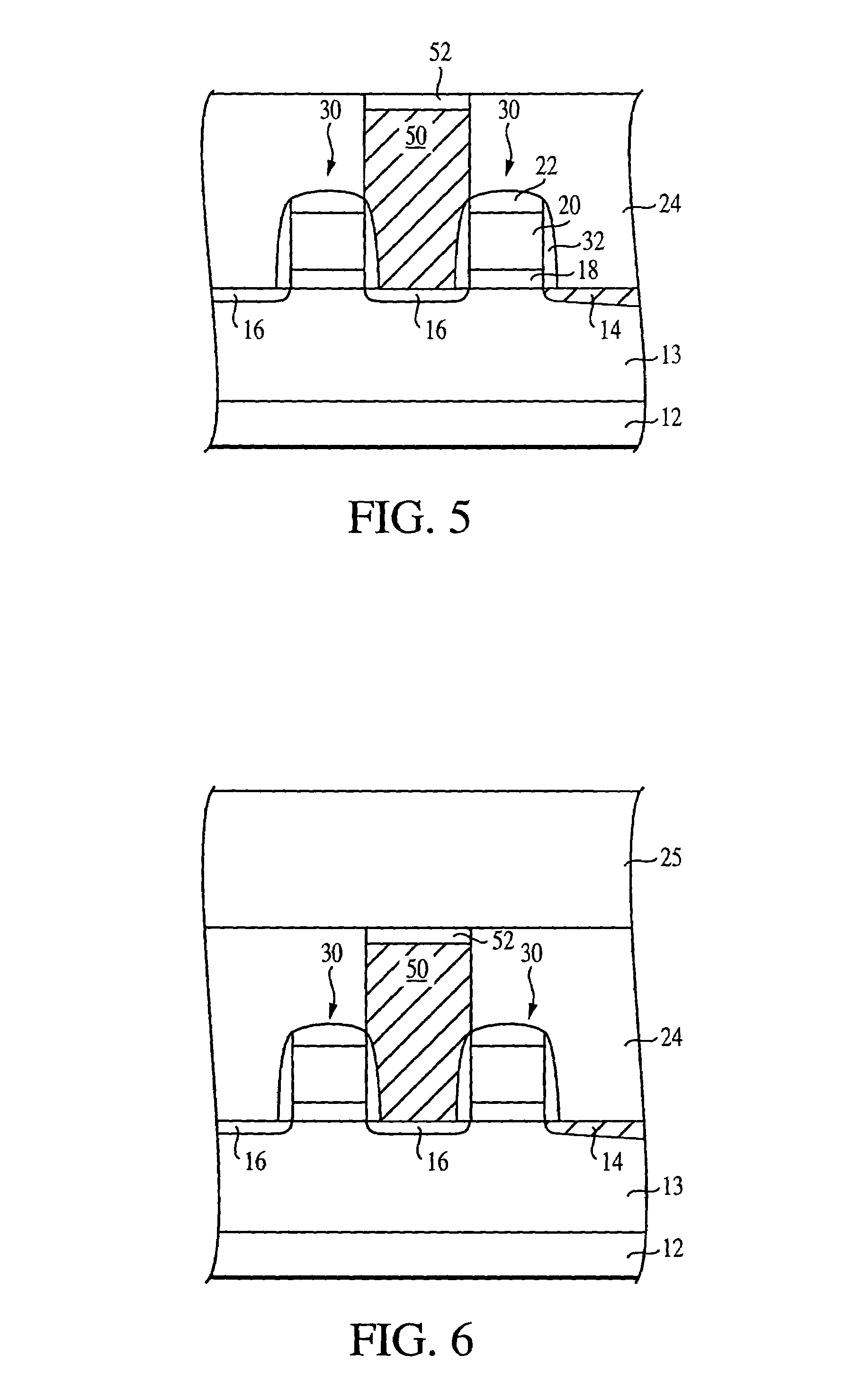

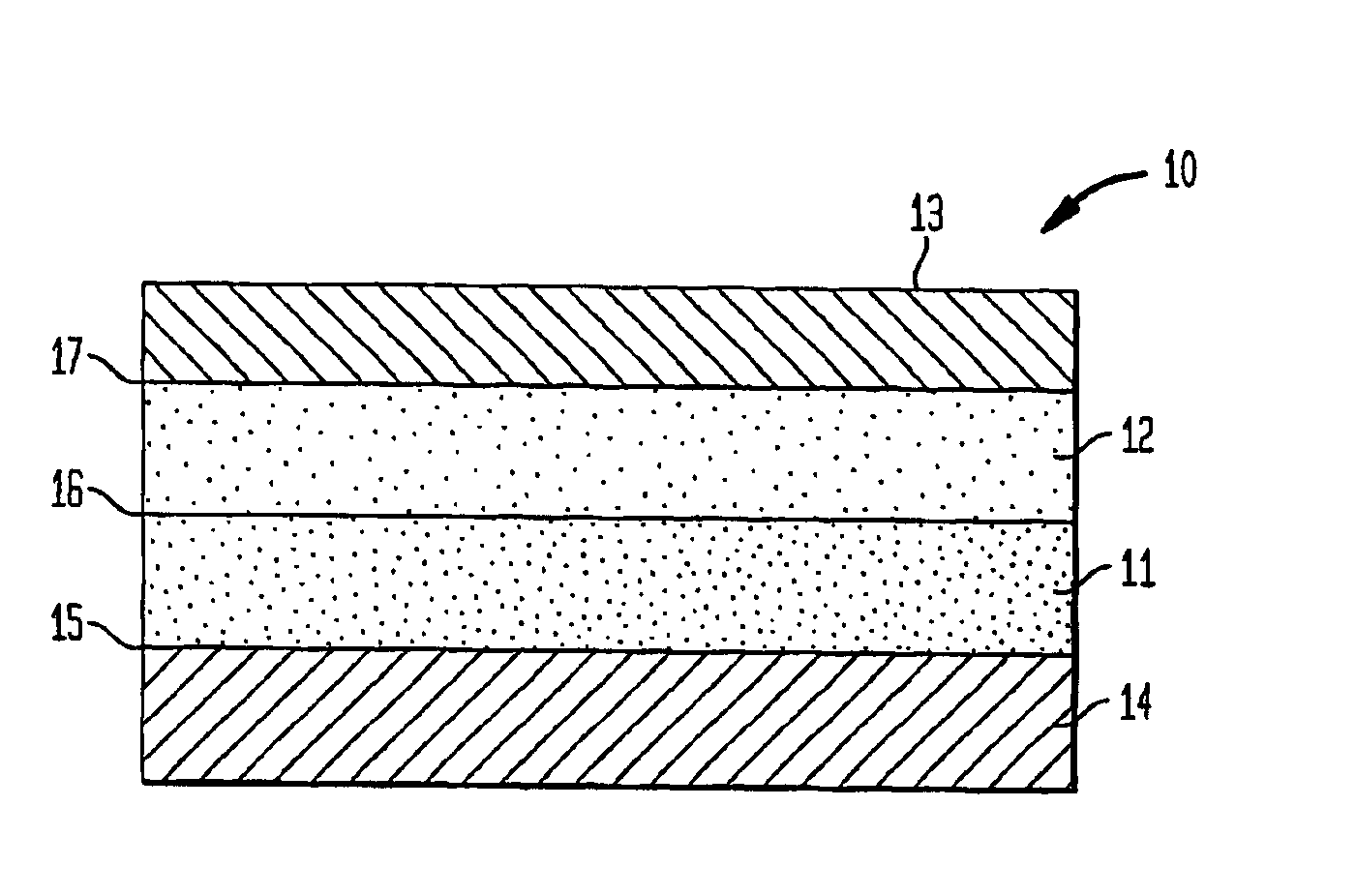

Method of forming MIS capacitor

InactiveUS7029985B2Reduce leakage currentIncrease capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLow leakage

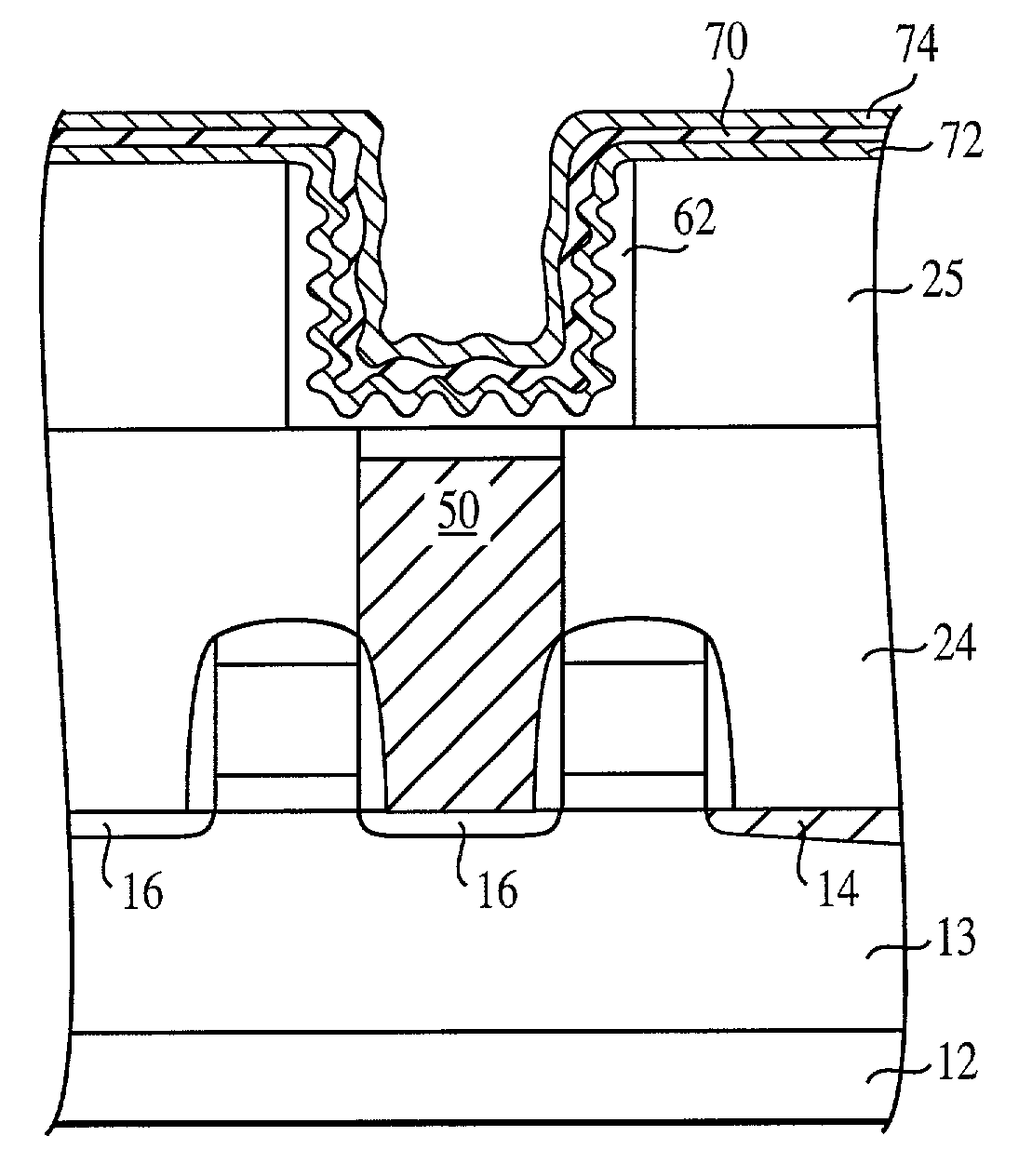

An MIS capacitor with low leakage and high capacitance is disclosed. A layer of hemispherical grained polysilicon (HSG) is formed as a lower electrode. Prior to the dielectric formation, the hemispherical grained polysilicon layer may be optionally subjected to a nitridization or anneal process. A dielectric layer of aluminum oxide (Al2O3), or a composite stack of interleaved layers of aluminum oxide and other metal oxide dielectric materials, is fabricated over the hemispherical grained polysilicon layer and after the optional nitridization or anneal process. The dielectric layer of aluminum oxide (Al2O3) or the aluminum oxide composite stack may be optionally subjected to a post-deposition treatment to further increase the capacitance and decrease the leakage current. A metal nitride upper electrode is formed over the dielectric layer or the composite stack by a deposition technique or by atomic layer deposition.

Owner:ROUND ROCK RES LLC

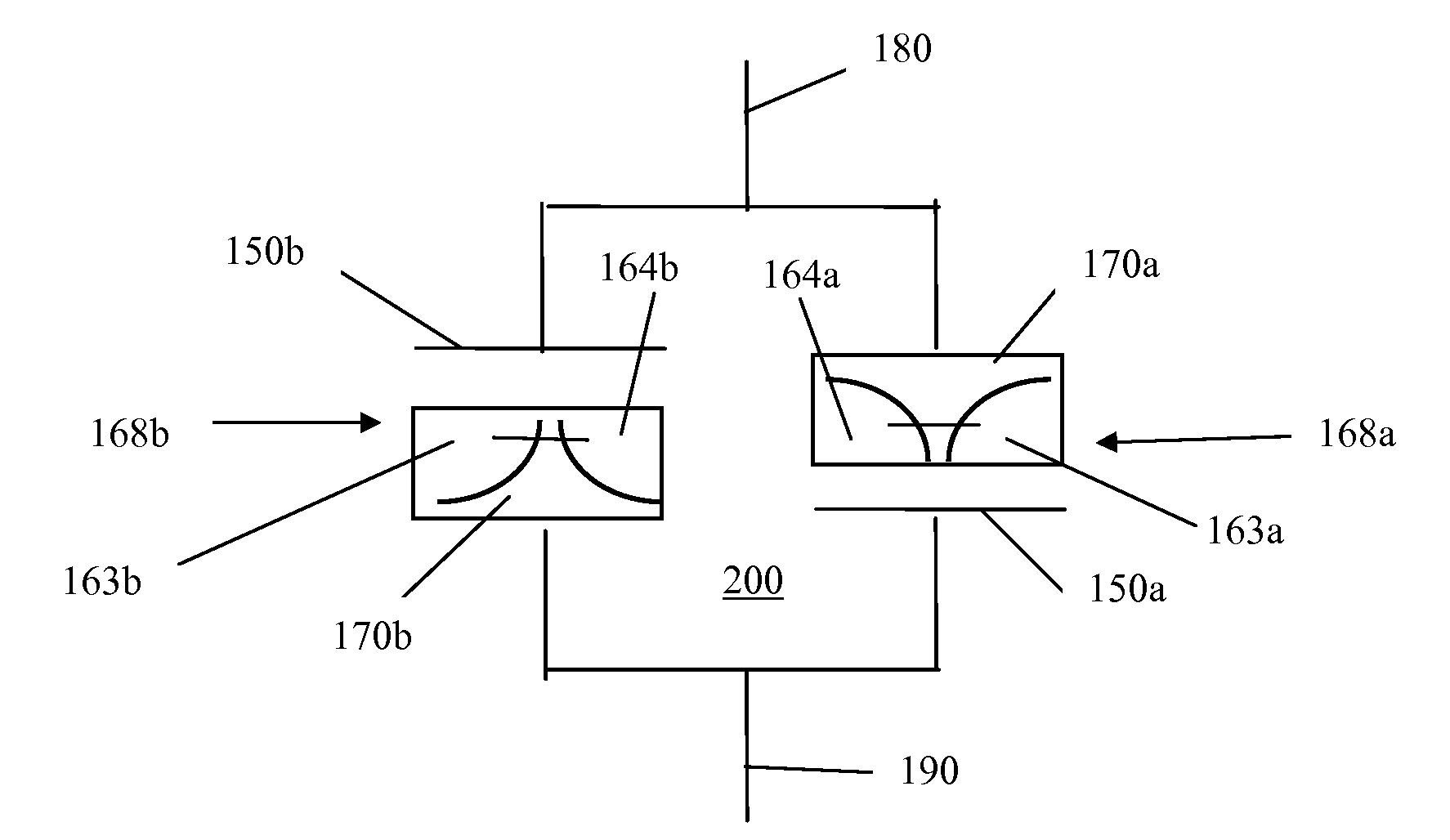

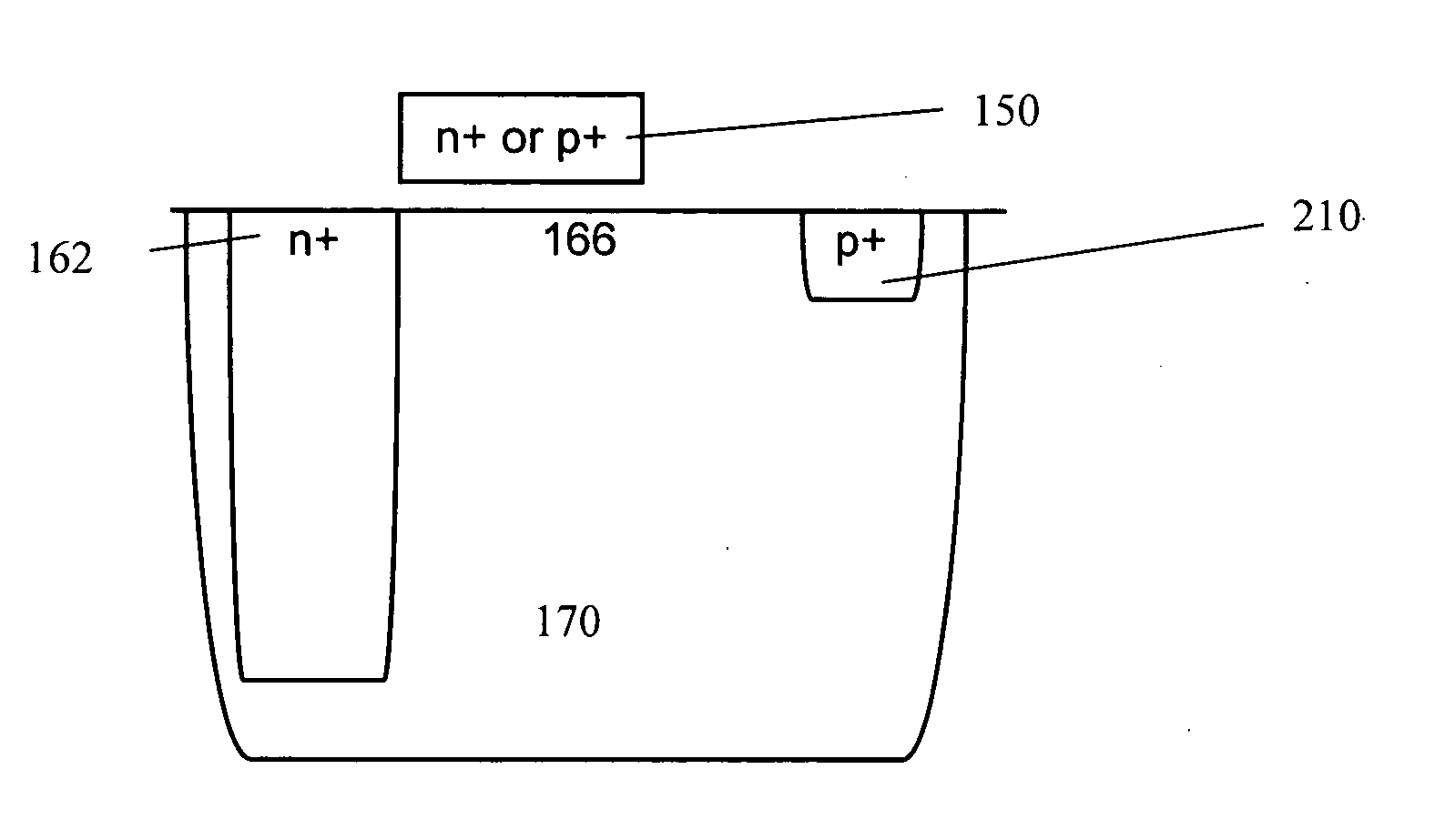

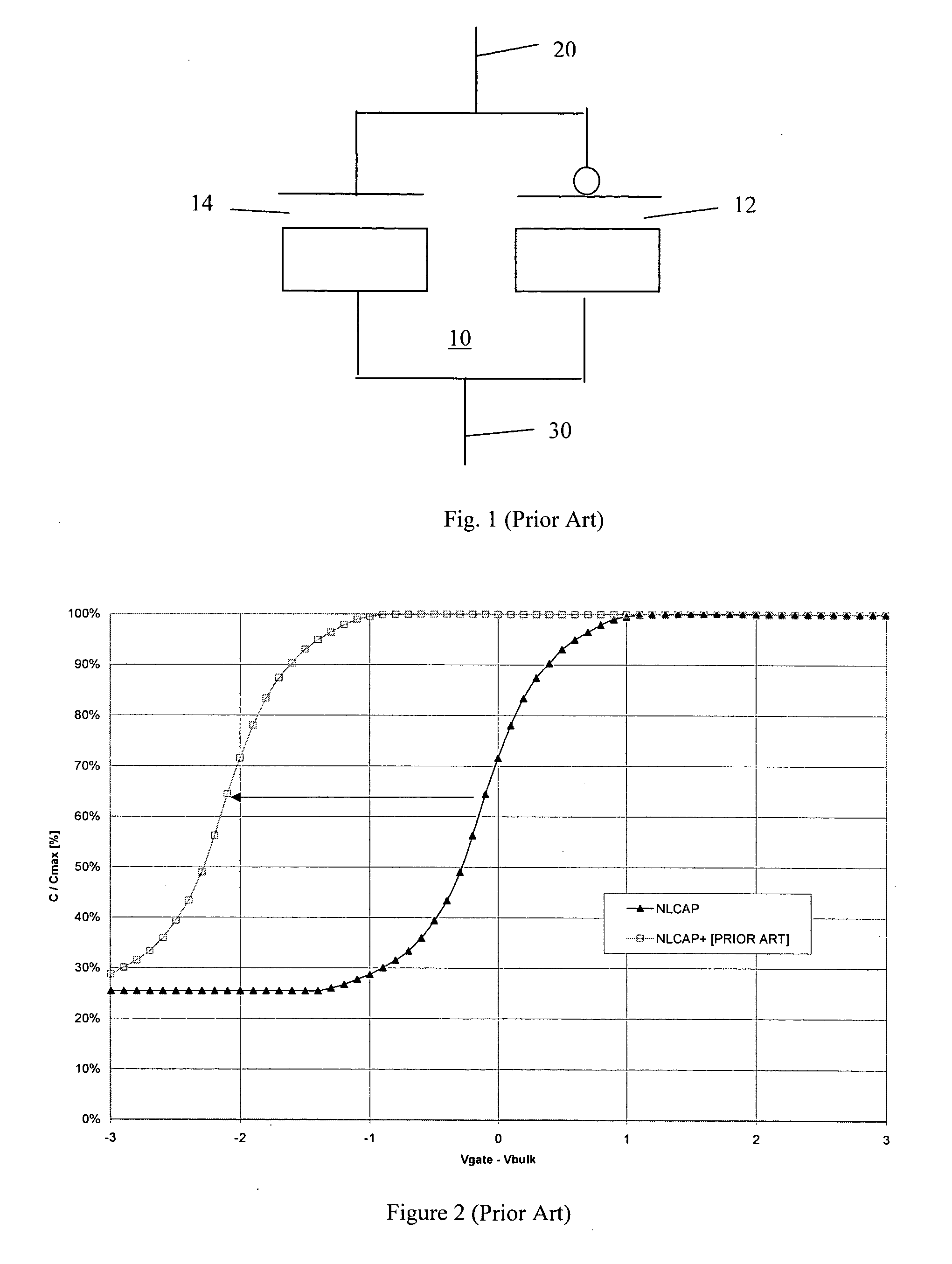

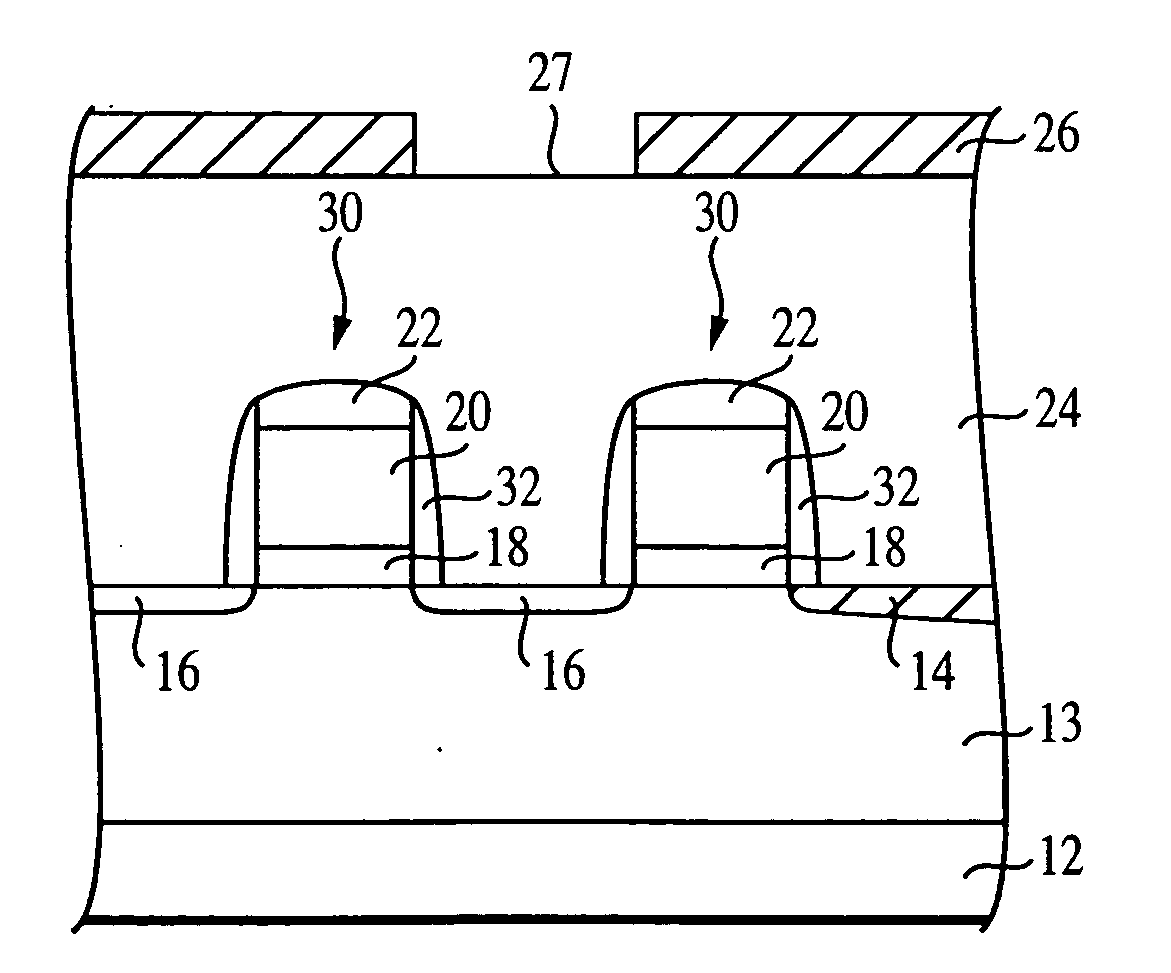

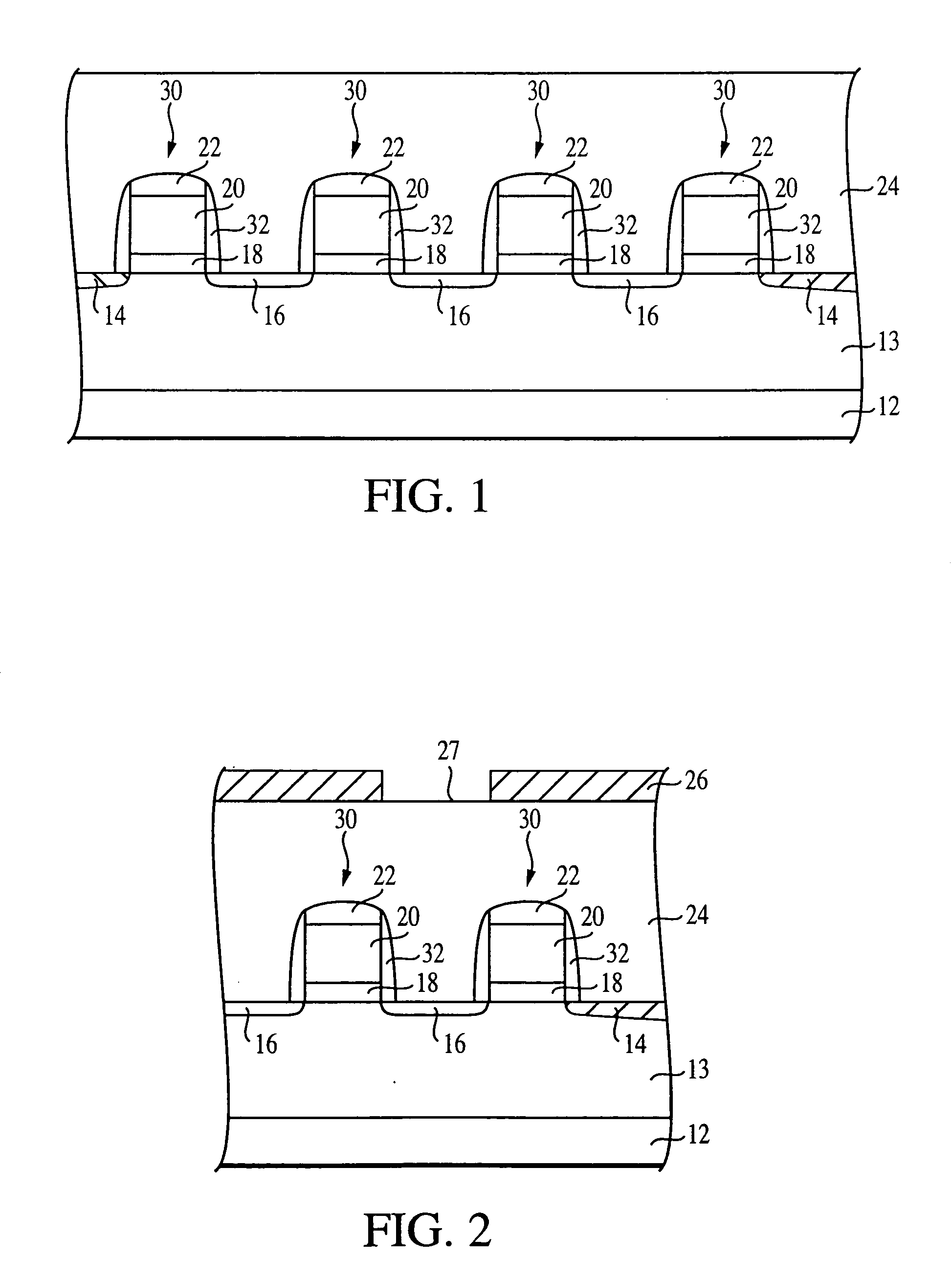

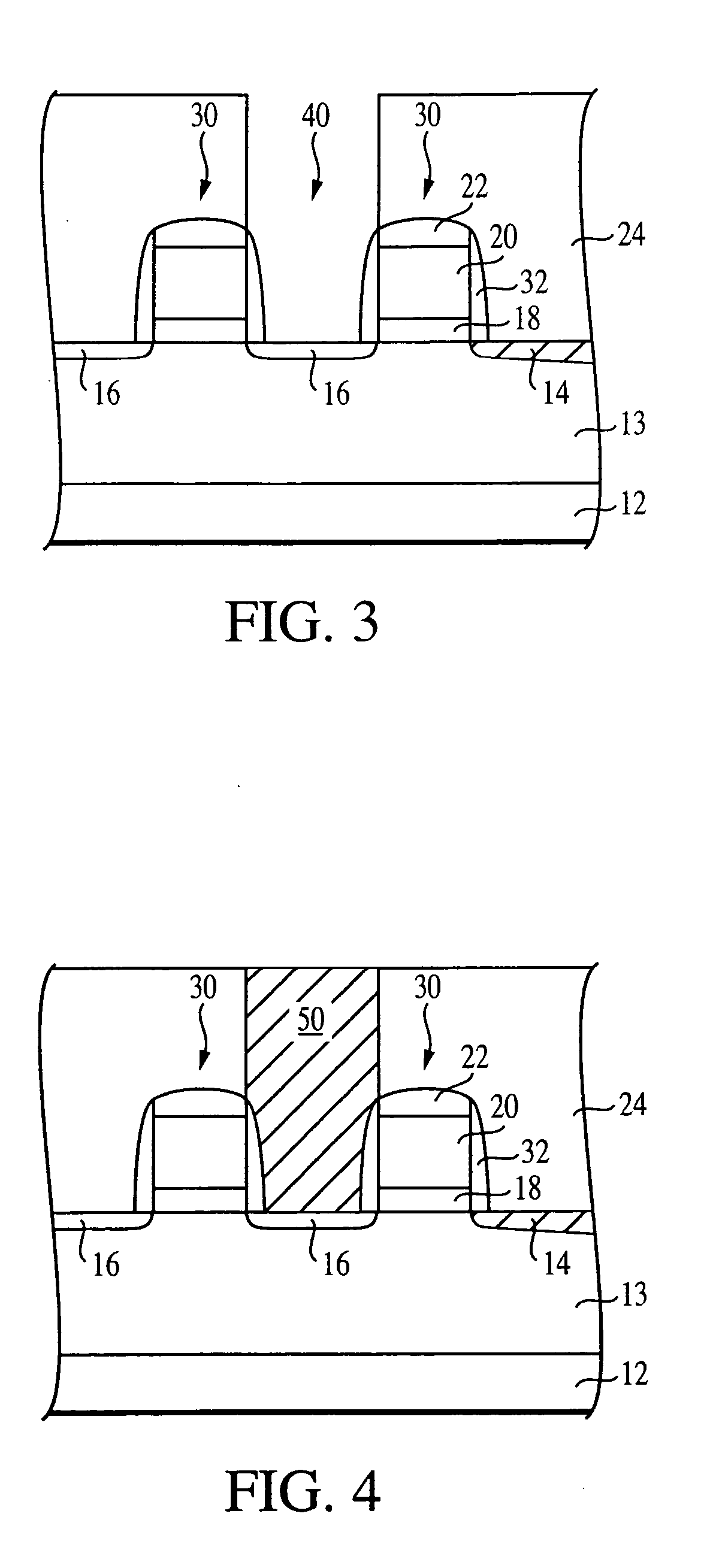

Integrated Semiconductor Metal-Insulator-Semiconductor Capacitor

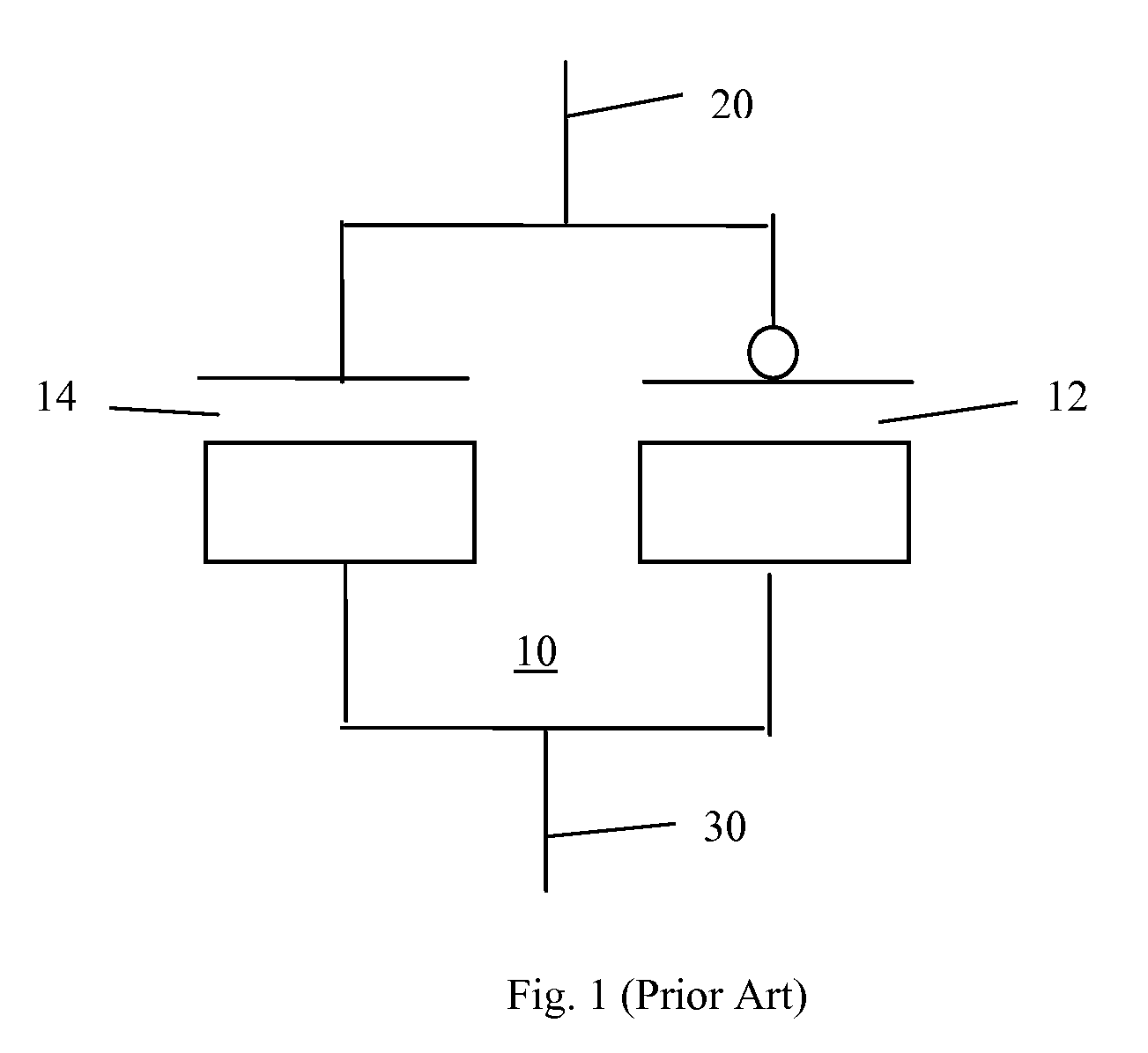

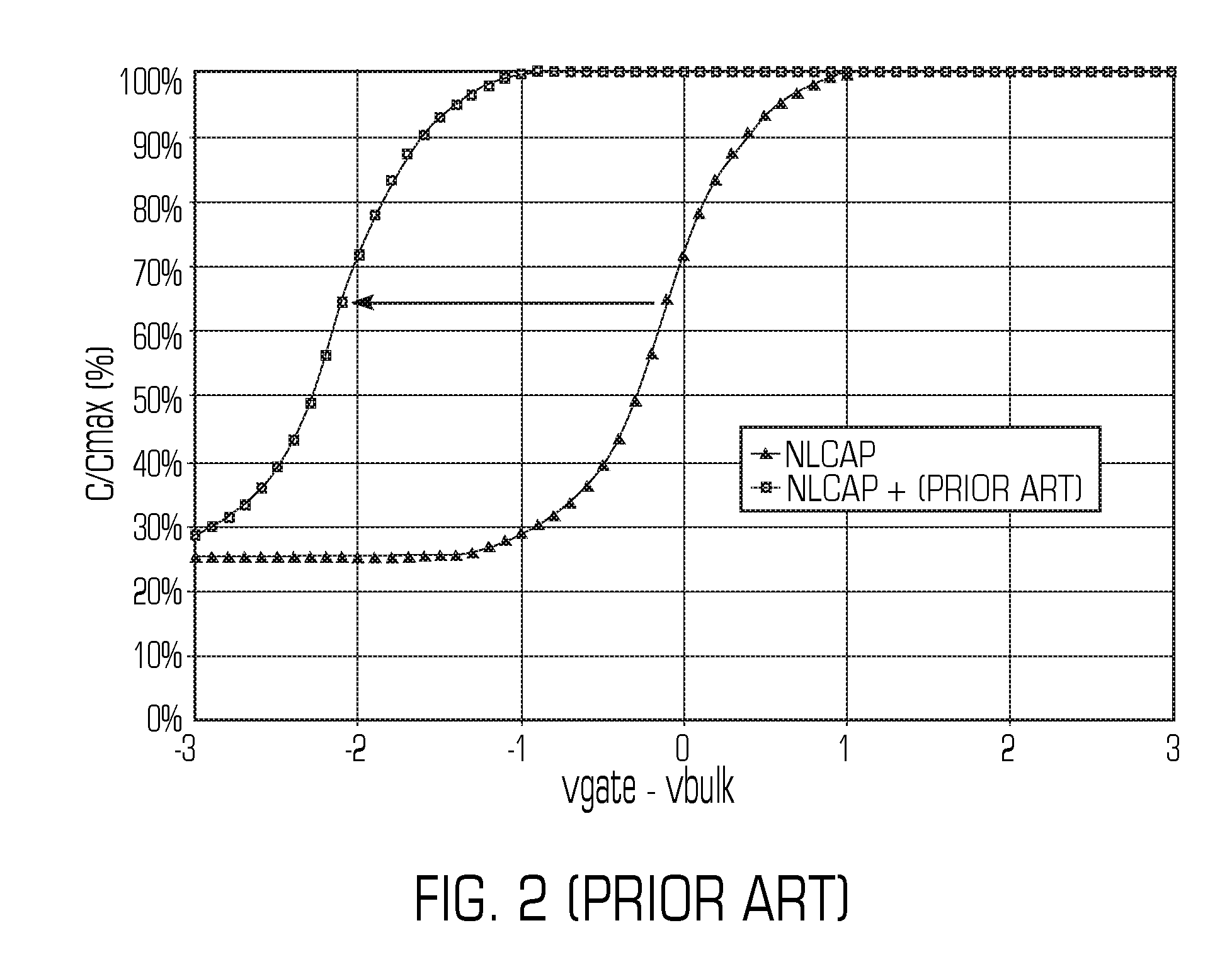

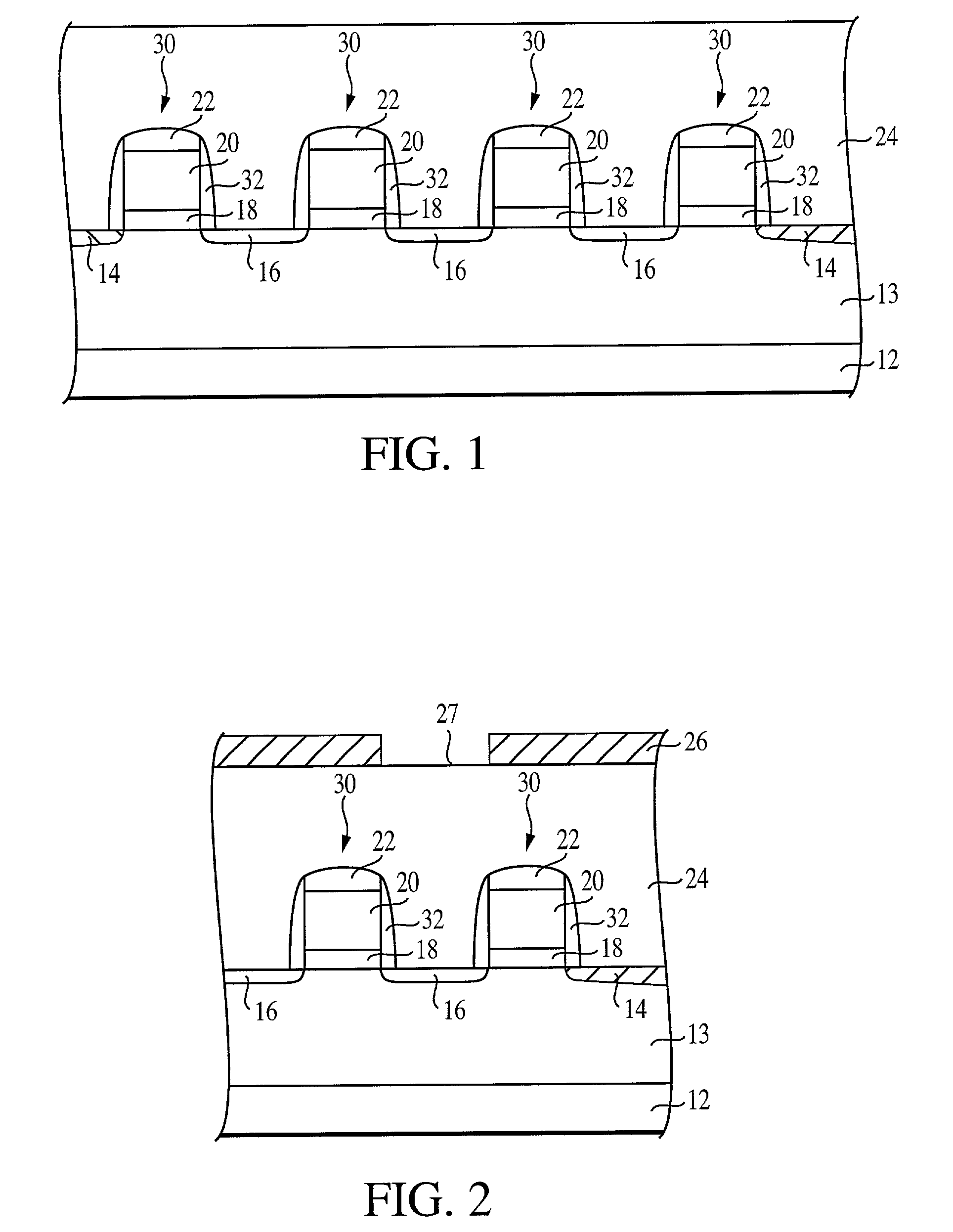

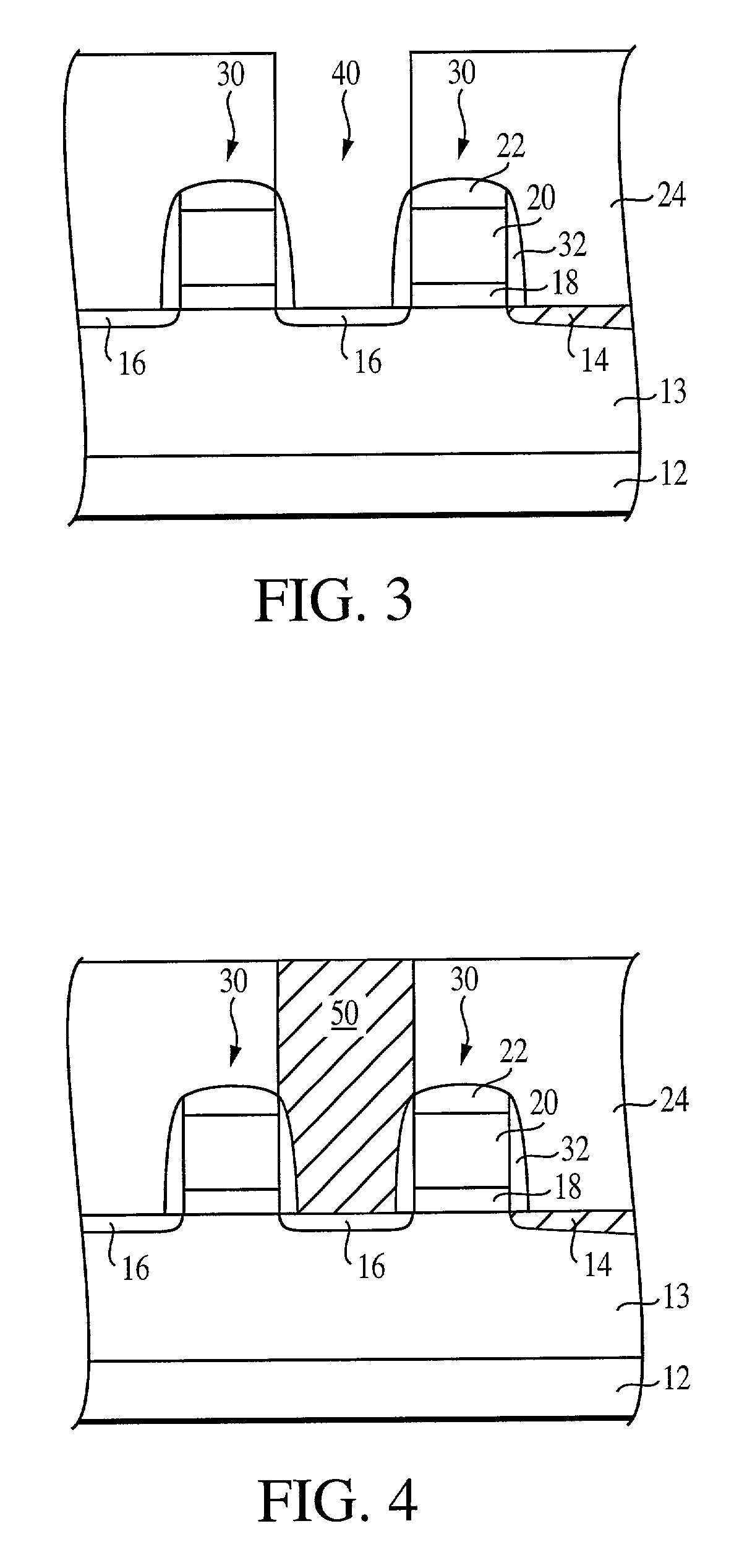

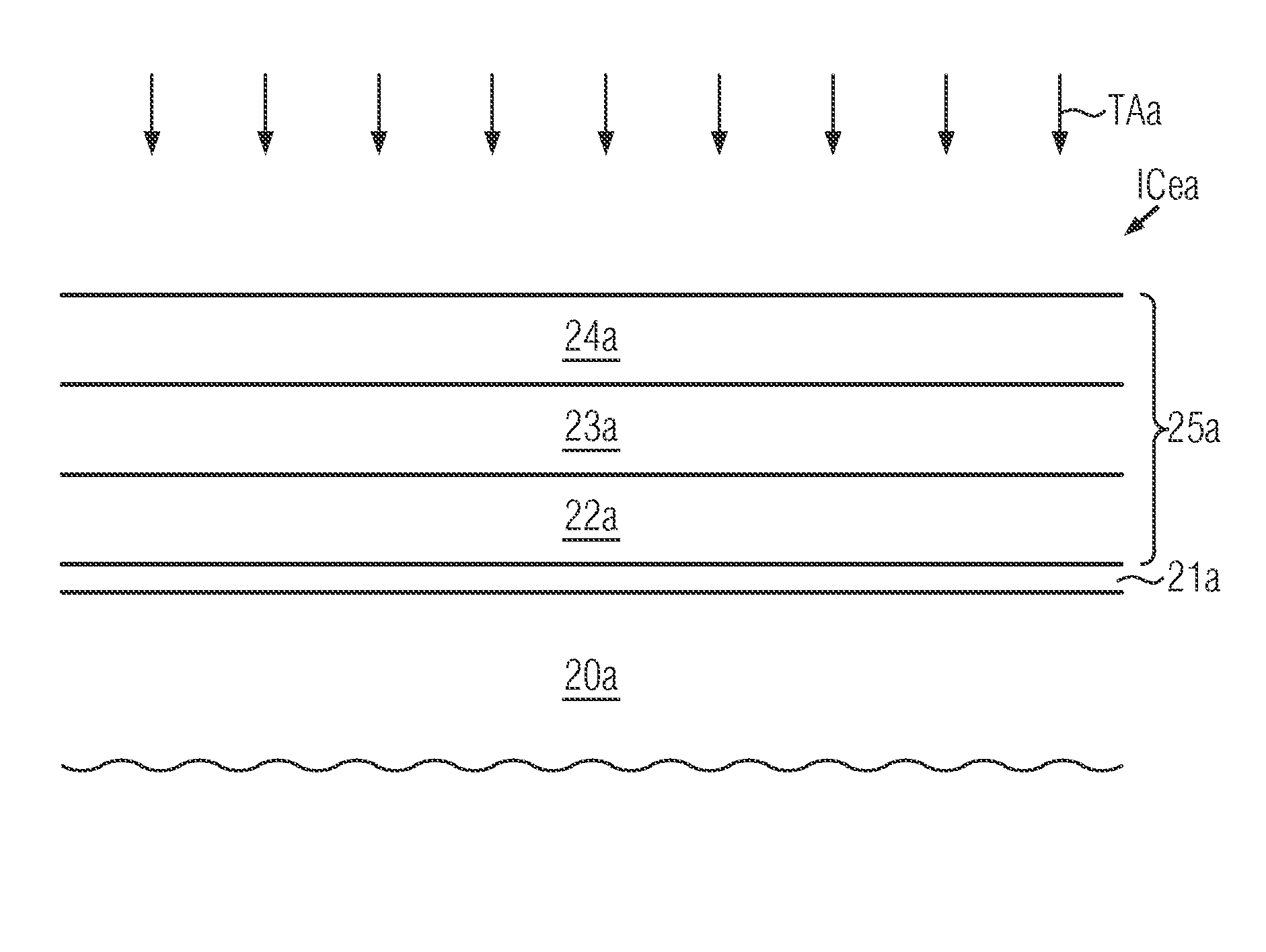

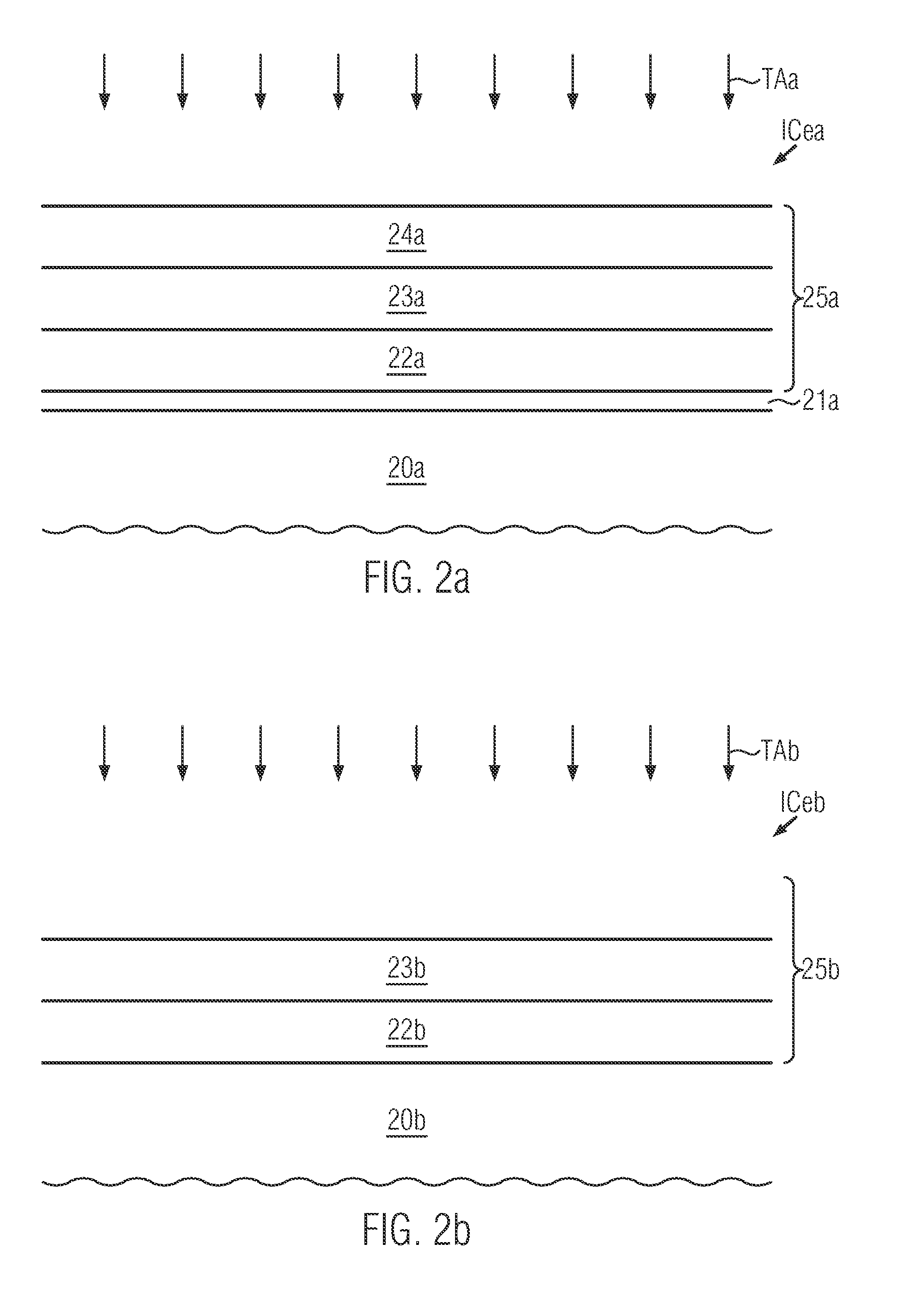

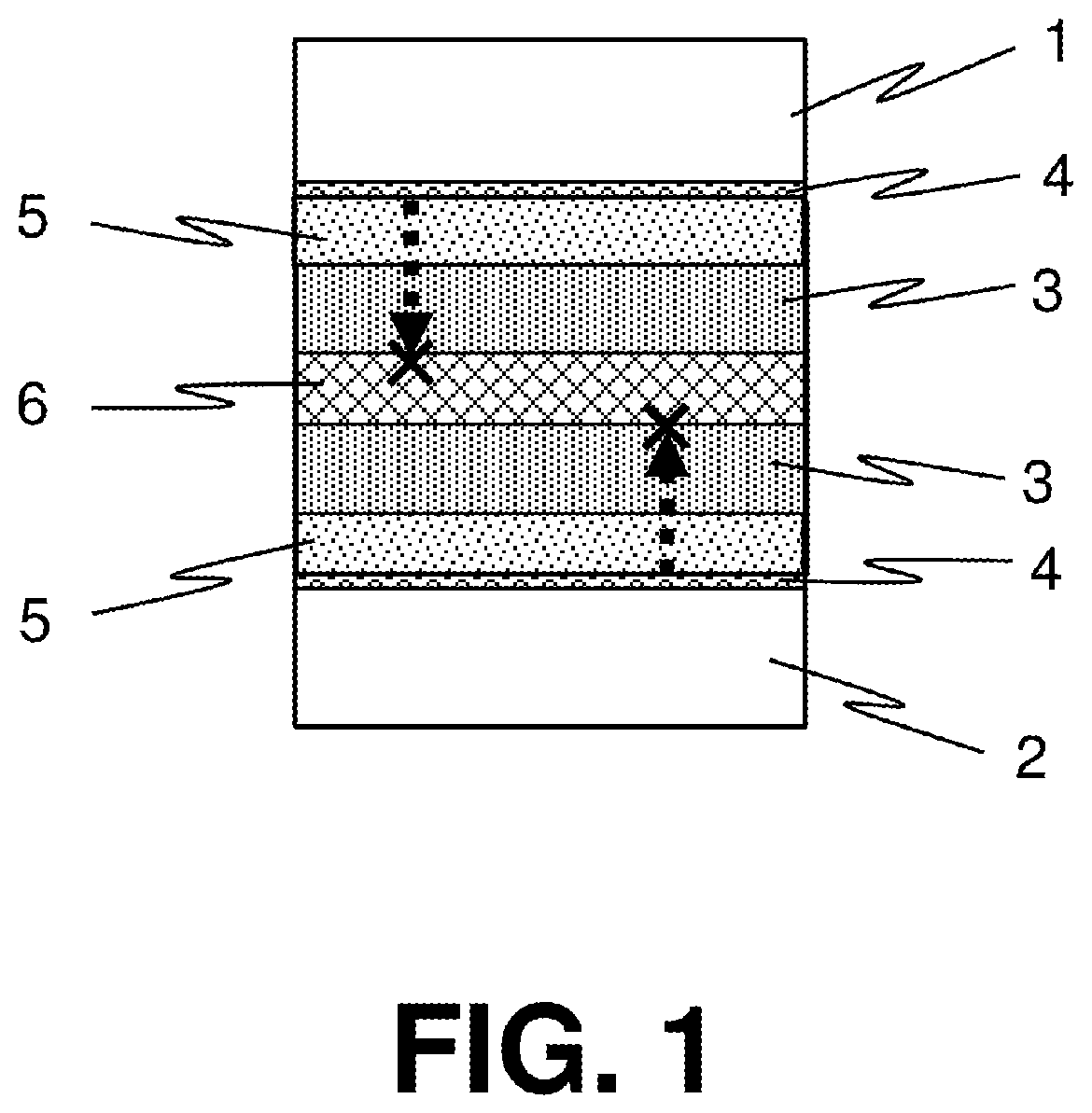

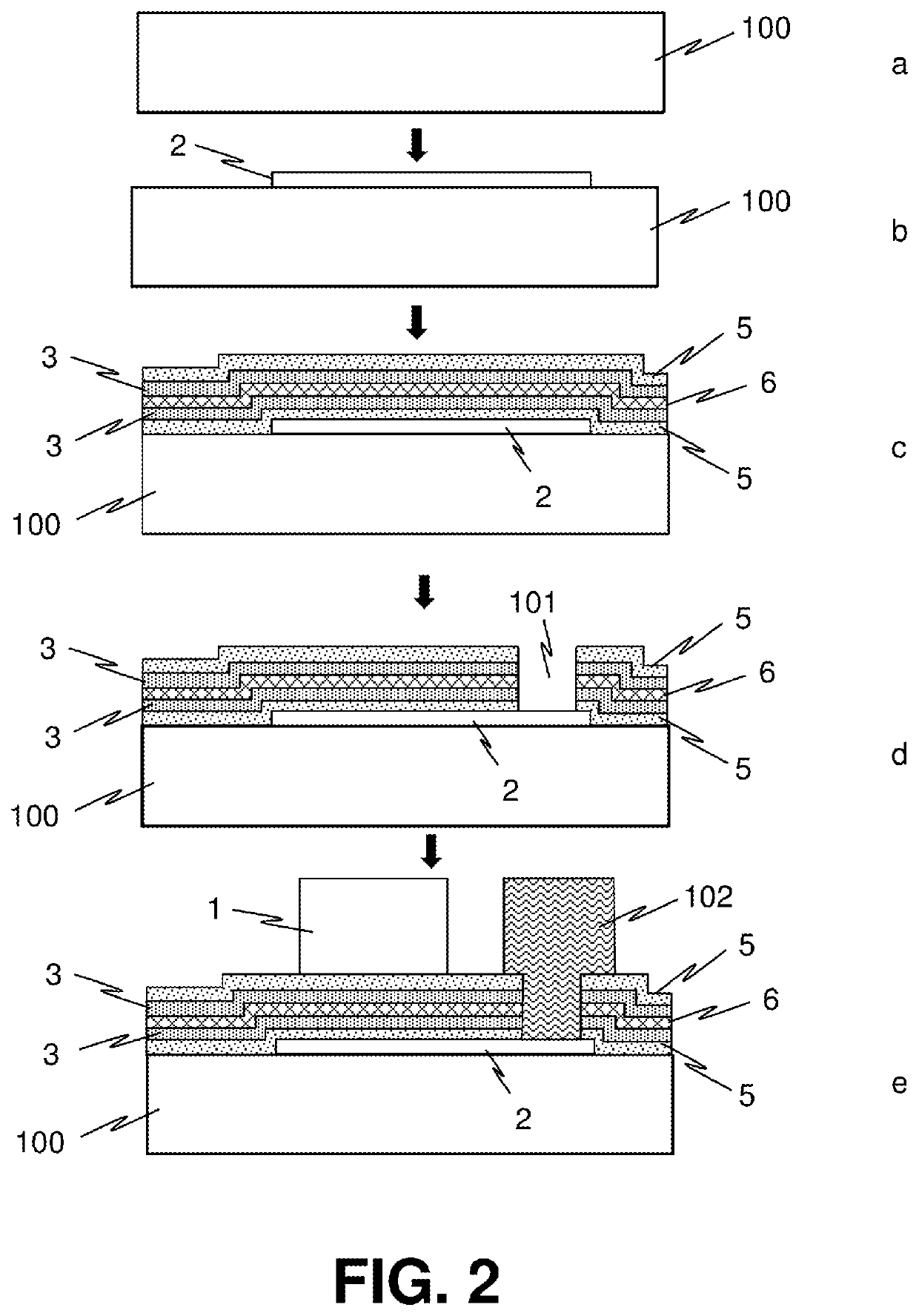

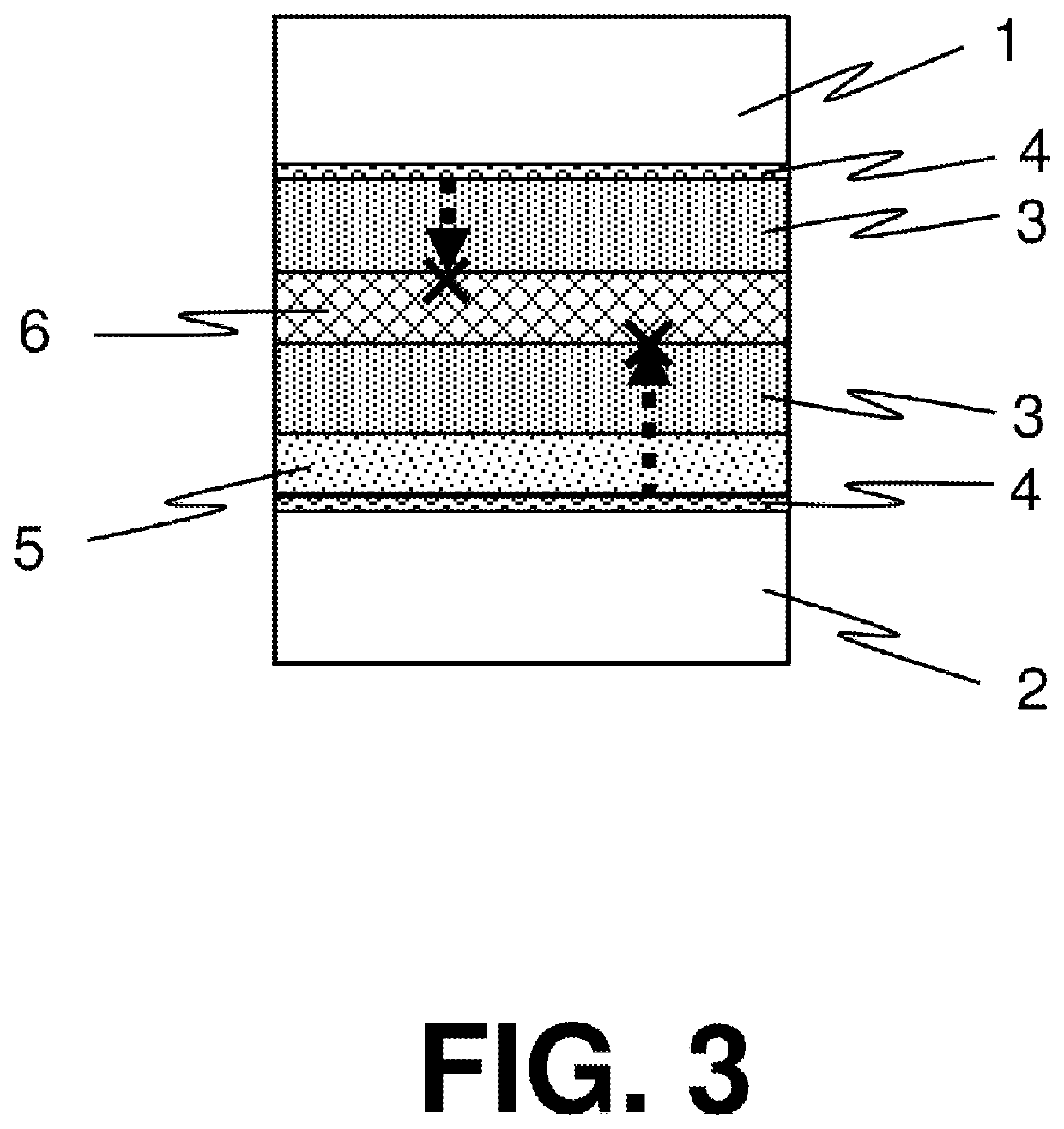

An integrated MIS capacitor has two substantially identical MIS capacitors. A first capacitor comprises a first region of a first conductivity type adjacent to a channel region of the first conductivity type in a semiconductor substrate. The semiconductor substrate has a second conductivity type. A gate electrode is insulated and spaced apart from the channel region of the first capacitor. The second capacitor is substantially identical to the first capacitor and is formed in the same semiconductor substrate. The gate electrode of the first capacitor is electrically connected to the first region of the second capacitor and the gate electrode of the second capacitor is electrically connected to the first region of the first capacitor. In this manner, the capacitors are connected in an anti-parallel configuration. A capacitor which has high capacitance densities, low process complexity, ambipolar operation, low voltage and temperature coefficient, low external parasitic resistance and capacitance and good matching characteristics for use in analog designs that can be integrated with existing semiconductor processes results.

Owner:SILICON STORAGE TECHNOLOGY

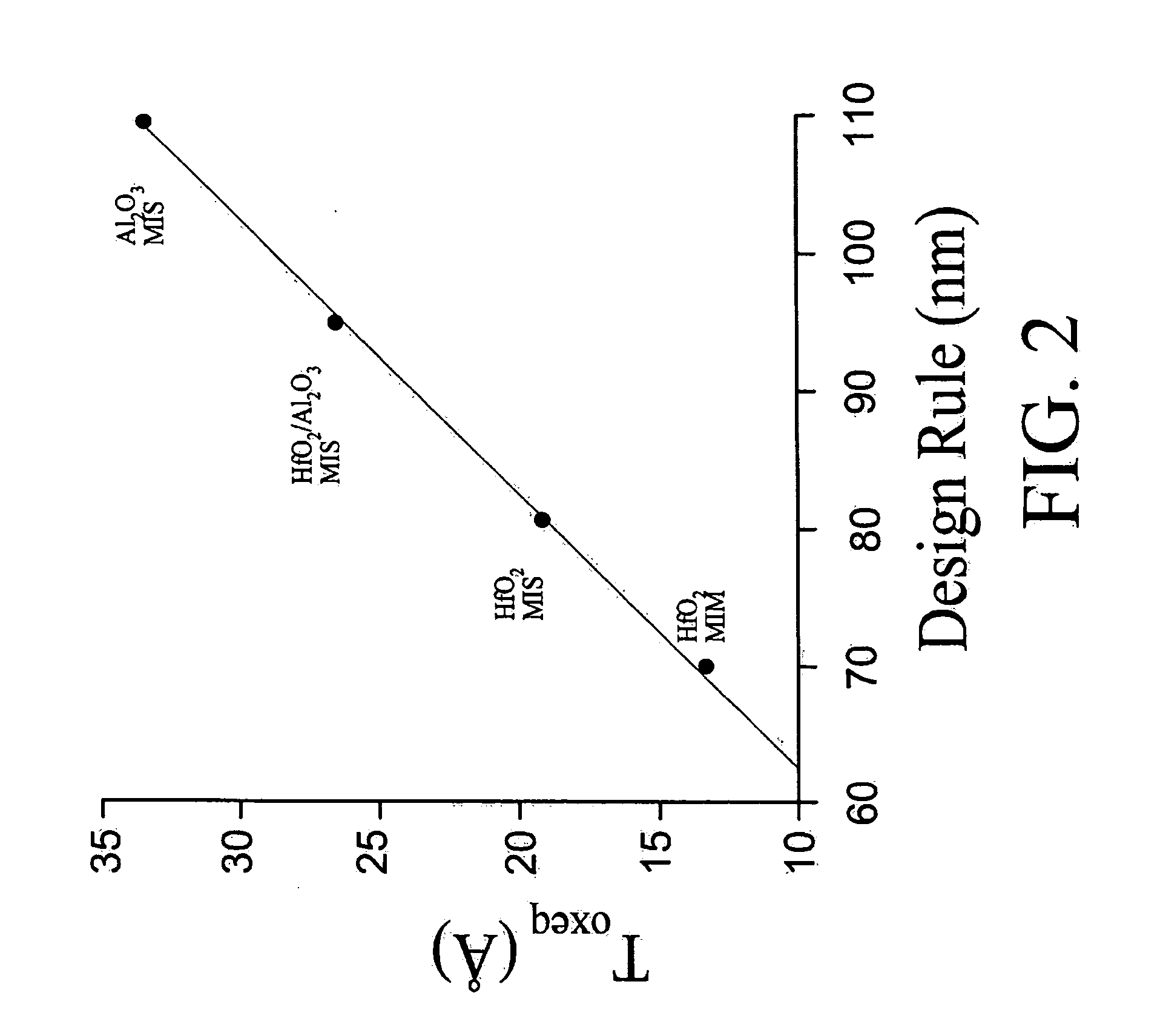

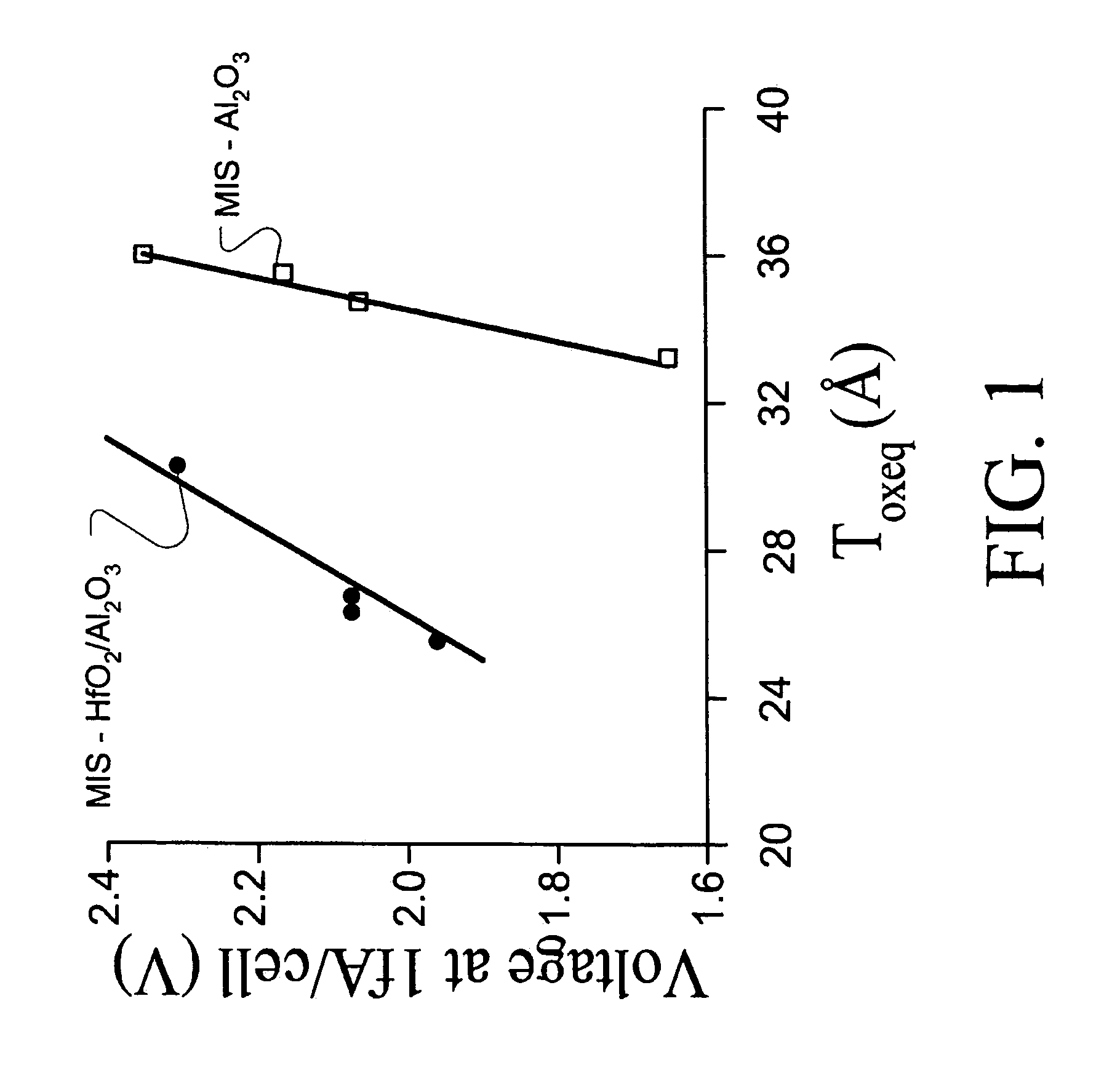

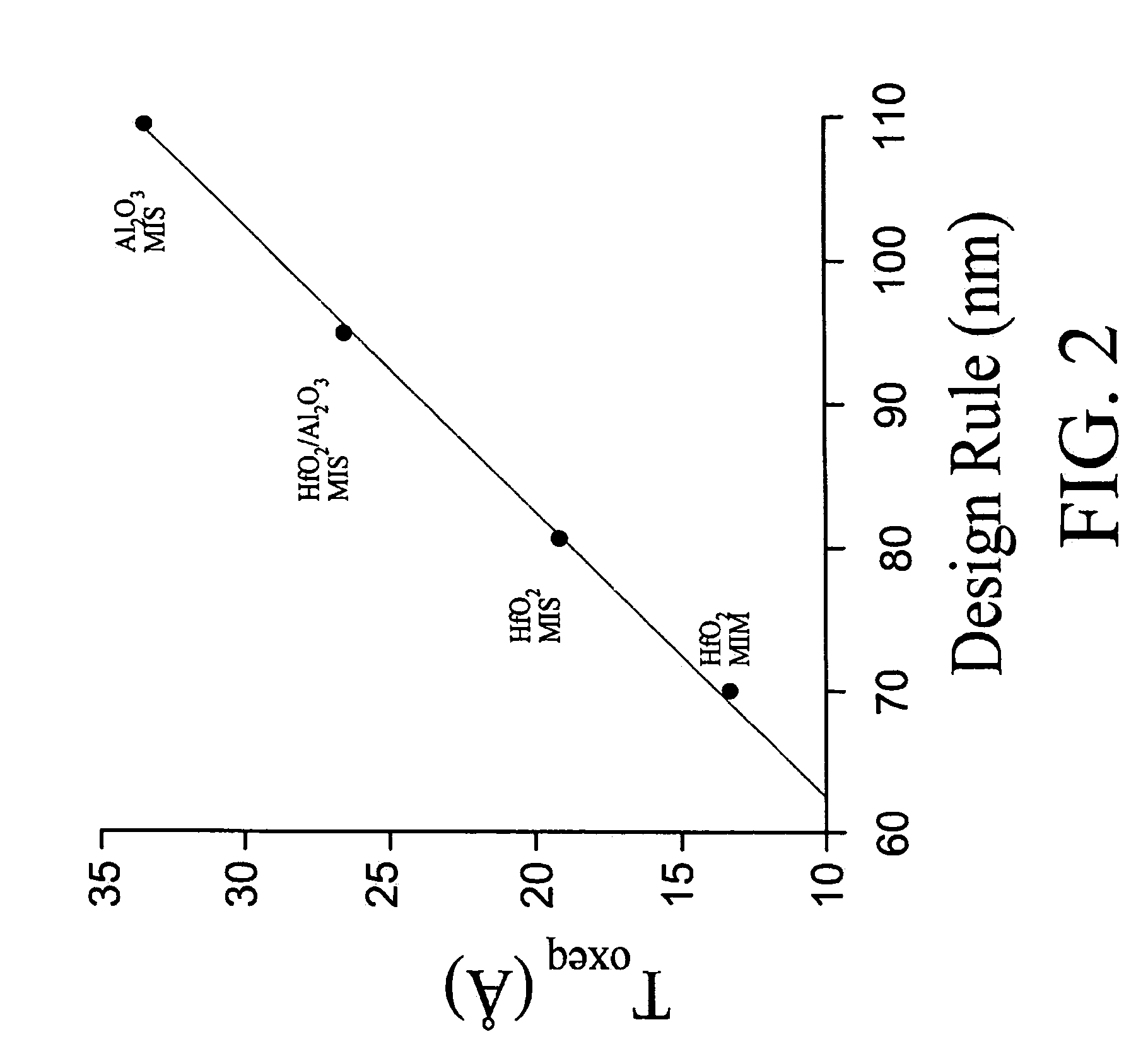

High performance MIS capacitor with HfO2 dielectric

InactiveUS20050070063A1Prevent crystallizationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingMIS capacitorAtomic layer deposition

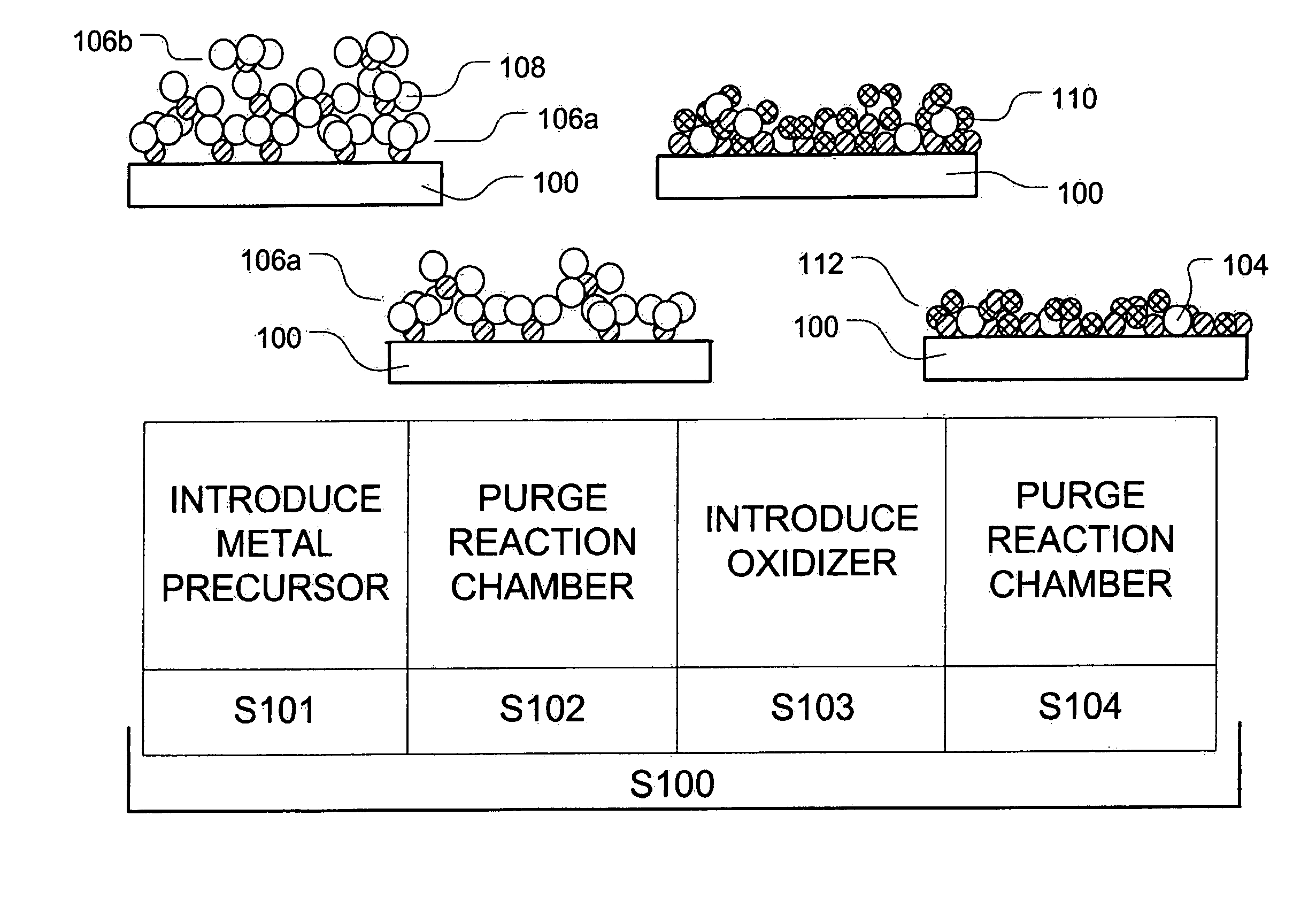

Disclosed is a method for forming metal oxide dielectric layers, more particularly HfO2 dielectric layers, using an atomic layer deposition (ALD) method in which a series of thin intermediate layers are formed and treated with one or more oxidizers and nitrogents before the next intermediate layer is formed on the substrate. The intermediate oxidation treatments reduce the number of organic contaminants incorporated into the metal oxide layer from the organometallic precursors to produce a dielectric layer having improved current leakage characteristics. The dielectric layers formed in this manner remain susceptible to crystallization if exposed to temperatures much above 550° C., so subsequent semiconductor manufacturing processes should be modified or eliminated to avoid such temperatures or limit the duration at such temperatures to maintain the performance of the dielectric materials.

Owner:SAMSUNG ELECTRONICS CO LTD

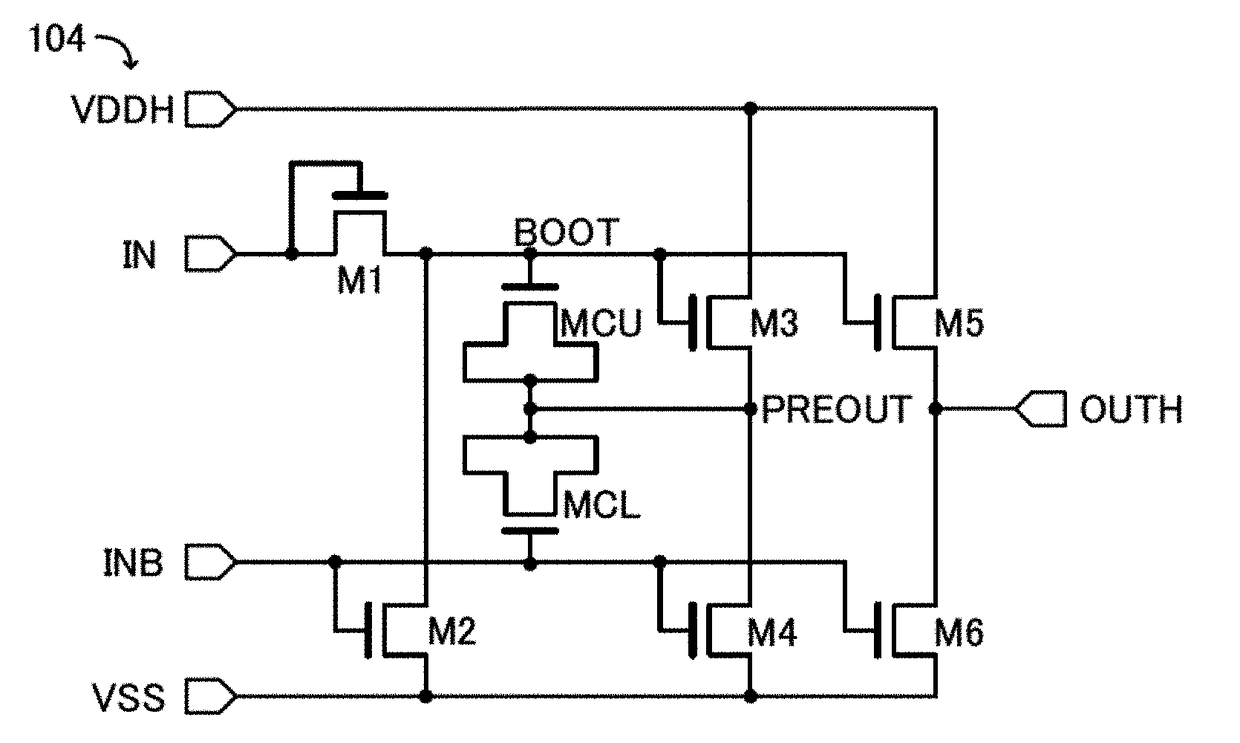

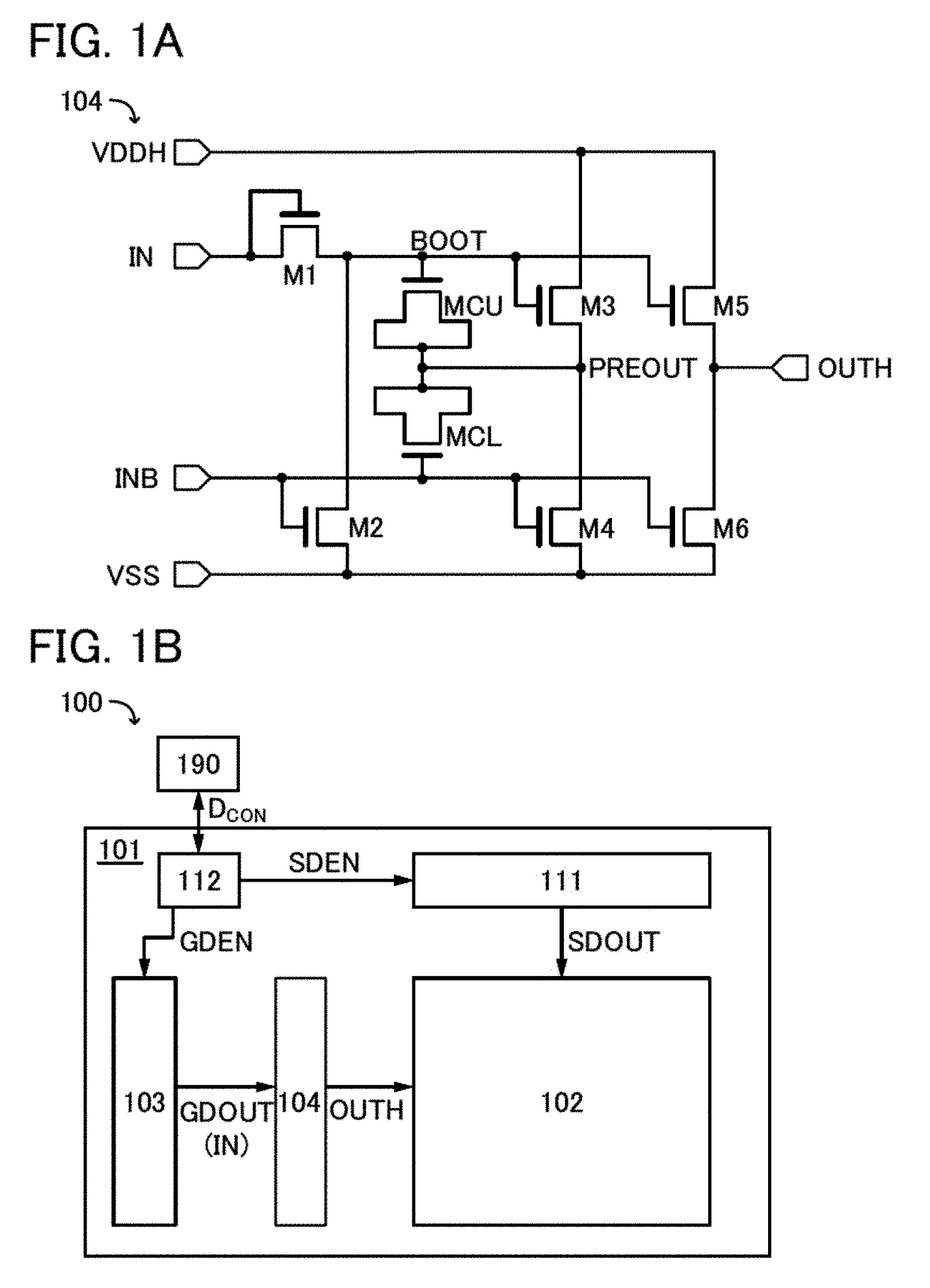

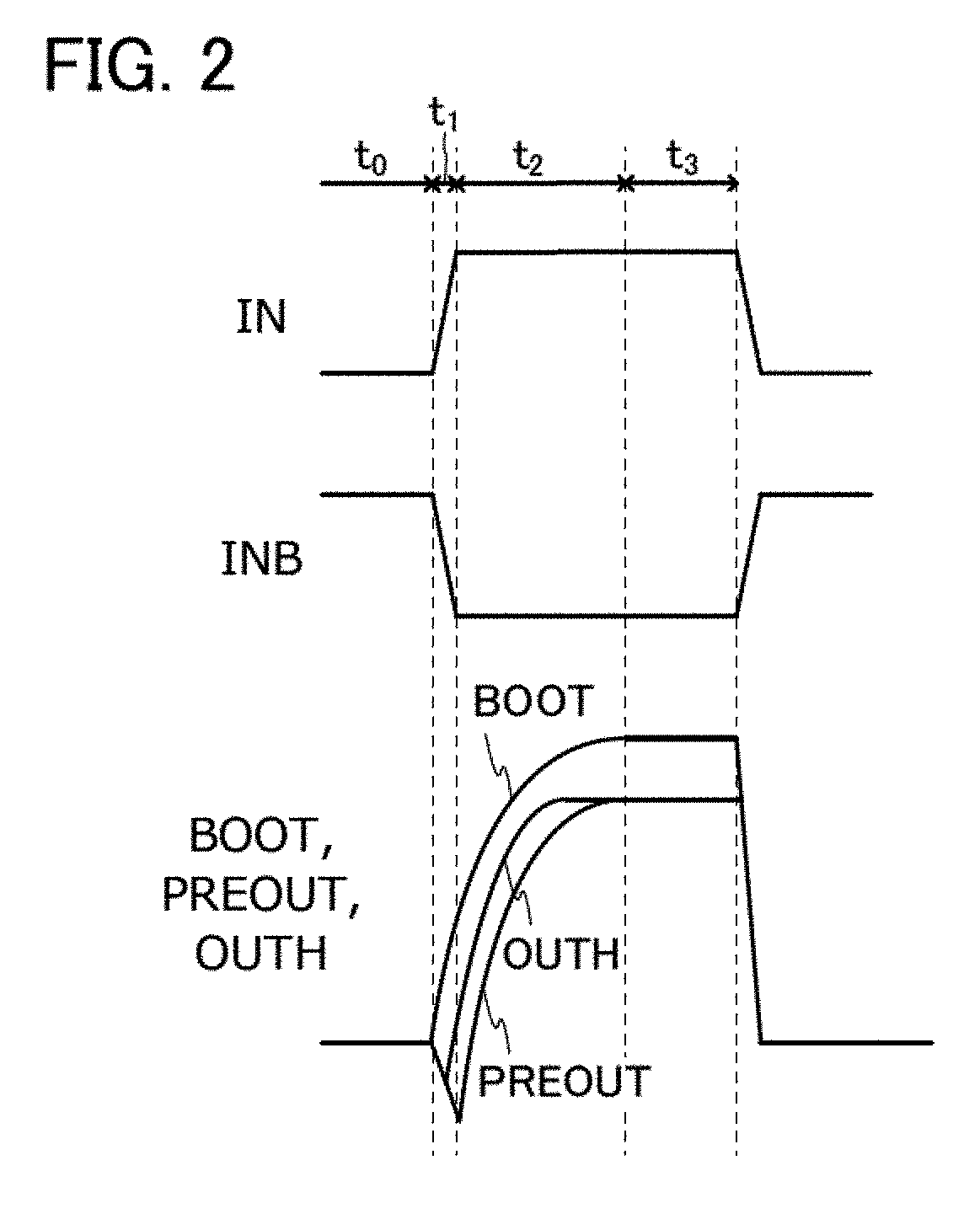

Semiconductor device, display device, and electronic device

ActiveUS20180151593A1Reduce power consumptionReduce in quantityStatic indicating devicesSolid-state devicesDevice materialDisplay device

A level shifter including a transistor that can be formed through the same process as a display portion is provided. A semiconductor device serves as a level shifter including transistors having the same conductivity type. The semiconductor device includes a so-called MIS capacitor in which metal, an insulator, and a semiconductor are stacked as a capacitor for boosting an input signal. Since the MIS capacitor is used, the gate-source voltage of a transistor for generating an output signal can be increased. Thus, boosting operation to generate the output signal can be performed more surely.

Owner:SEMICON ENERGY LAB CO LTD

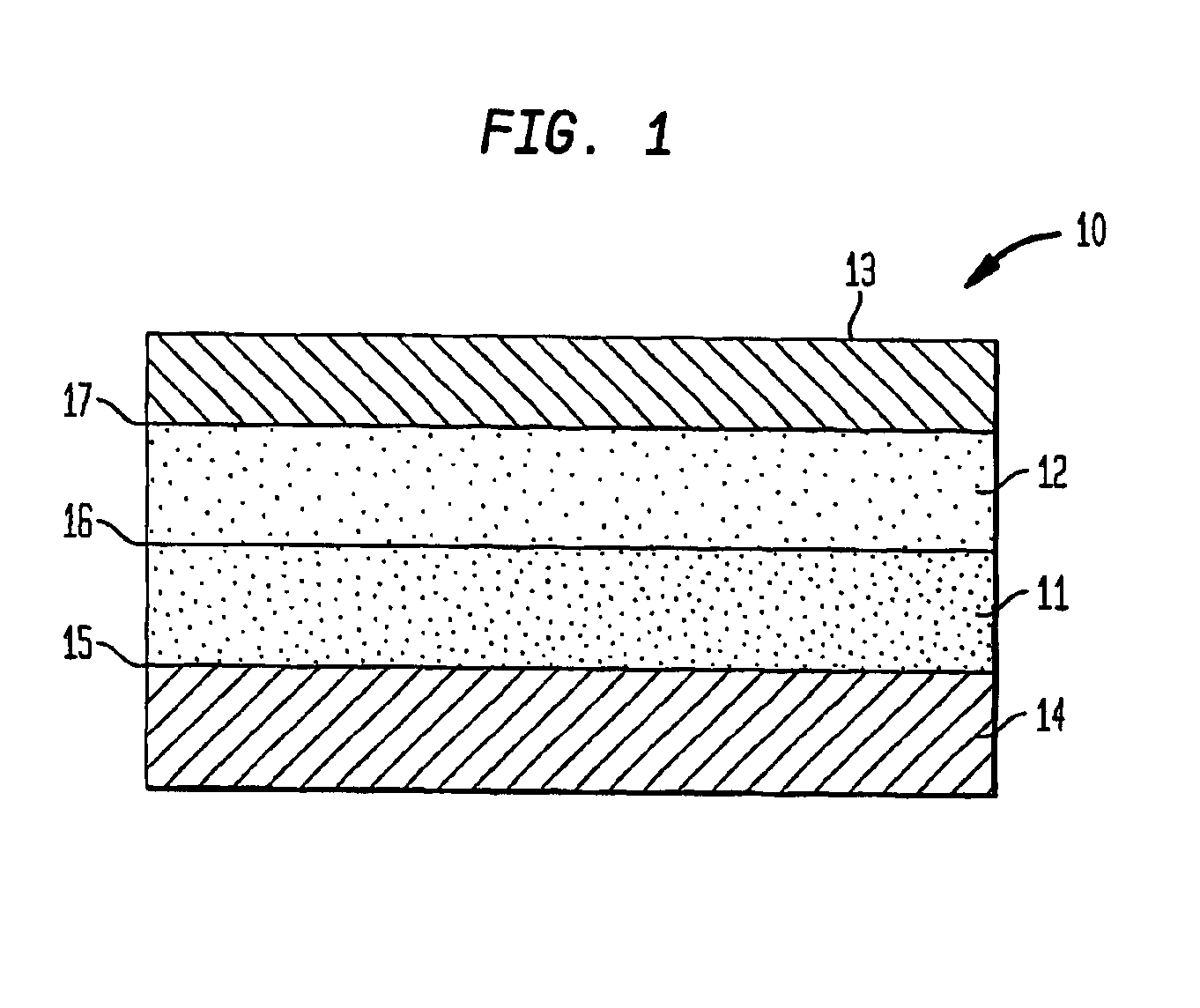

MIS hydrogen sensors

InactiveUS6935158B2Analysing fluids using sonic/ultrasonic/infrasonic wavesSemiconductor/solid-state device manufacturingThin metalRectifier diodes

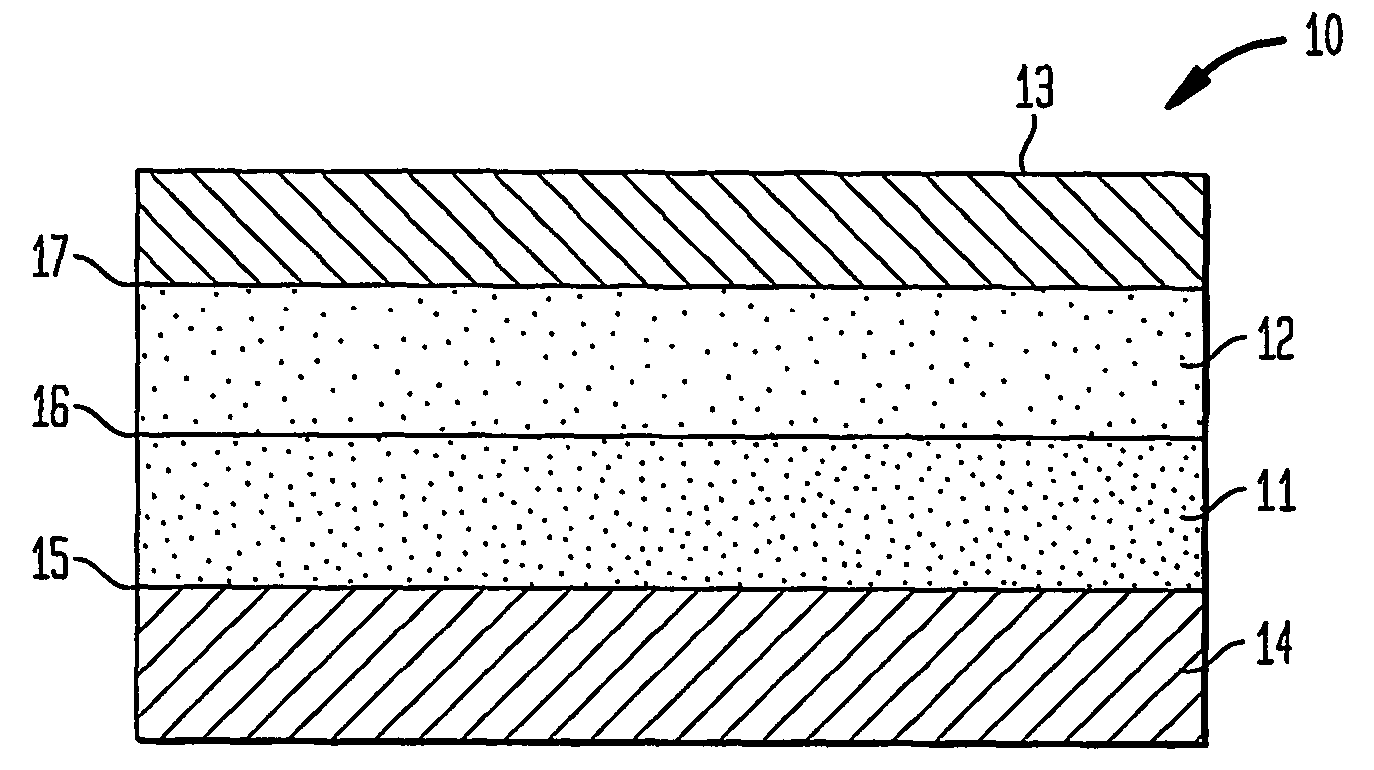

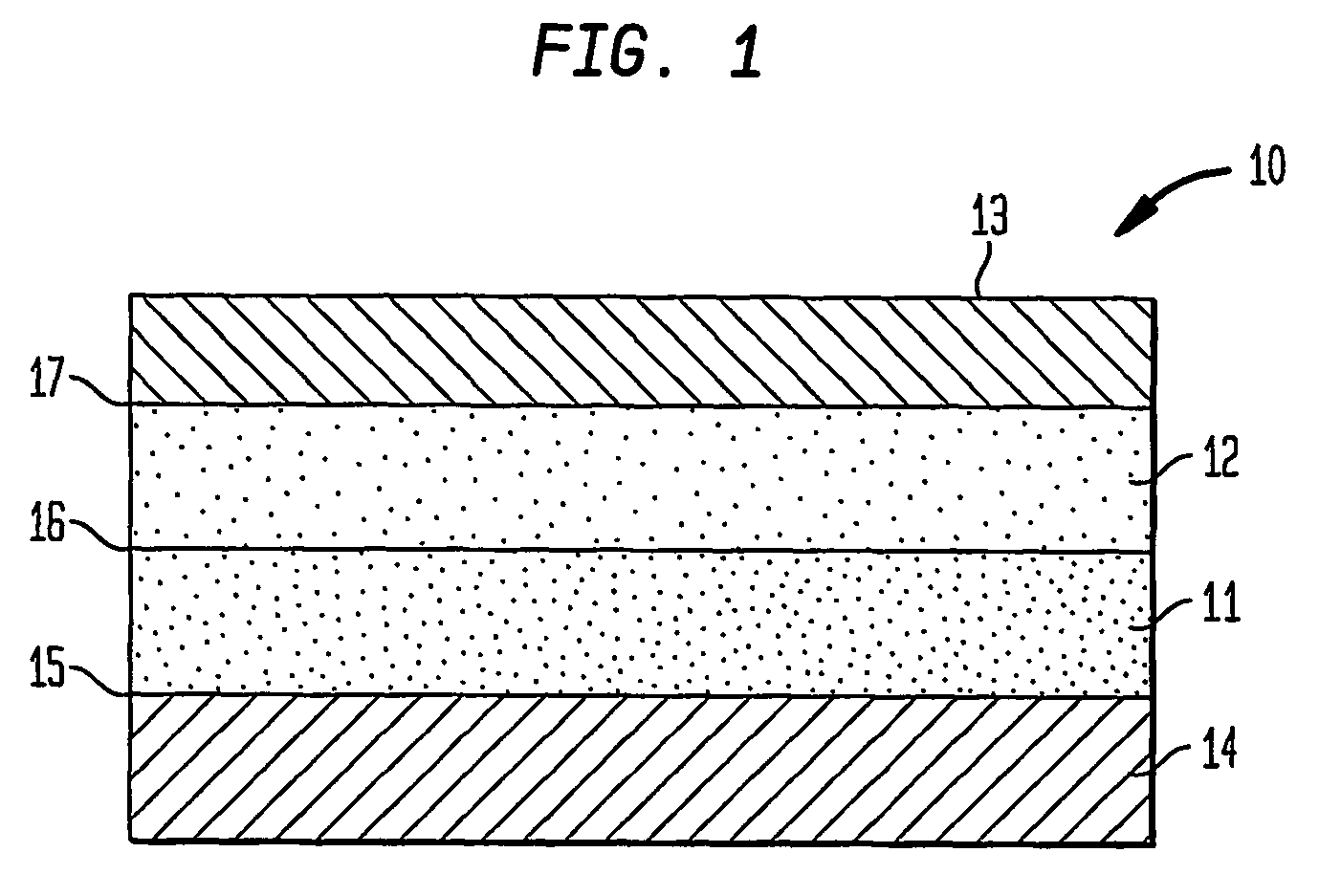

Hydrogen gas sensors employ an epitaxial layer of the thermodynamically stable form of aluminum nitride (AlN) as the “insulator” in an MIS structure having a thin metal gate electrode suitable for catalytic dissociate of hydrogen, such as palladium, on a semiconductor substrate. The AlN is deposited by a low temperature technique known as Plasma Source Molecular Beam Epitaxy (PSMBE). When silicon (Si) is used the semiconducting substrate, the electrical behavior of the device is that of a normal nonlinear MIS capacitor. When a silicon carbide (SiC) is used, the electrical behavior of the device is that of a rectifying diode. Preferred structures are Pd / AlN / Si and Pd / AlN / SiC wherein the SiC is preferably 6H—SiC.

Owner:WAYNE STATE UNIV

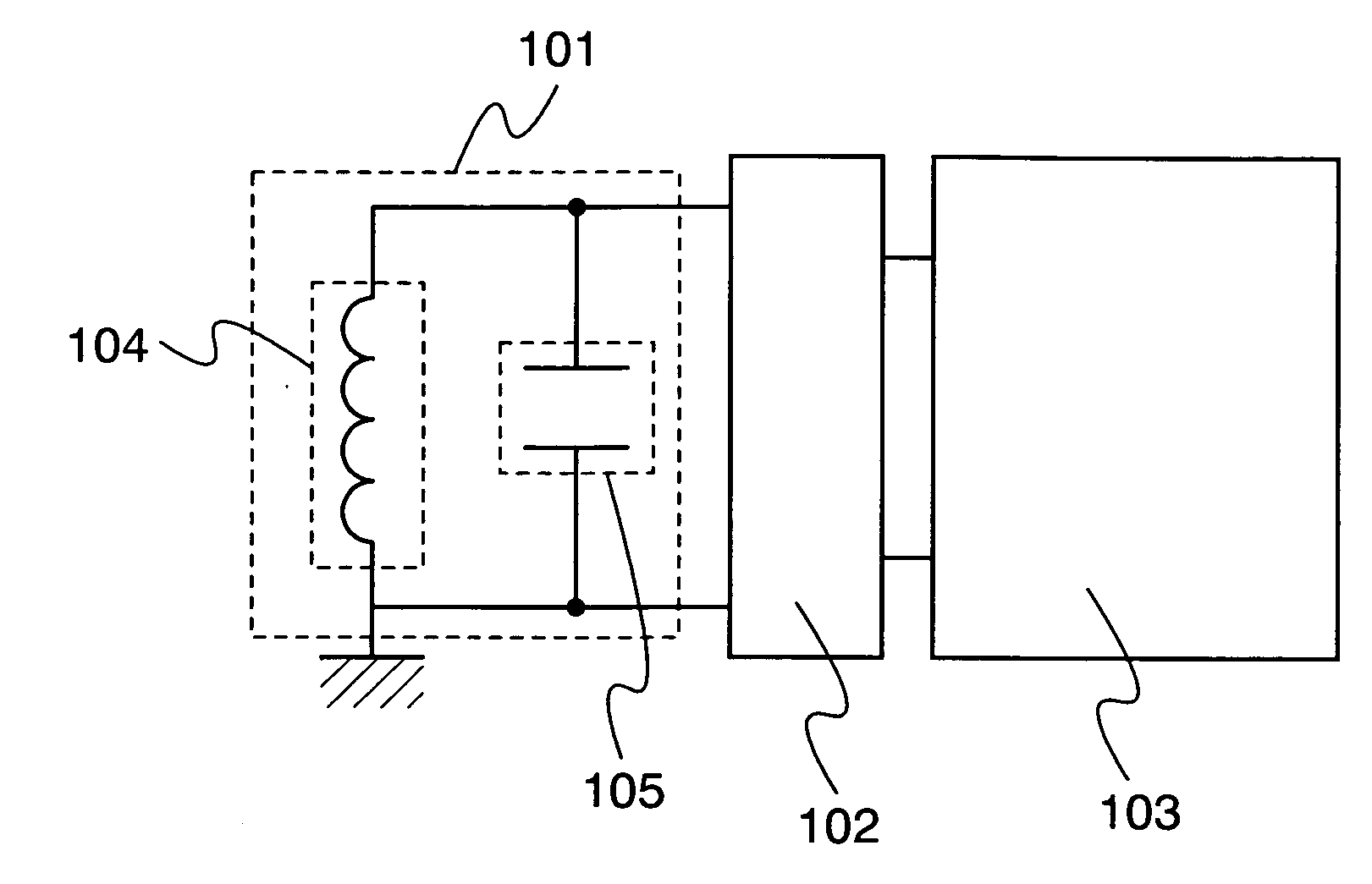

Semiconductor device

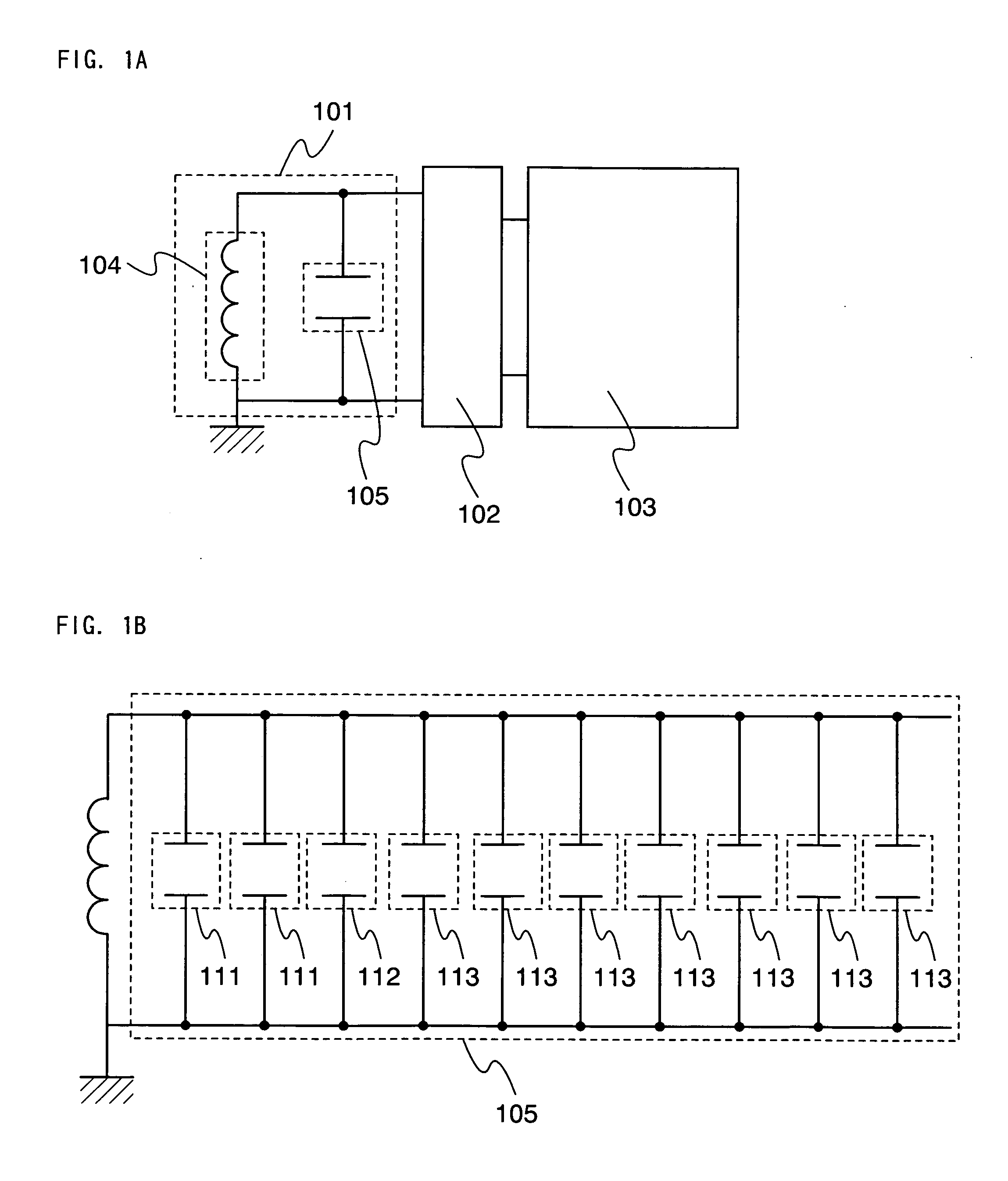

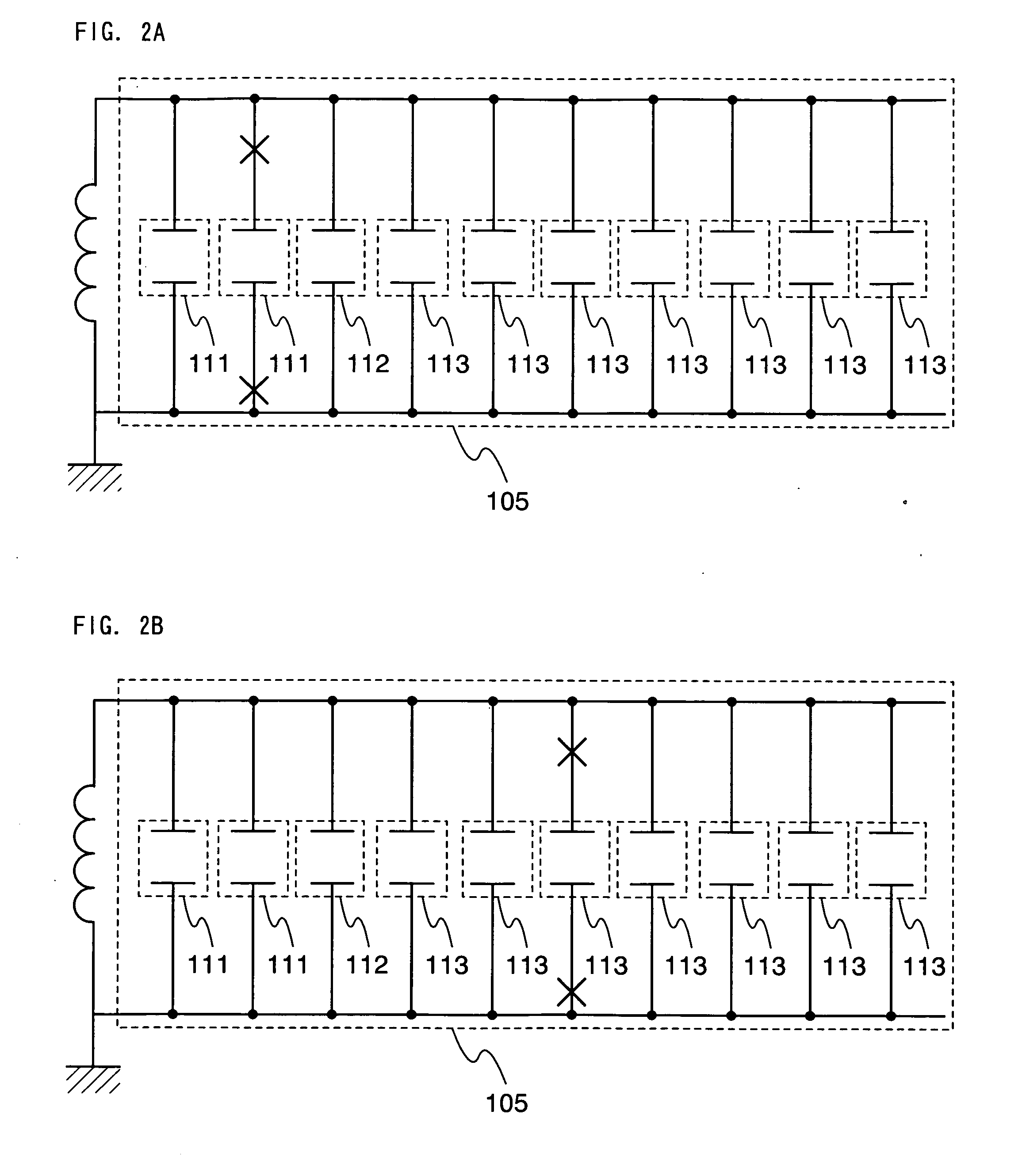

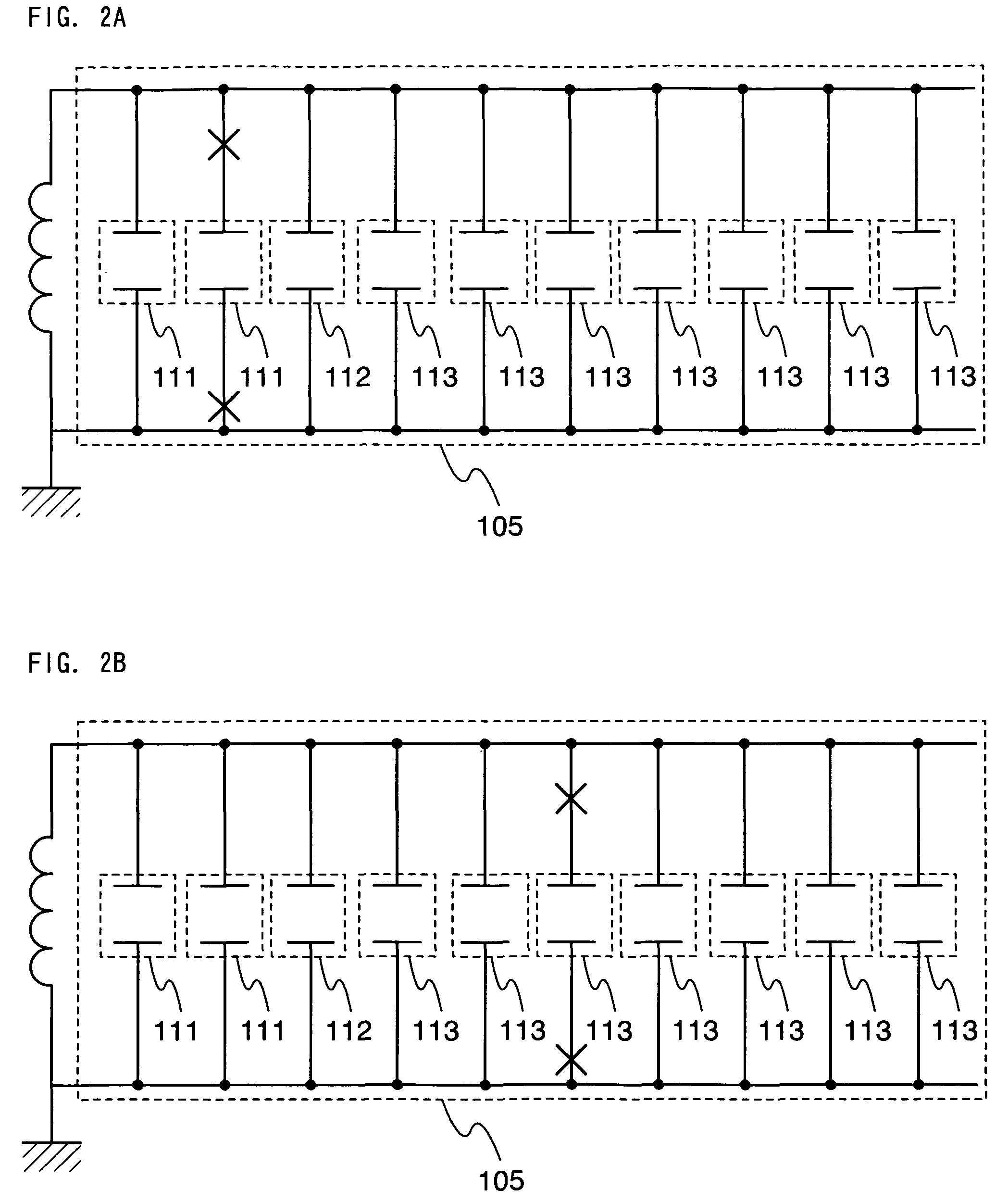

InactiveUS20060267771A1Easy to adjustReduced footprintSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDevice material

It is an object of the present invention to provide a semiconductor device in which an arrangement area of capacitance can be reduced and resonance frequency can be easily adjusted. The semiconductor device includes an antenna and a resonance circuit including a capacitor connected to the antenna in parallel where the capacitor is formed by connecting x pieces of first capacitor (x is an arbitrary natural number), y pieces of second capacitor (y is an arbitrary natural number), and z pieces of third capacitor (z is an arbitrary natural number) in parallel; and the first capacitor, the second capacitor, and the third capacitor have different capacitance values from each other. It is preferable that each of the first capacitor, the second capacitor, and the third capacitor be a MIS capacitor. Further, at least one of the first capacitor, the second capacitor, and the third capacitor is preferably formed by connecting a plurality of capacitors in parallel.

Owner:SEMICON ENERGY LAB CO LTD

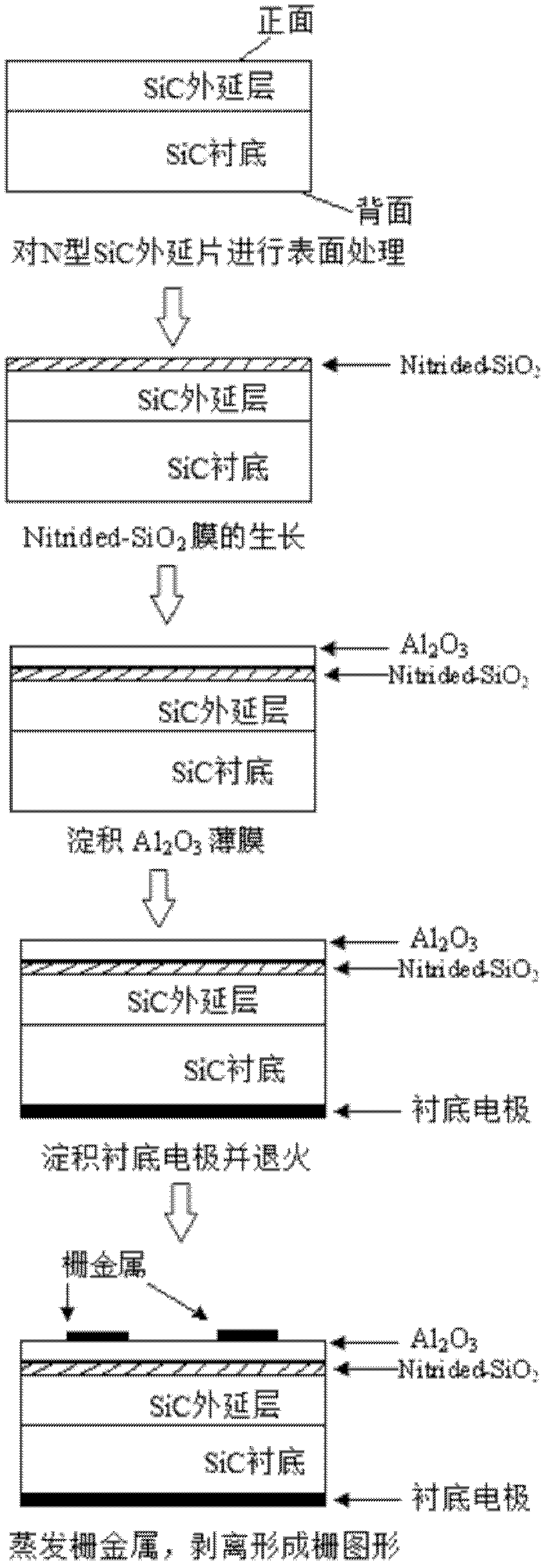

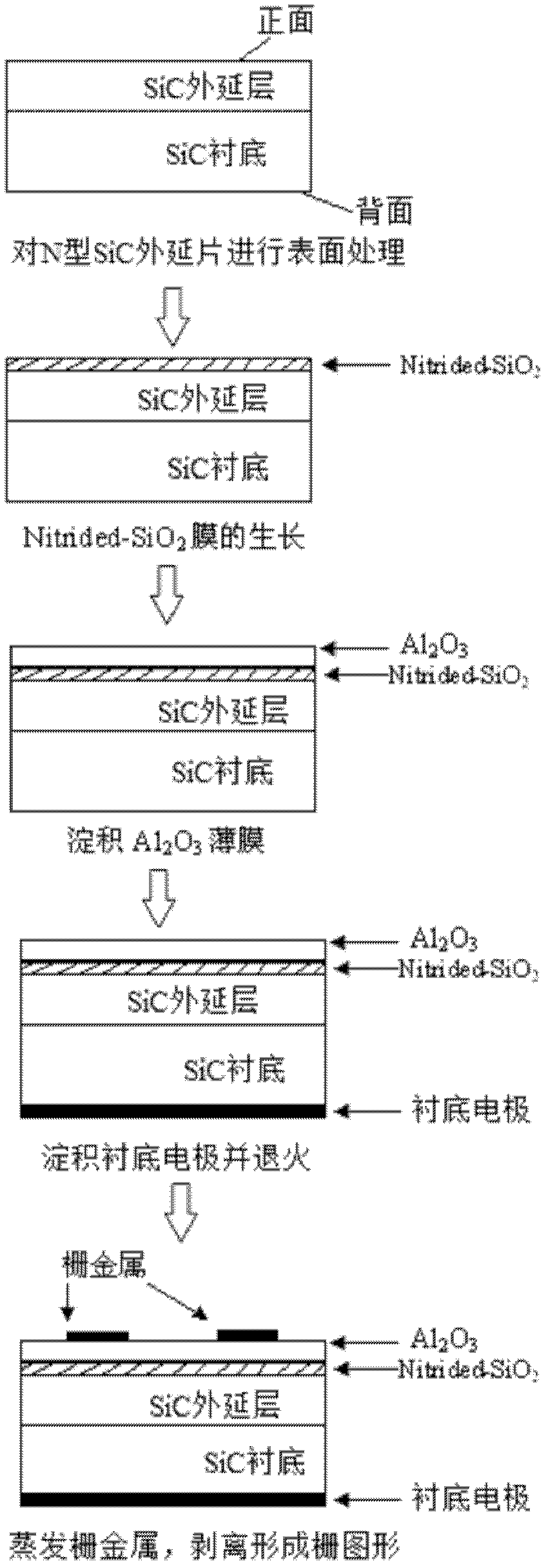

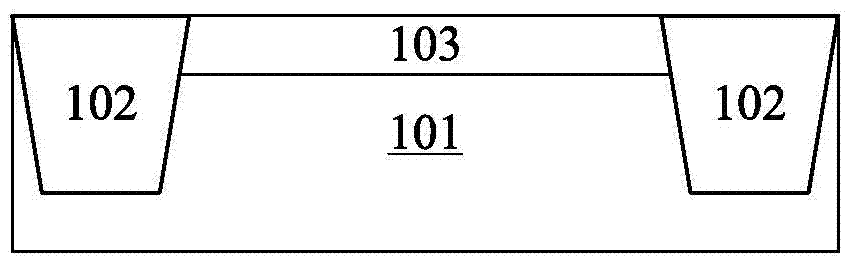

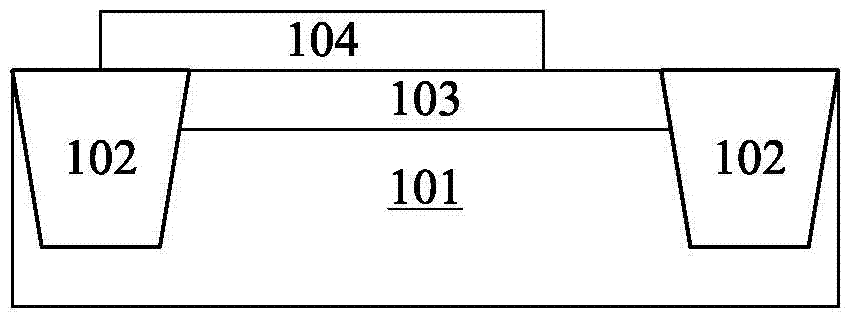

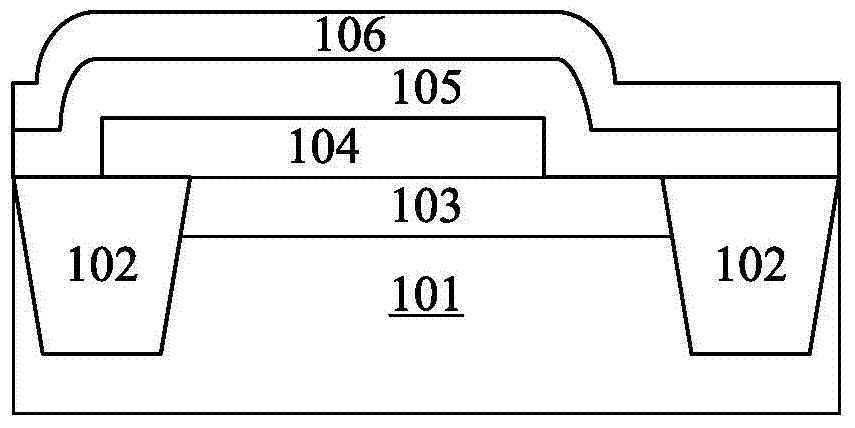

Manufacture method of stacked gate SiC-metal insulator semiconductor (MIS) capacitor

ActiveCN102629559AImprove featuresImprove reliabilitySemiconductor/solid-state device manufacturingCapacitanceEngineering

The invention discloses a manufacture method of a stacked gate SiC-metal insulator semiconductor (MIS) capacitor and mainly solves the problem of overlarge gate leakage current, too high SiC and SiO2 interface state density and poor breakdown characteristics of a SiC power MIS device. In the manufacture process, the standard wet process cleaning is carried out on an N type SiC epitaxial wafer; a layer of SiO2 film grows by a dry-oxygen oxidation method, and bottom layer gate media are formed; the grown SiO2 film is subjected to plasma treatment in an electron cyclotron resonance plasma enhanced-metal organic chemical vapor deposition (ECR PE-MOCVD) system; an atom layer deposition (ALD) method is used for depositing Al2O3 medium films, and top layer gate media are formed; substrate metals are evaporated by electron beams to form a zero electrode; and finally, the gate metal is formed through peeling, and the device manufacture is completed. The gate medium reliability of the SiC-MIS capacitor during the high-temperature and high-power application is improved, and the manufacture method can be used for the manufacture of large-scale SiC-MIS devices and circuits.

Owner:DALIAN UNIV OF TECH +1

Mis hydrogen sensors

InactiveUS20050074970A1Semiconductor/solid-state device manufacturingGas analyser construction detailsMIS capacitorHydrogen sensor

Hydrogen gas sensors employ an epitaxial layer of the thermodynamically stable form of aluminum nitride (AlN) as the “insulator” in an MIS structure having a thin metal gate electrode suitable for catalytic dissociate of hydrogen, such as palladium, on a semiconductor substrate. The AlN is deposited by a low temperature technique known as Plasma Source Molecular Beam Epitaxy (PSMBE). When silicon (Si) is used the semiconducting substrate, the electrical behavior of the device is that of a normal nonlinear MIS capacitor. When a silicon carbide (SiC) is used, the electrical behavior of the device is that of a rectifying diode. Preferred structures are Pd / AlN / Si and Pd / AlN / SiC wherein the SiC is preferably 6H—SiC.

Owner:WAYNE STATE UNIV

MIS capacitor

InactiveUS7164165B2Reduce leakageIncrease capacitanceTransistorSolid-state devicesCapacitanceOxide composite

An MIS capacitor with low leakage and high capacitance is disclosed. A layer of hemispherical grained polysilicon (HSG) is formed as a lower electrode. Prior to the dielectric formation, the hemispherical grained polysilicon layer may be optionally subjected to a nitridization or anneal process. A dielectric layer of aluminum oxide (Al2O3), or a composite stack of interleaved layers of aluminum oxide and other metal oxide dielectric materials, is fabricated over the hemispherical grained polysilicon layer and after the optional nitridization or anneal process. The dielectric layer of aluminum oxide (Al2O3) or the aluminum oxide composite stack may be optionally subjected to a post-deposition treatment to further increase the capacitance and decrease the leakage current. A metal nitride upper electrode is formed over the dielectric layer or the composite stack by a deposition technique or by atomic layer deposition.

Owner:ROUND ROCK RES LLC

High performance MIS capacitor with HfO2 dielectric

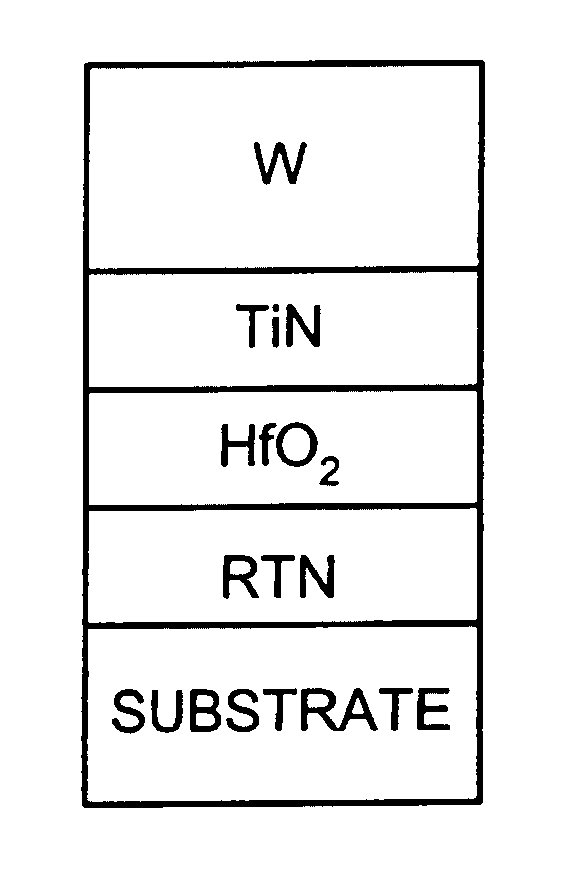

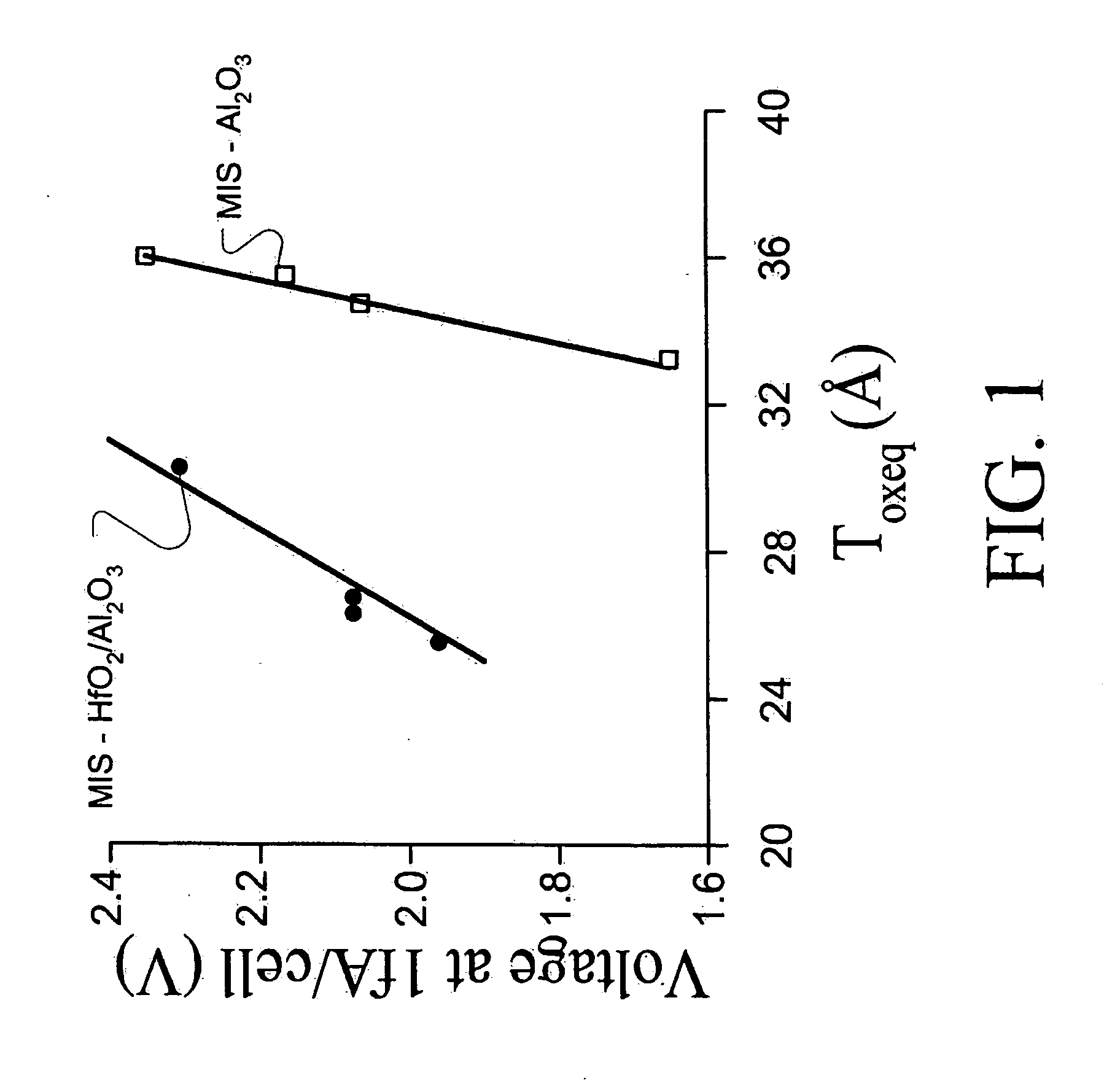

InactiveUS7094712B2Prevent crystallizationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricInter layer

Disclosed is a method for forming metal oxide dielectric layers, more particularly HfO2 dielectric layers, using an atomic layer deposition (ALD) method in which a series of thin intermediate layers are formed and treated with one or more oxidizers and nitrogents before the next intermediate layer is formed on the substrate. The intermediate oxidation treatments reduce the number of organic contaminants incorporated into the metal oxide layer from the organometallic precursors to produce a dielectric layer having improved current leakage characteristics. The dielectric layers formed in this manner remain susceptible to crystallization if exposed to temperatures much above 550° C., so subsequent semiconductor manufacturing processes should be modified or eliminated to avoid such temperatures or limit the duration at such temperatures to maintain the performance of the dielectric materials.

Owner:SAMSUNG ELECTRONICS CO LTD

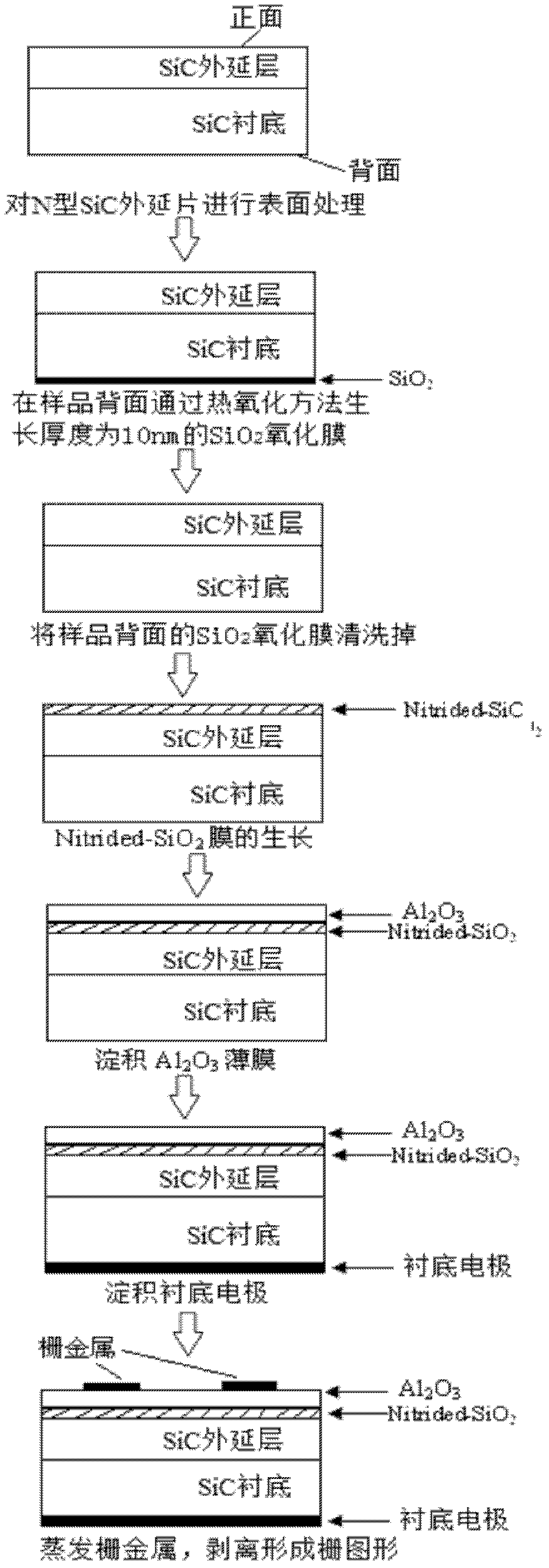

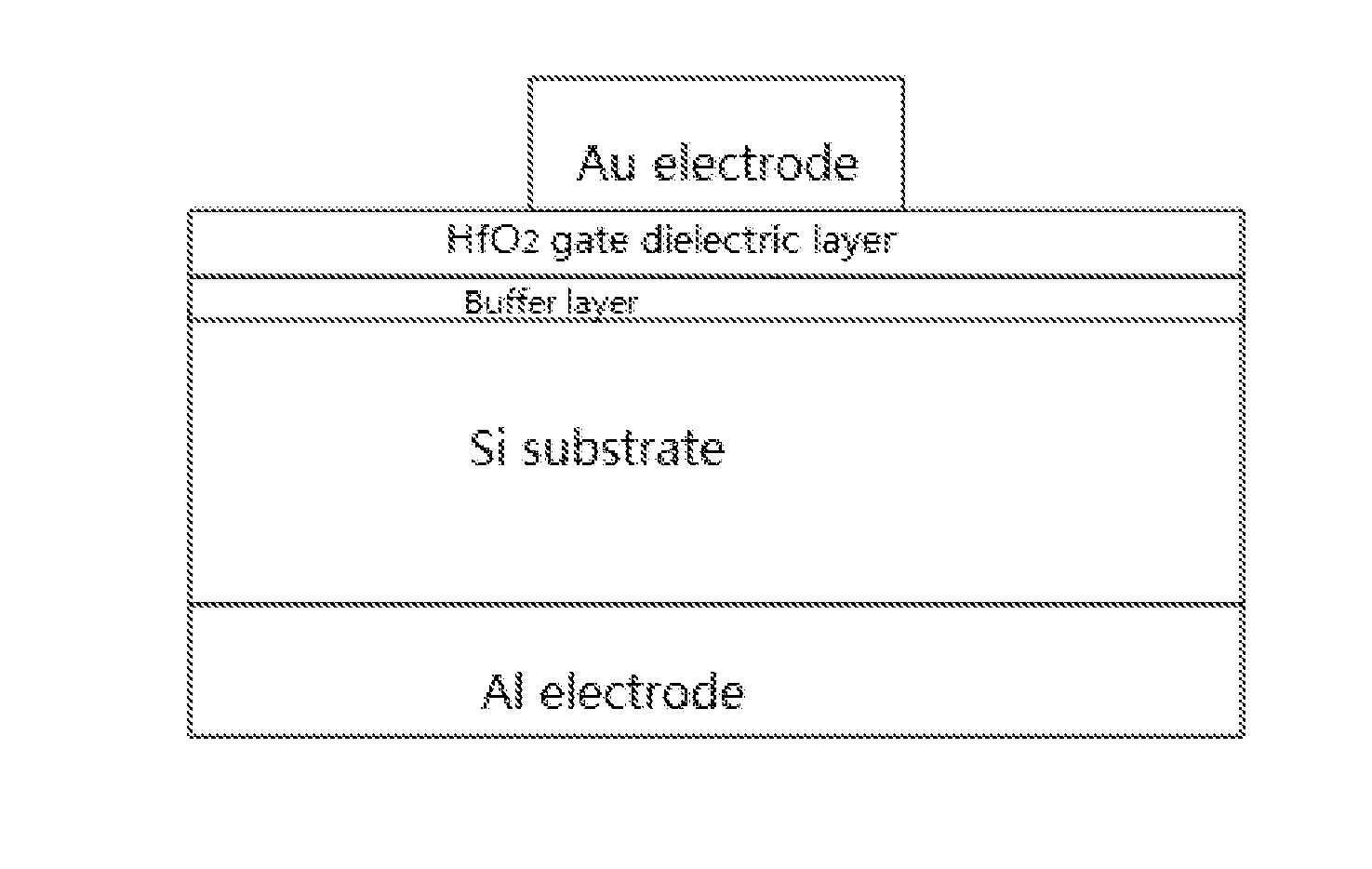

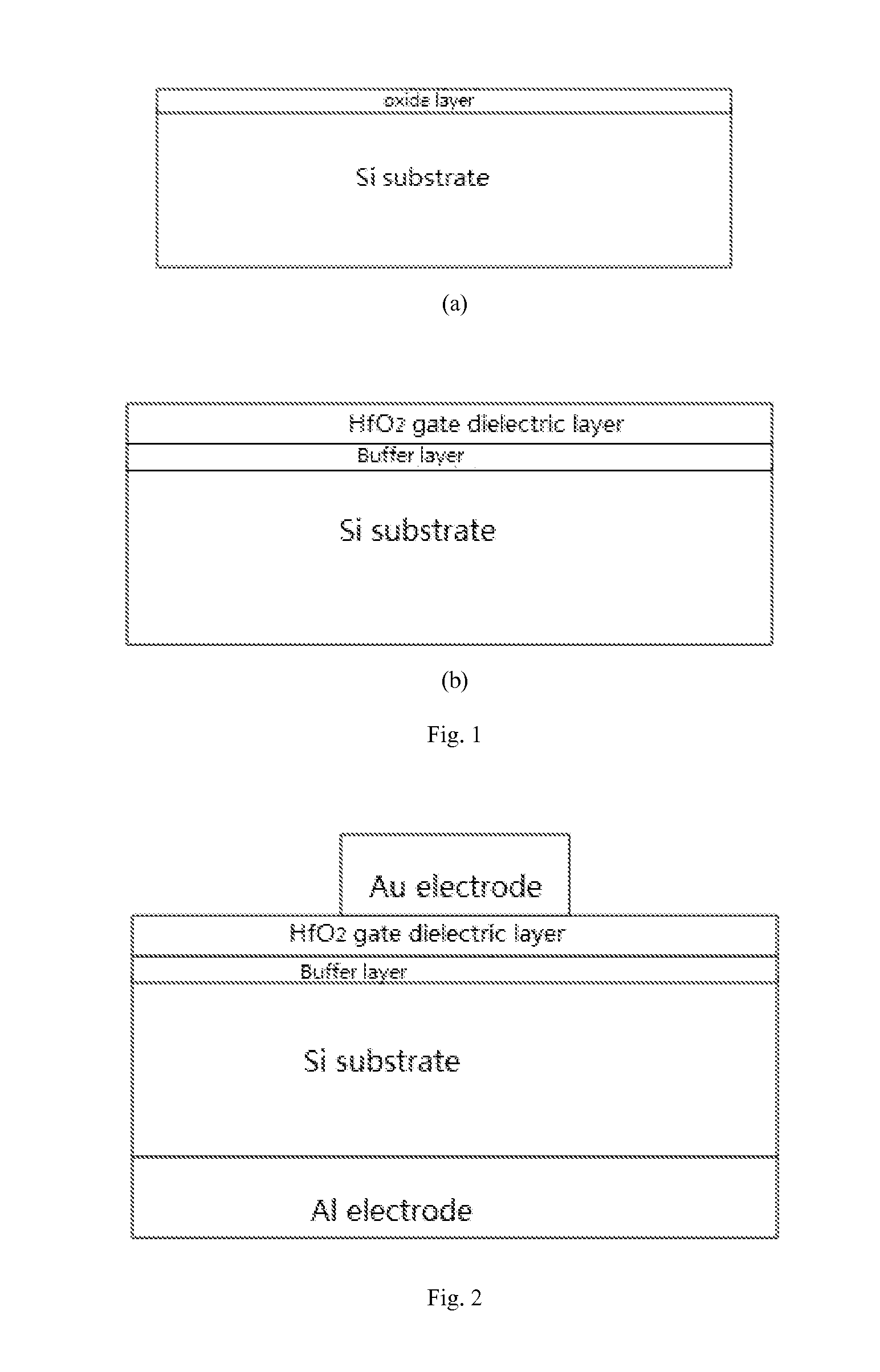

Method of depositing gate dielectric, method of preparing mis capacitor, and mis capacitor

InactiveUS20120273861A1Reduce thicknessImprove electrical performanceTransistorSolid-state devicesEquivalent oxide thicknessGate dielectric

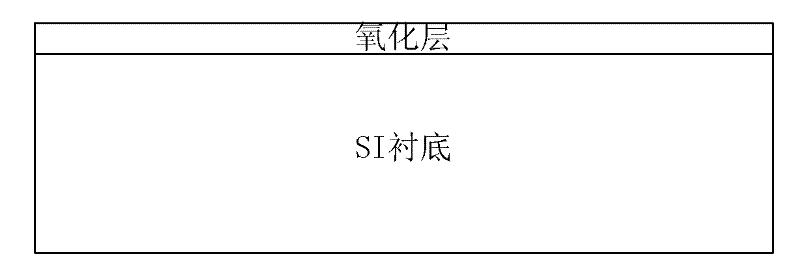

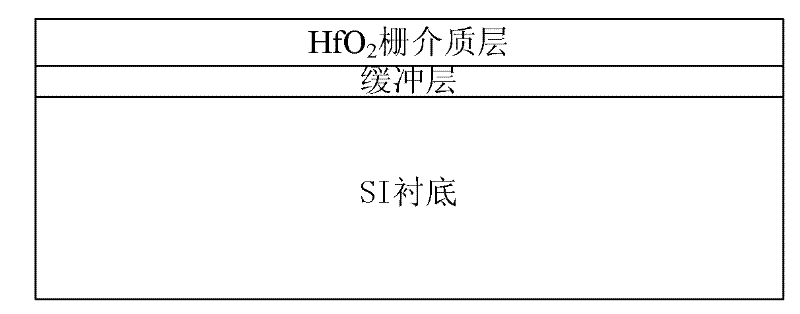

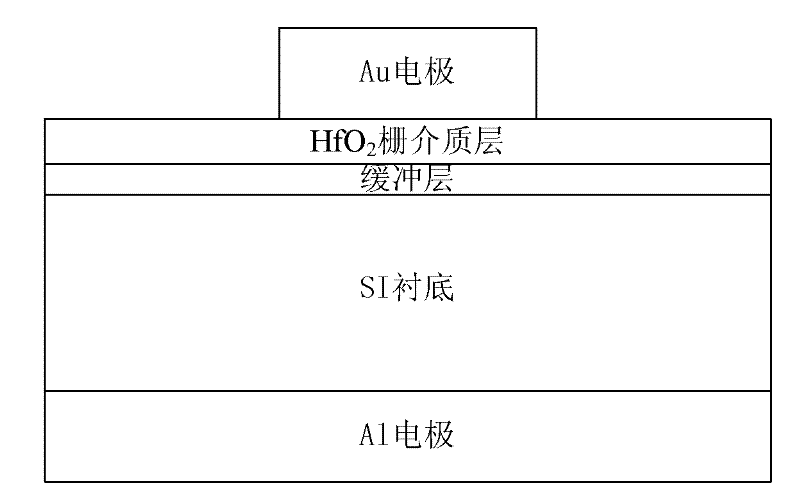

The present invention relates to a method of depositing a gate dielectric, a method of preparing a MIS capacitor and the MIS capacitor. In the method of depositing the gate dielectric, a semiconductor substrate surface is preprocessed with oxygen plasma and nitrogen-containing plasma to form a nitrogen-containing oxide layer thereon. Then, a high-k gate dielectric layer is grown on the nitrogen-containing oxide layer surface by a plasma-enhanced atomic layer deposition process, and the oxide layer converts during the gate dielectric layer growth process into a buffer layer of a dielectric constant higher than SiO2. Then, a metal electrode is formed on both an upper layer and a lower layer of the thus-formed semiconductor construction, so that a MIS capacitor is prepared. According to the present invention, the formation of the buffer layer enables the interface characteristics between semiconductor materials and high-k gate dielectric layers to be improved effectively, equivalent oxide thickness (EOT) to be reduced and electrical properties to be enhanced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method for depositing gate dielectric, method for preparing MIS capacitor and MIS capacitor

InactiveCN102226270AReduce the equivalent gate oxide thicknessImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricCapacitance

The invention provides a method for depositing a gate dielectric, a method for preparing a MIS capacitor and a MIS capacitor. The method for depositing the gate dielectric comprises the following steps: first, pretreating the surface of a semiconductor substrate by using O2 plasma and plasma containing nitrogen so as to form a nitrogenous oxide layer on the surface of the semiconductor substrate; and then, growing a gate dielectric layer with high dielectric constant on the surface of the nitrogenous oxide layer using a plasma enhanced atomic layer deposition process, wherein, the oxide layer converts into a buffer layer with higher dielectric constant than SiO2 in the process of growth of the gate dielectric layer. Based on the method for depositing the gate dielectric, a MIS capacitor is prepared by forming a metal electrode on the upper and lower surface of the formed semiconductor structure. The invention has the advantages that: the existence of the buffer layer is capable of improving the interface characteristic between the semiconductor material and the high K gate dielectric layer, reducing the increasement of equivalent oxide thickness (EOT) and improving the electric properties.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

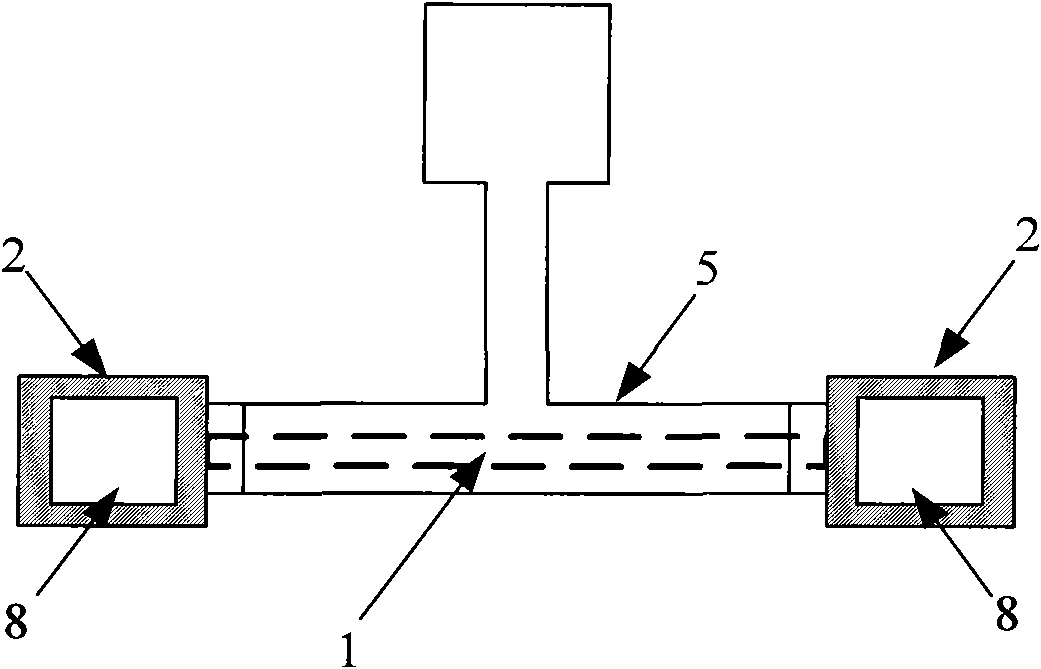

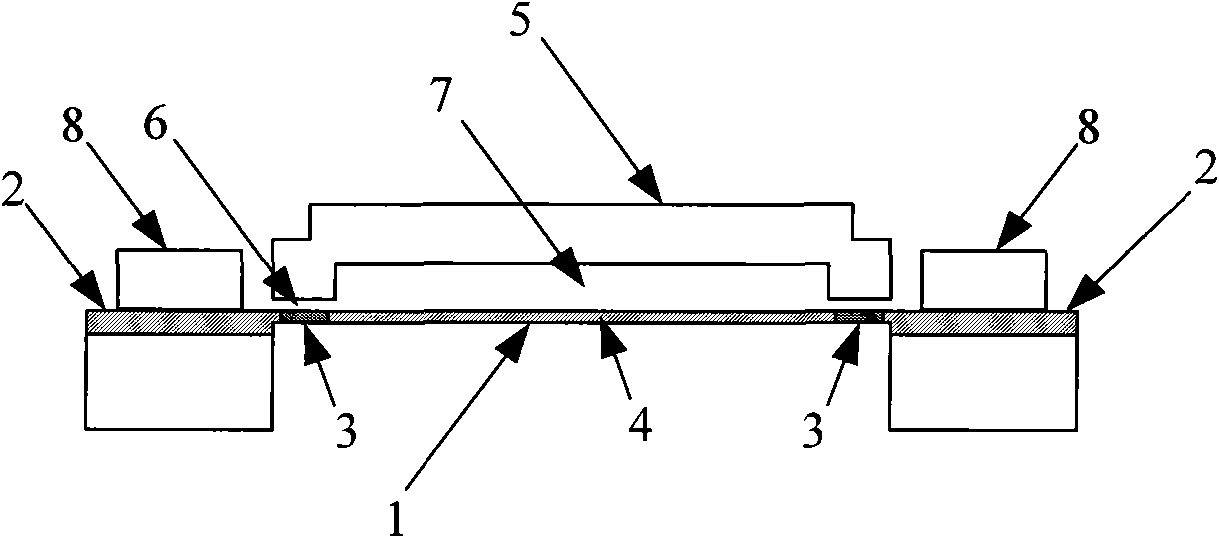

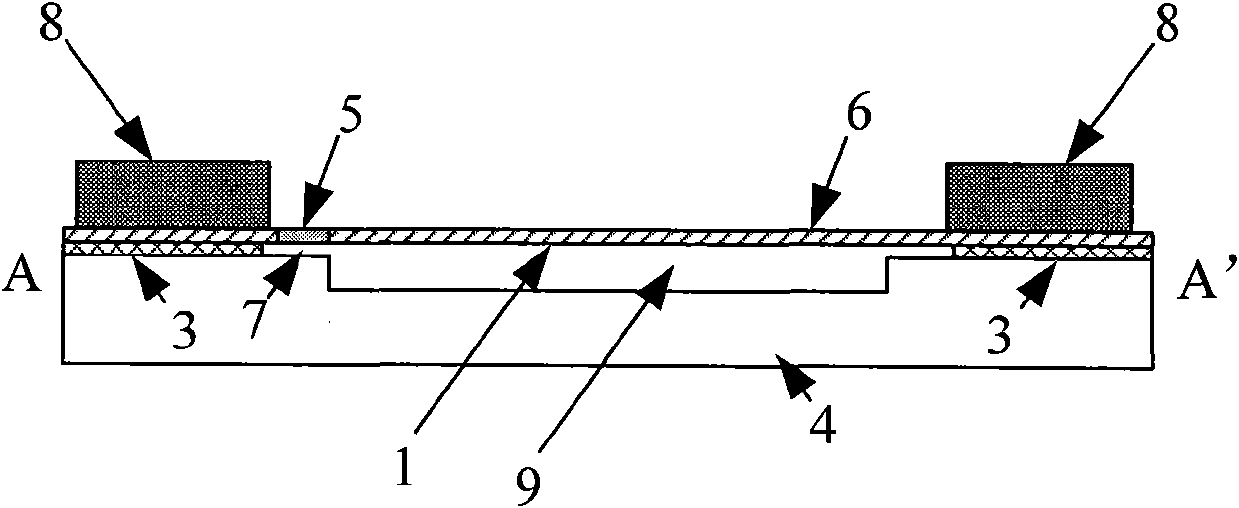

Structure and method of using step electrodes to realize nanometer beam drive and pressure resistance detection

InactiveCN101565162AAvoid stressReduce qualityIndividual molecule manipulationForce measurement using piezo-resistive materialsCapacitanceElectrical resistance and conductance

The invention relates to a structure and a method of using step electrodes to realize nanometer beam drive and pressure resistance detection, which are characterized in that a metal electrode on the upper part of the nanometer beam is of step-shape; the clearance between the two ends of the electrode and the nanometer beam is smaller than 100 nanometers; while the electrode clearance in the middlepart is between 1 and 2 microns. An MIS capacitor structure is formed between the two ends of the step electrode and the nanometer beam. When the voltage between the step electrode and the nanometerbeam exceeds the threshold voltage of the MIS capacitor, a space charge area below the MIS capacitor achieves the maximum value; and the resistance under the space charge area is only a stress function, which can be used for detecting the pressure resistance of the nanometer beam. The central part of the step electrode has small effect on the resistance value of the nanometer beam due to the largeclearance; the drive efficiency of the central part to the nanometer beam is high; and the central part is used for realizing static drive on the nanometer beam.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

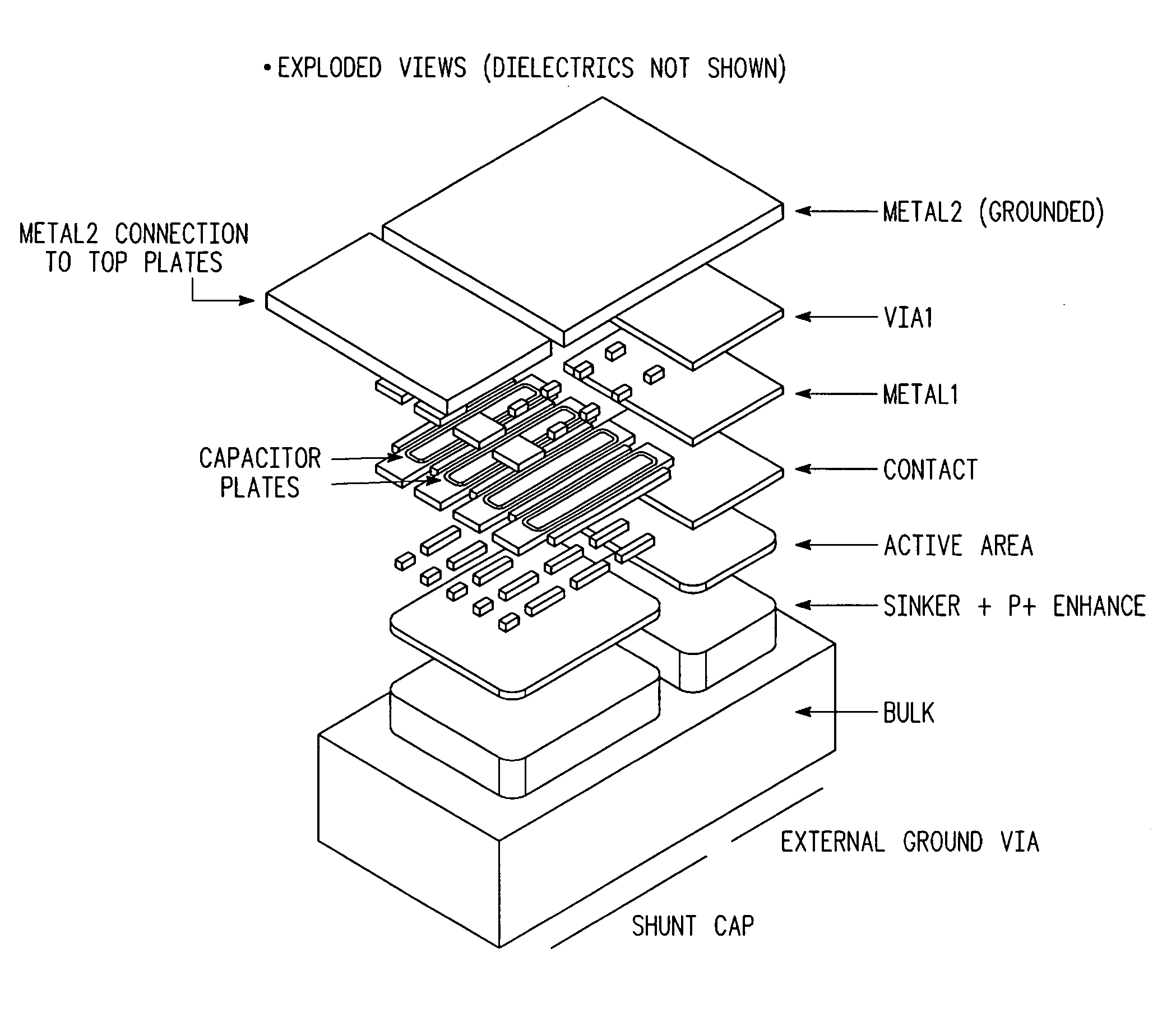

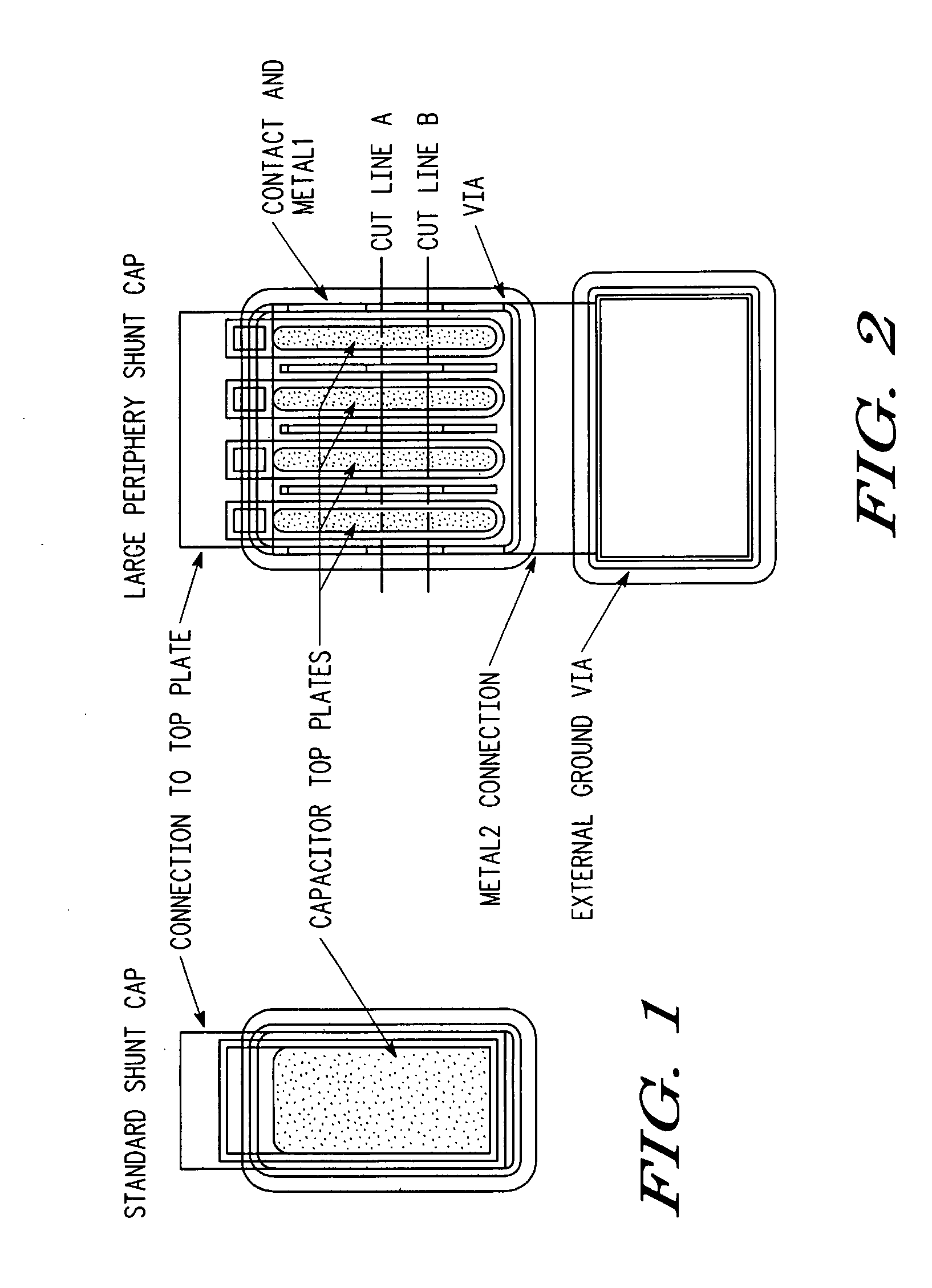

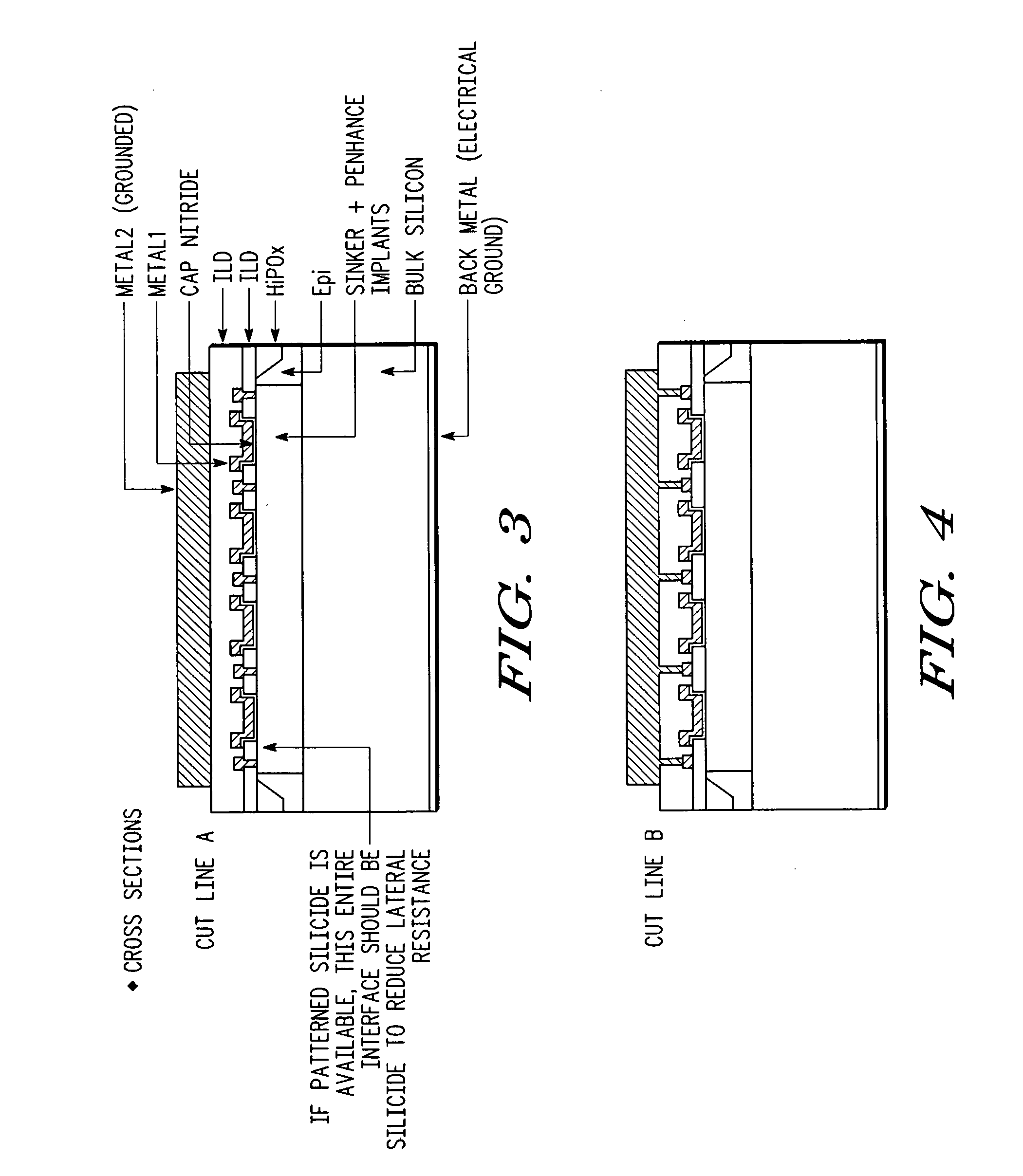

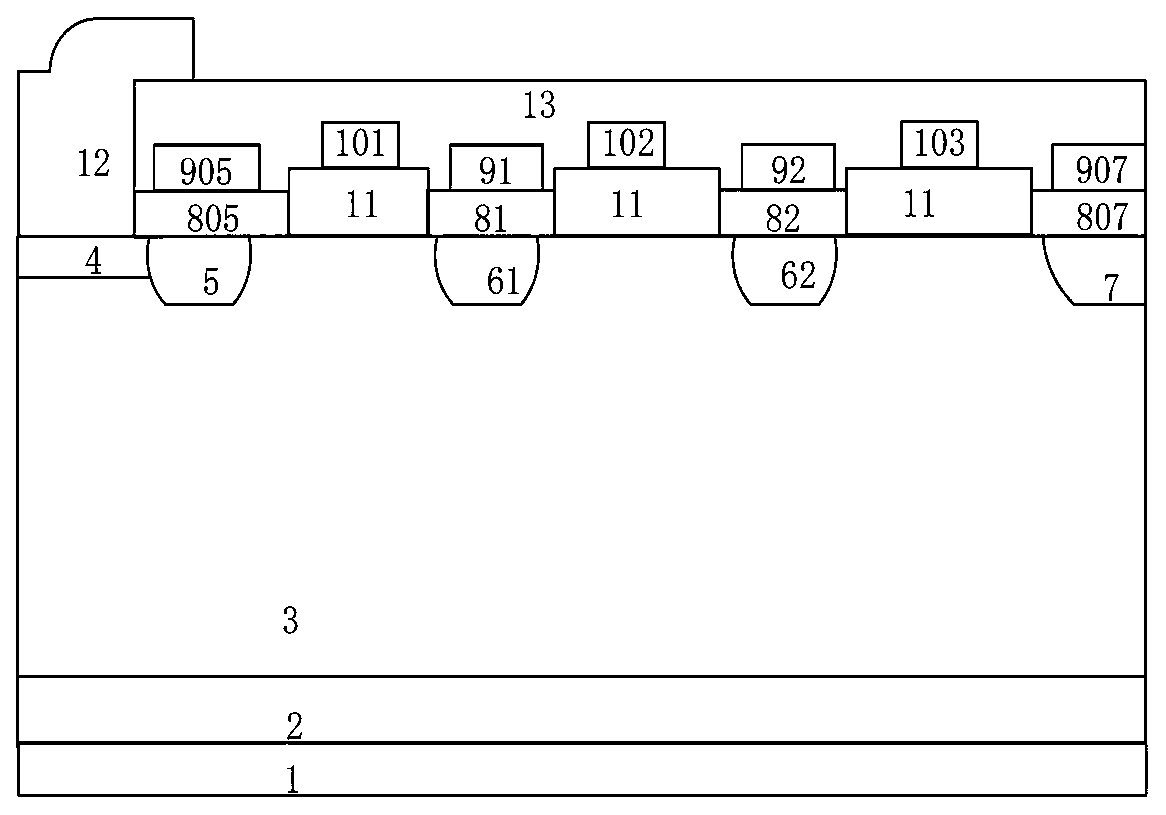

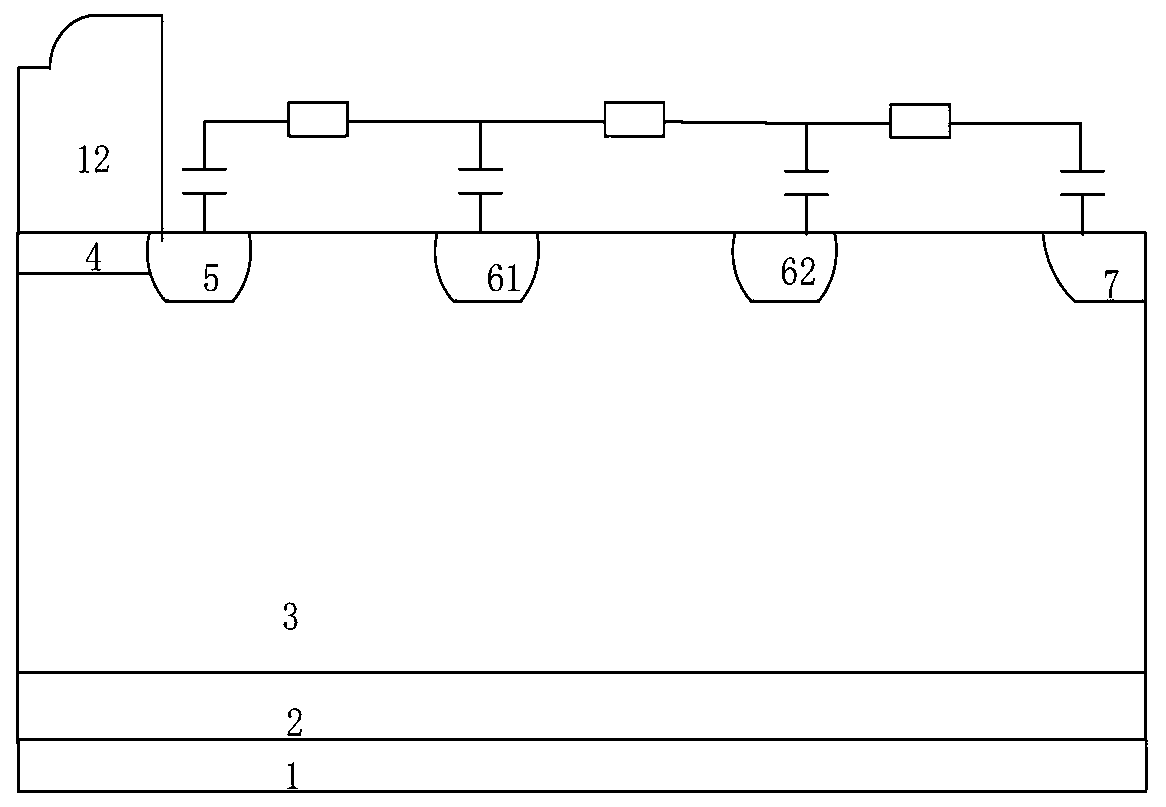

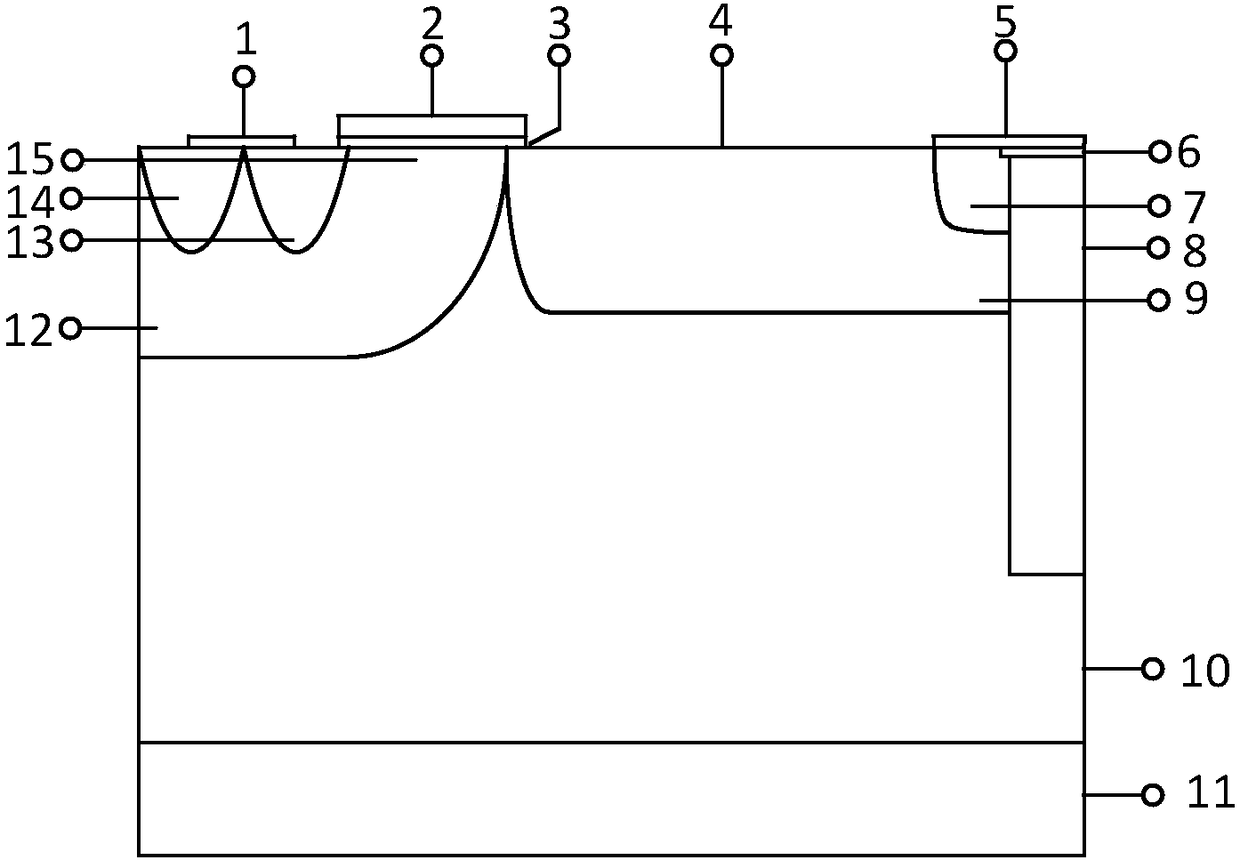

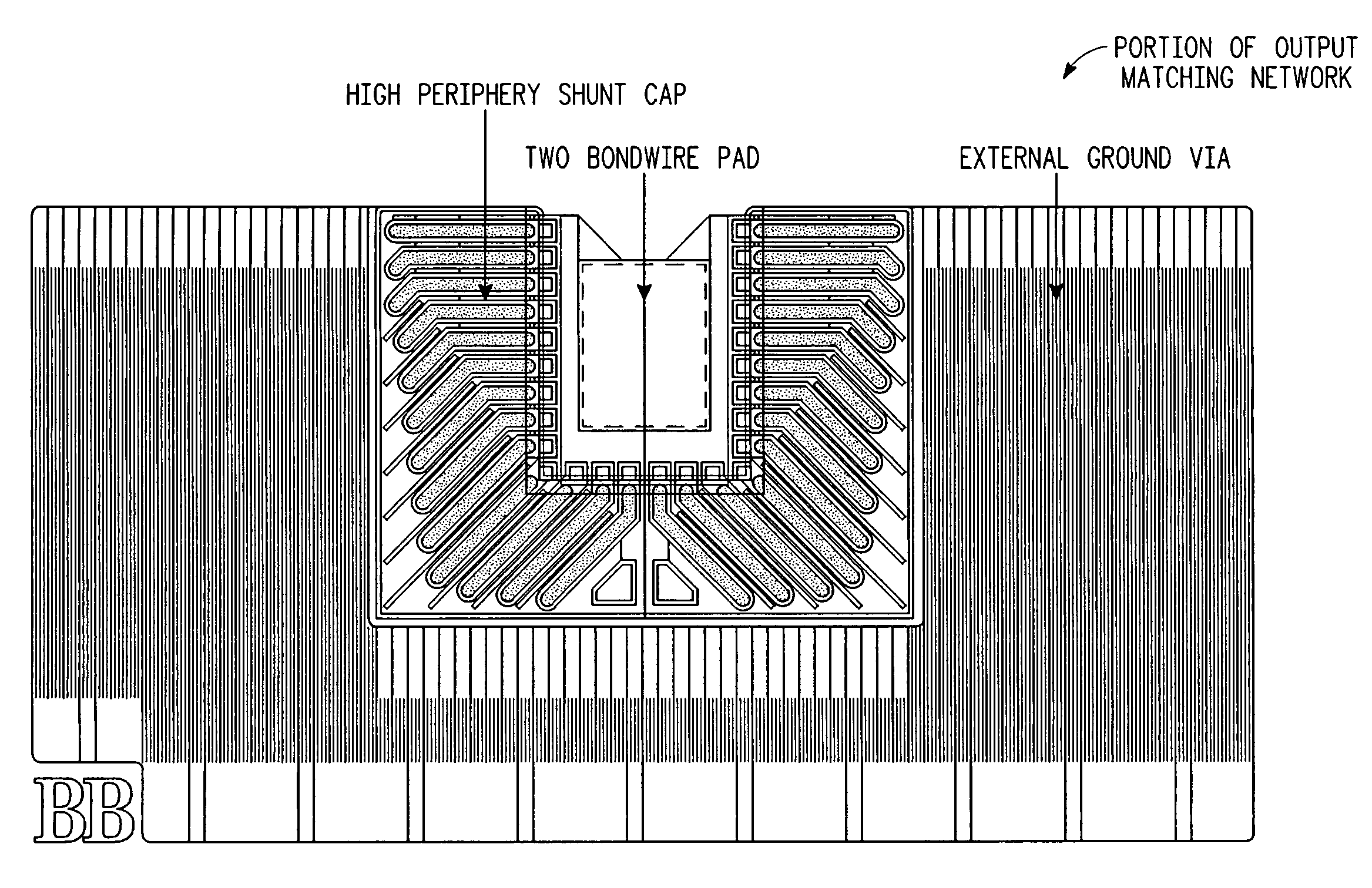

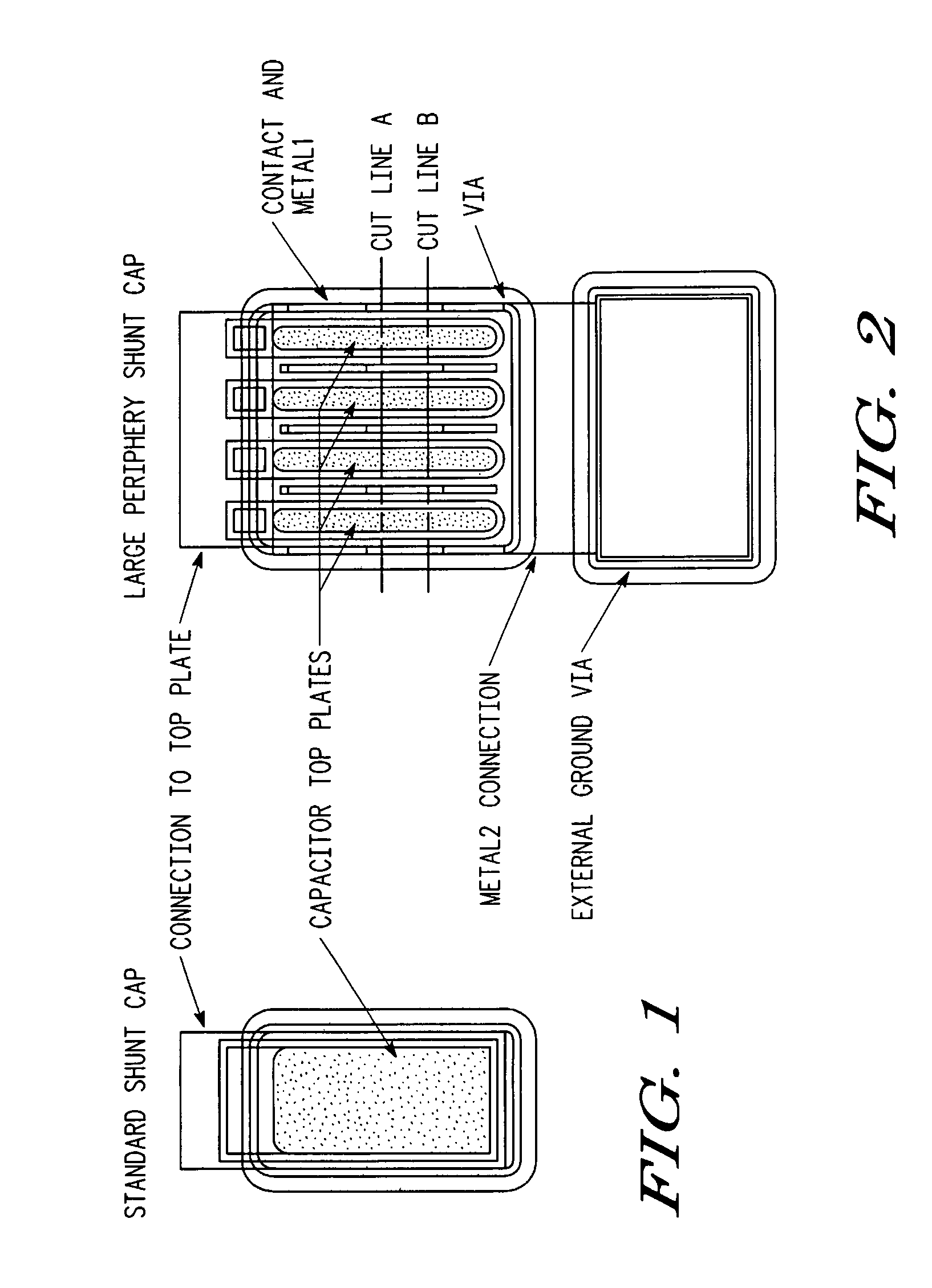

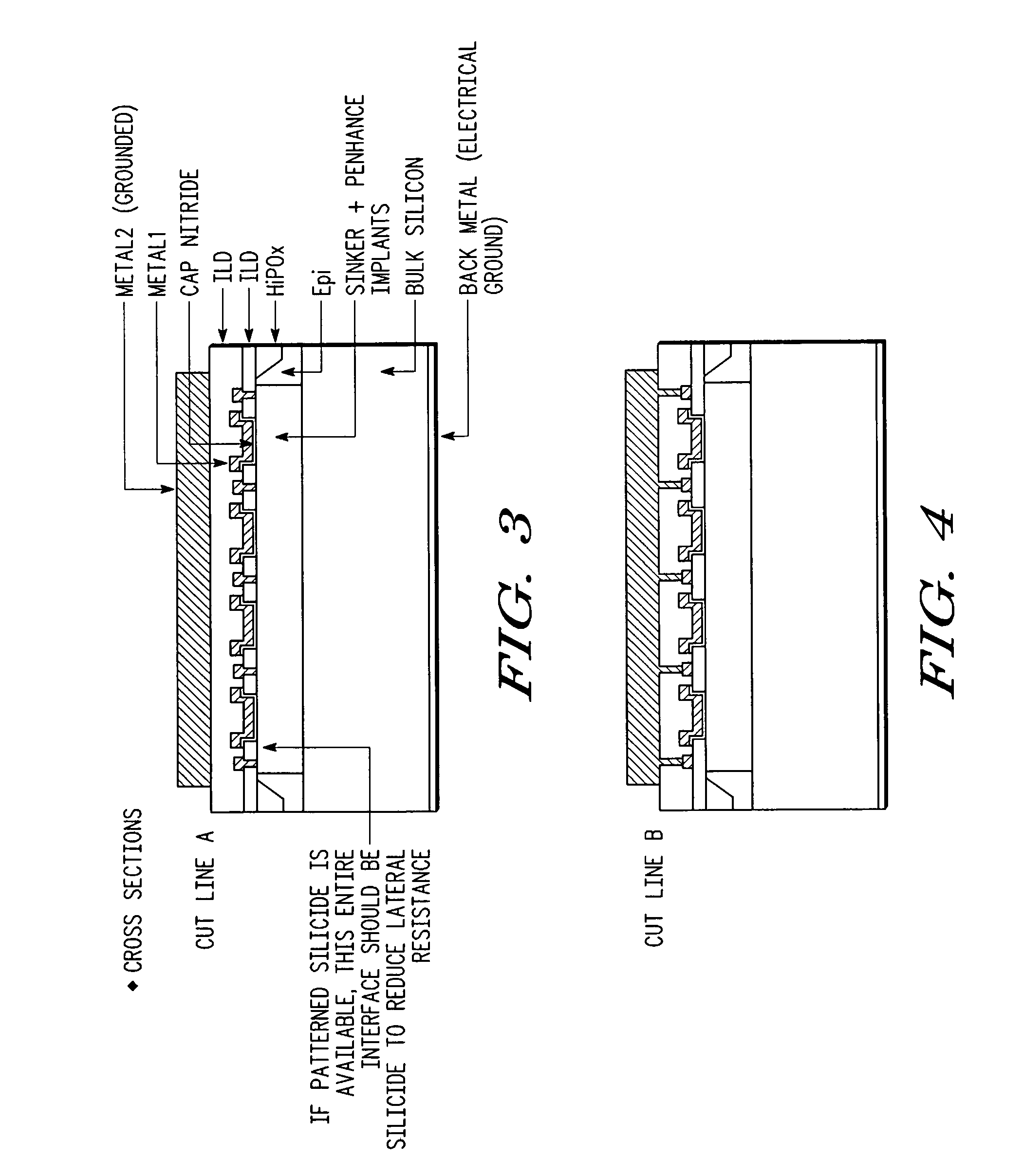

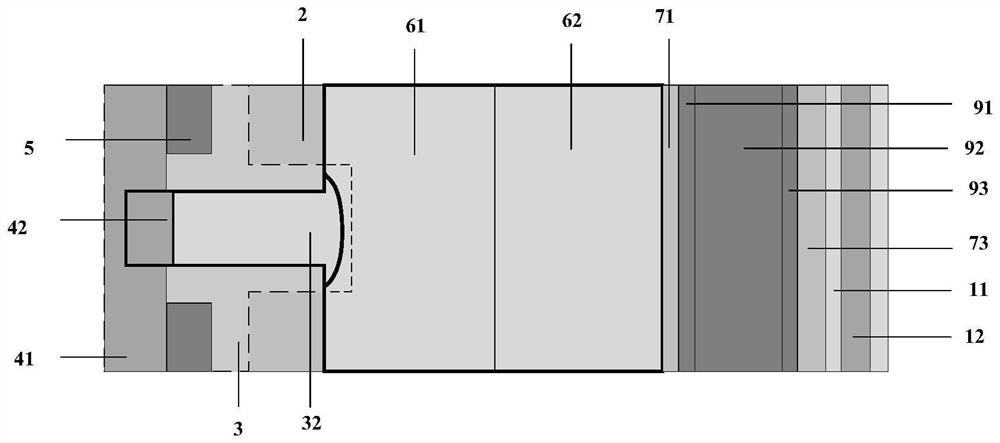

RF power transistor with large periphery metal-insulator-silicon shunt capacitor

ActiveUS20080149981A1TransistorSemiconductor/solid-state device detailsElectrical resistance and conductanceShunt capacitors

An integrated MIS capacitor structure comprises a high quality factor shunt capacitor. The integrated MIS capacitor is configured with a large periphery and an external ground via to mitigate resistive losses in the bottom plate of the MIS shunt capacitor.

Owner:NXP USA INC

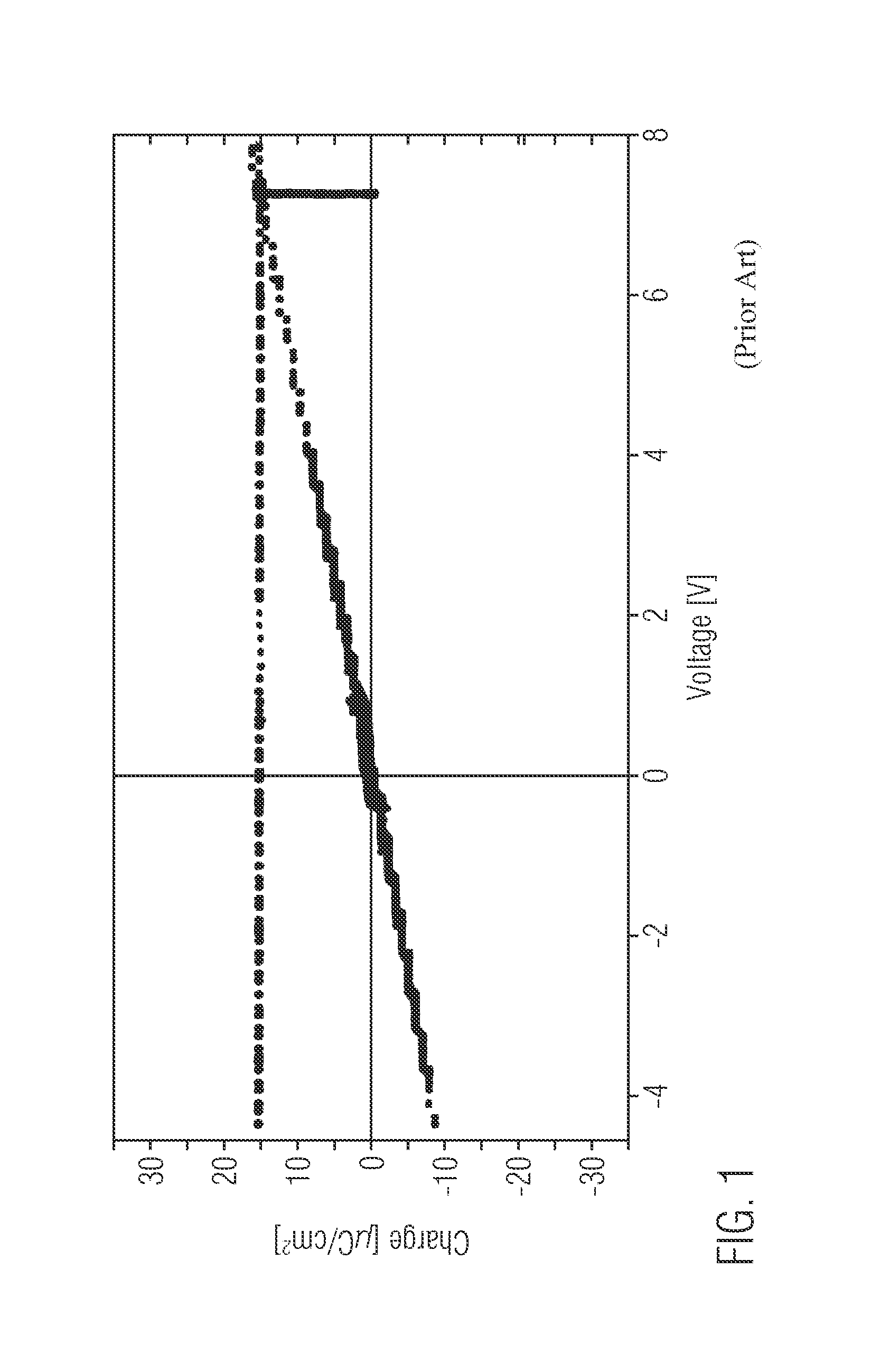

Complex circuit element and capacitor utilizing CMOS compatible antiferroelectric high-k materials

ActiveUS9318315B2Semiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMOSFET

The present disclosure provides integrated circuit elements and MIM / MIS capacitors having high capacitance and methods of forming according integrated circuit elements and integrated MIM / MIS capacitors and methods of controlling an integrated circuit element and an integrated MIM / MIS capacitor. In various aspects, a substrate is provided and a dielectric layer or insulating layer is formed over the substrate. Furthermore, an electrode layer is disposed over the dielectric layer or insulating layer. Herein, the dielectric layer or insulating layer is in an antiferroelectric phase. In various illustrative embodiments, the integrated circuit element may implement a MOSFET structure or a capacitor structure.

Owner:GLOBALFOUNDRIES US INC

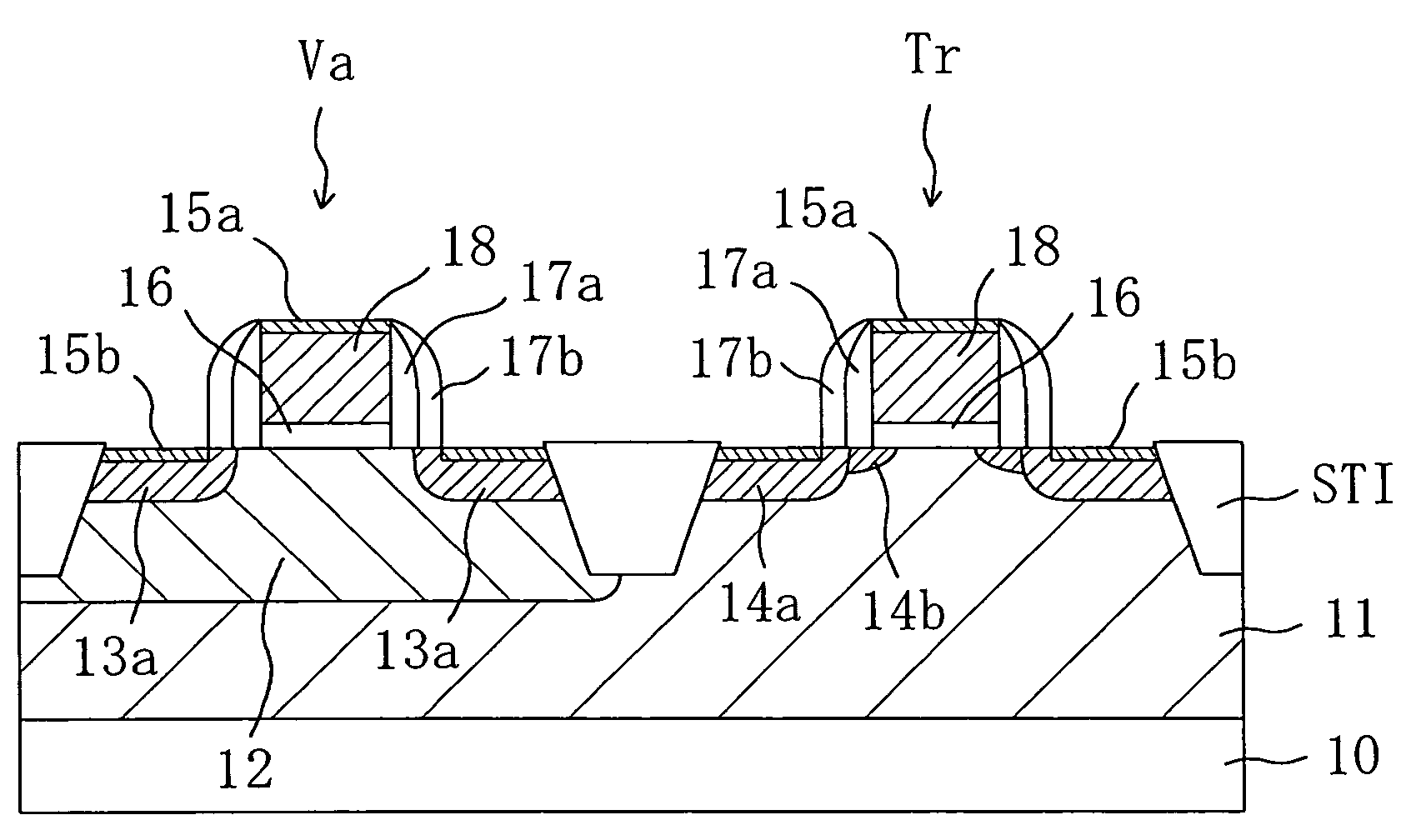

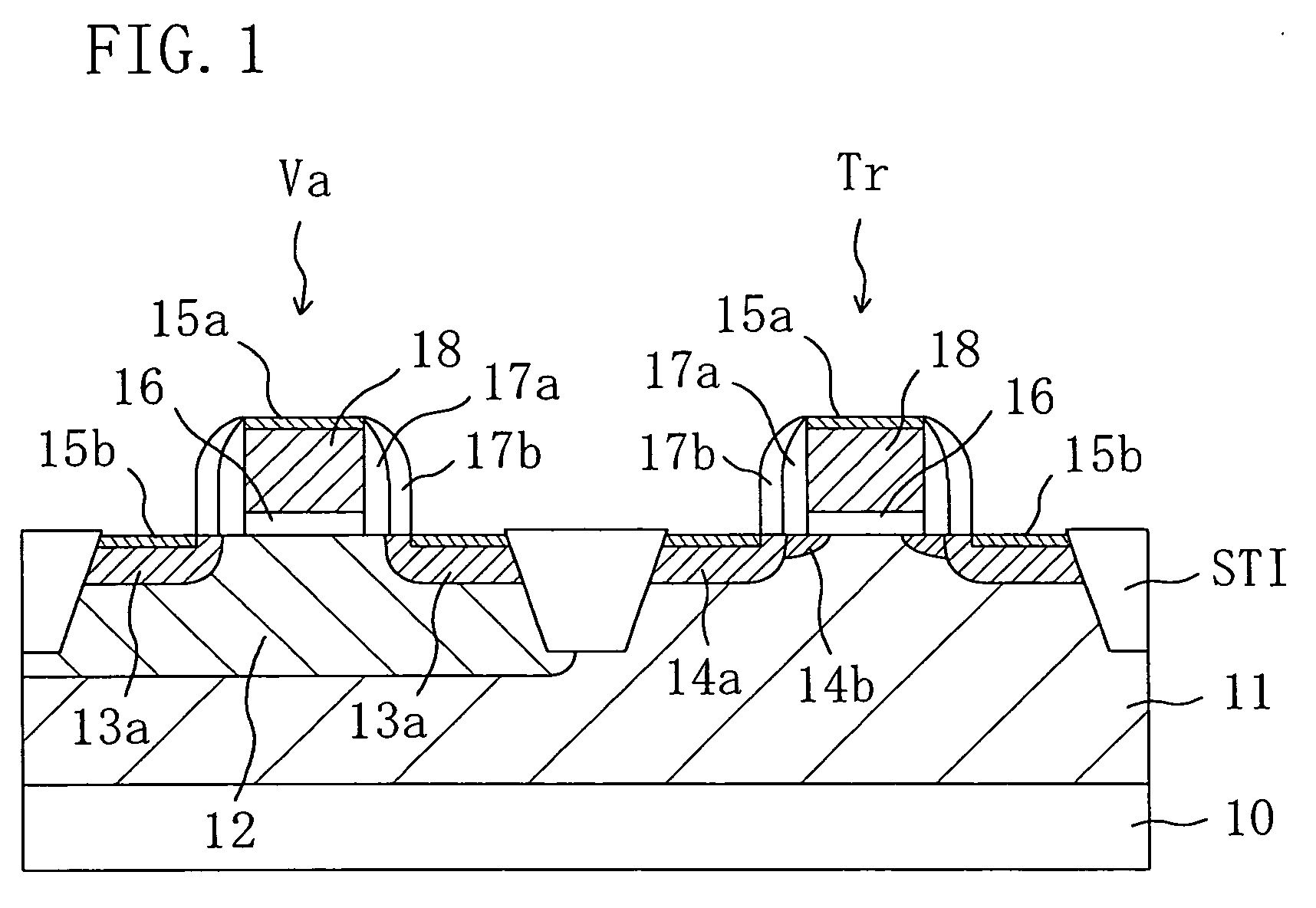

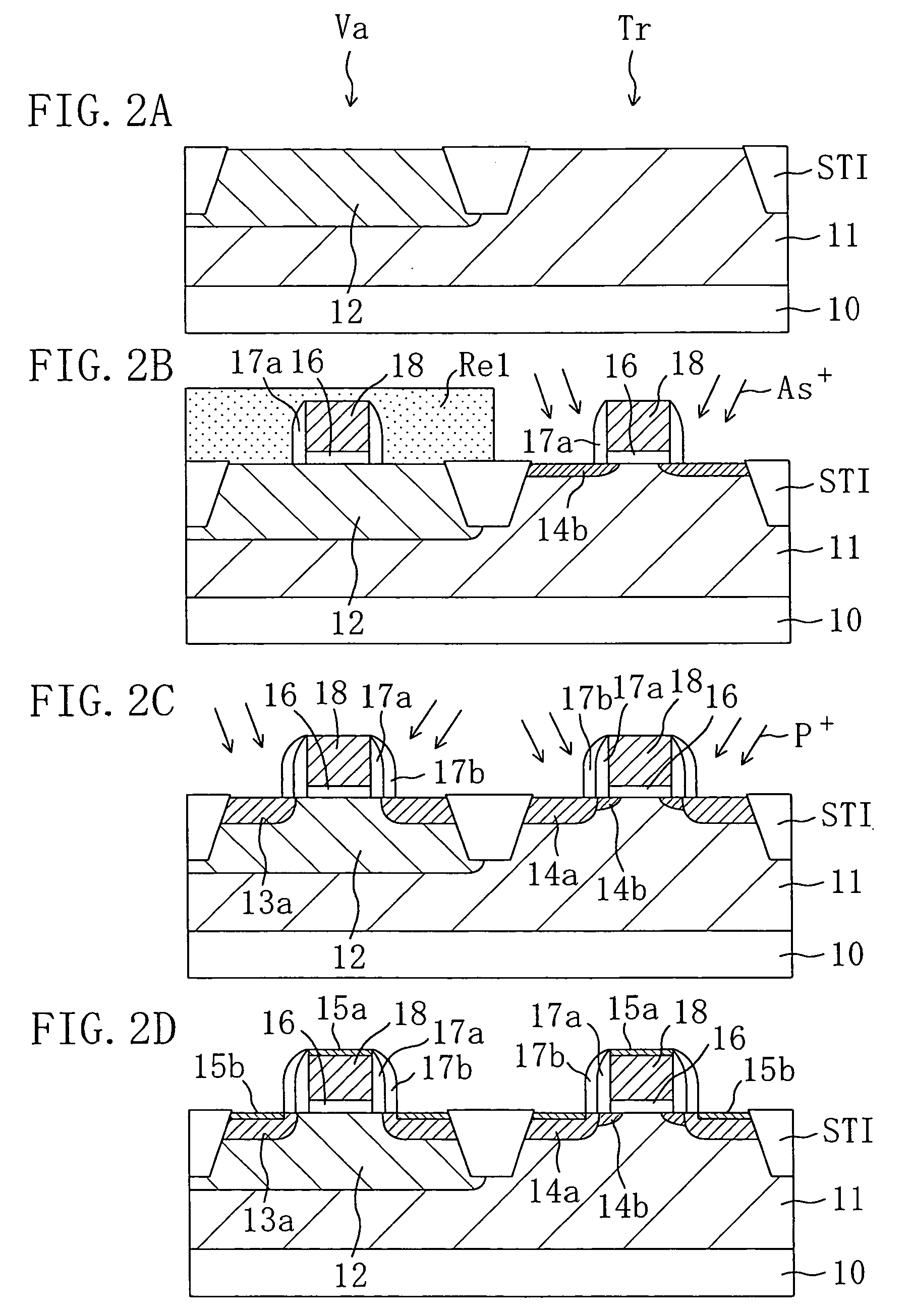

Semiconductor device including a MISFET and a MIS capacitor

ActiveUS7259418B2Range of depletionVariable capacitance range can be kept wide enoughTransistorSolid-state devicesHigh concentrationImpurity diffusion

A semiconductor device comprises varactor regions Va and transistor regions Tr. An active region for a varactor is formed with a substrate contact impurity diffusion region obtained by doping an N well region with N-type impurity at a relatively high concentration. However, any extension region (or LDD region) as in a varactor of a known semiconductor device is not formed in the active region for a varactor. On the other hand, parts of a P well region located to both sides of the polysilicon gate electrode in the transistor region Tr are formed with high-concentration source / drain regions and extension regions. Therefore, the extendable range of a depletion layer is kept wide to extend the capacitance variable range of the varactor.

Owner:GK BRIDGE 1

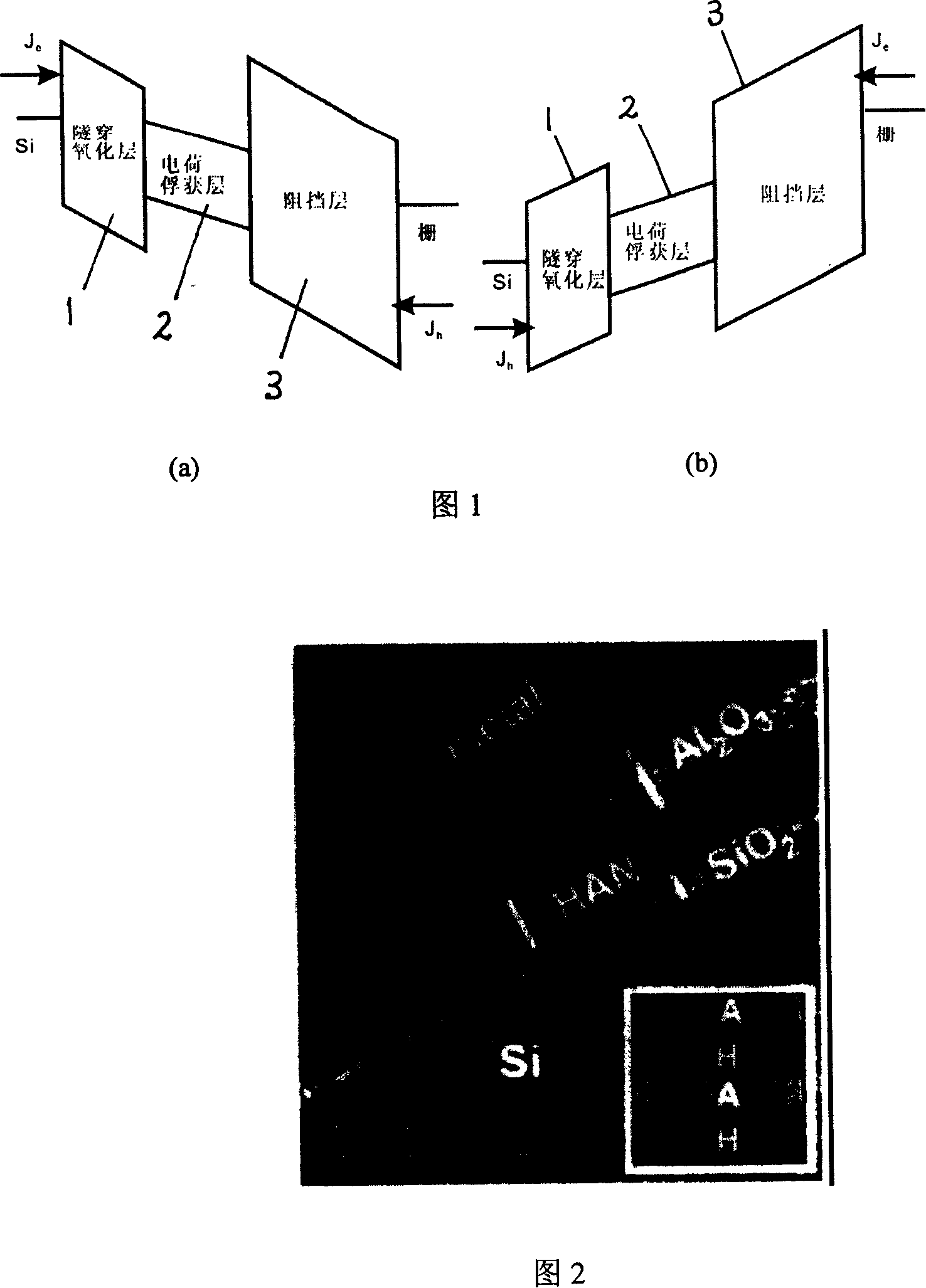

An erasable metal-insulator-silicon capacitor structure with high density

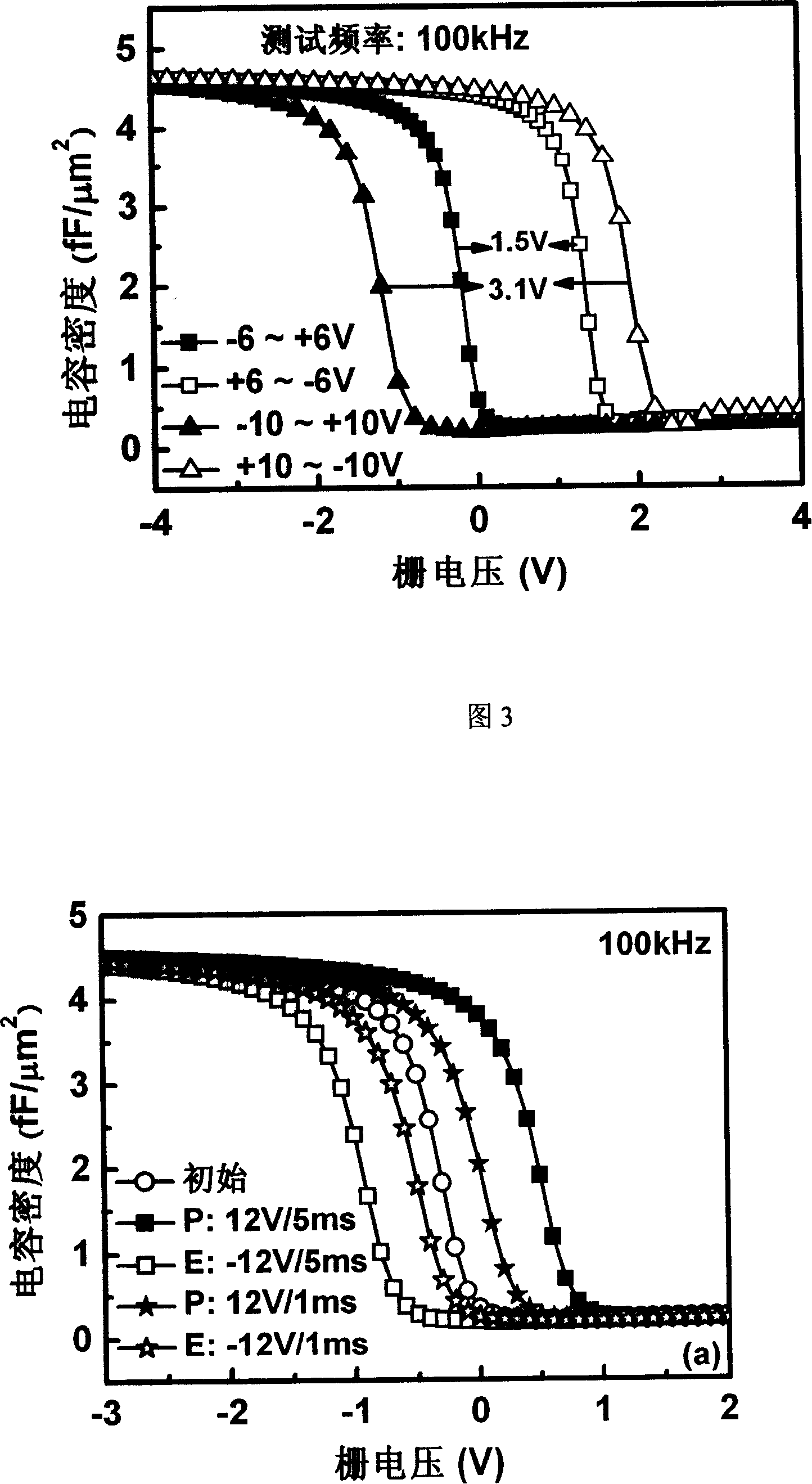

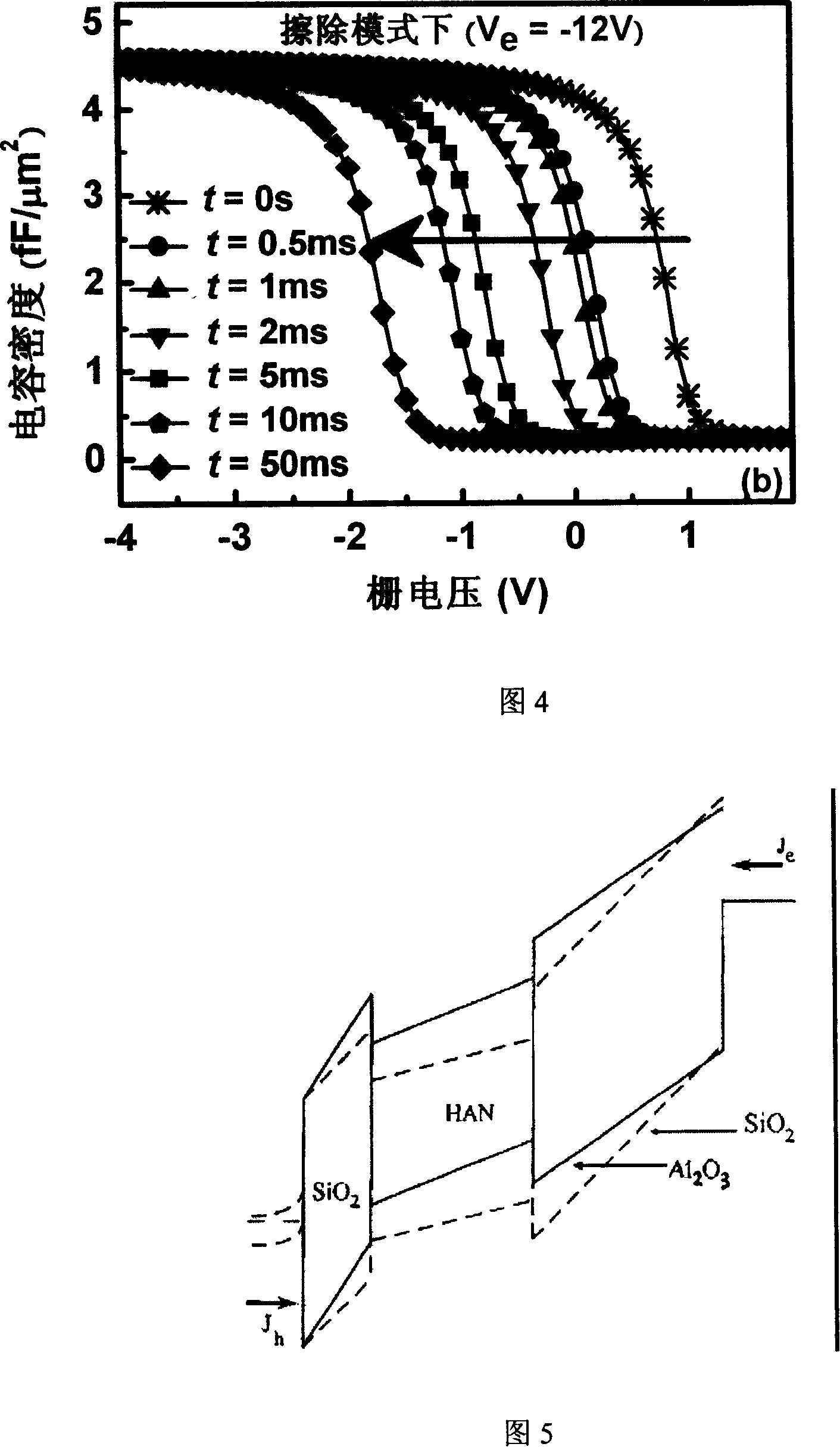

InactiveCN1964075AImprove storage characteristicsFast program/erase featureSolid-state devicesSemiconductor devicesCapacitanceHigh density

The related PE-MIS capacitor employs SiO2 / HfO2-Al2O3 nano (HAN) / Al2O3 medium structure, and has capacitance density up to 4.5fF / mum2, storage window up to 1.45V when programming at 12V voltage and erasing for 5ms at -12V voltage. This invention increases voltage drop on SiO2 layer, and thereby prevent Fowler-Nordheim tunneling current efficiently.

Owner:FUDAN UNIV

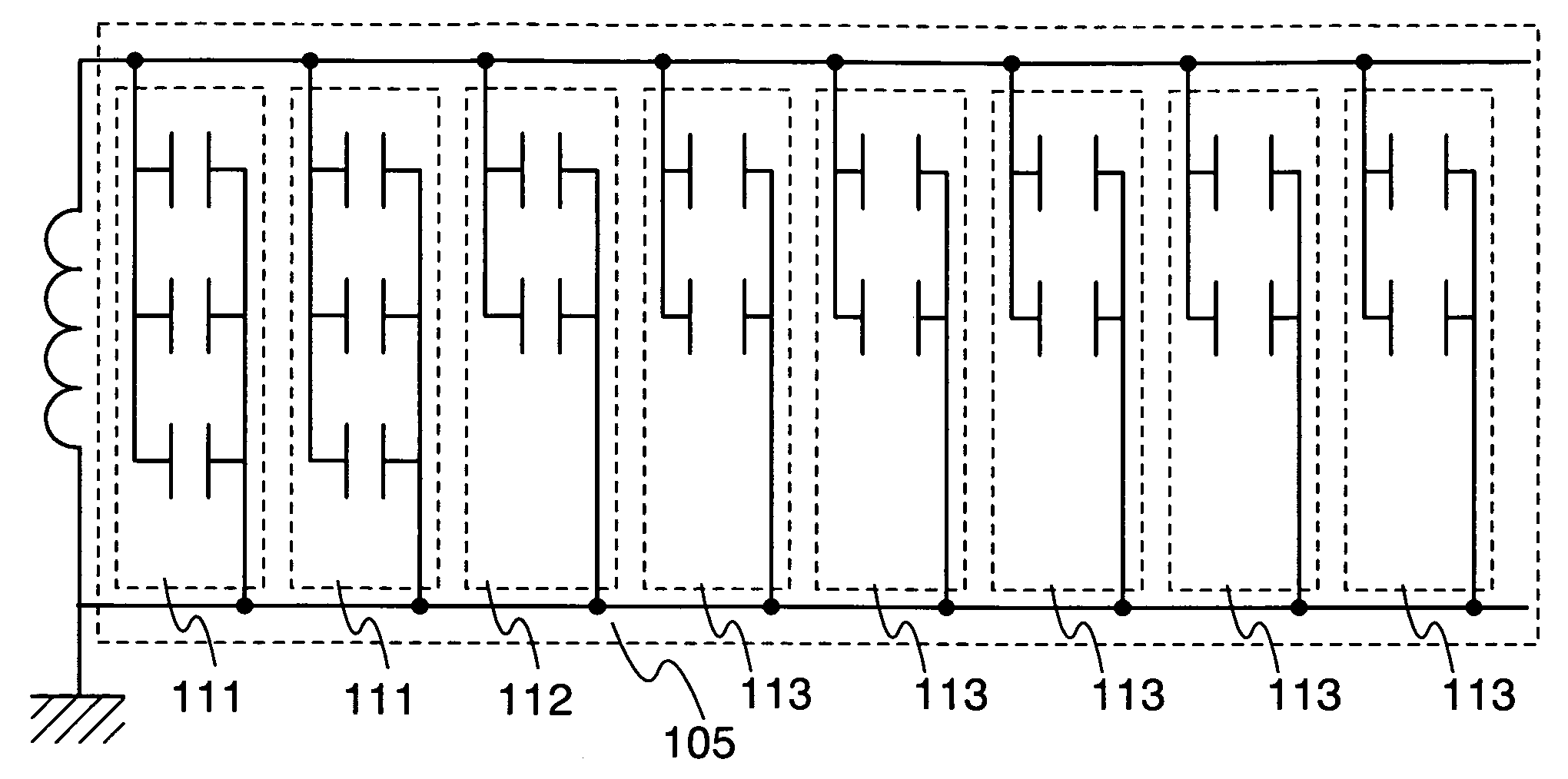

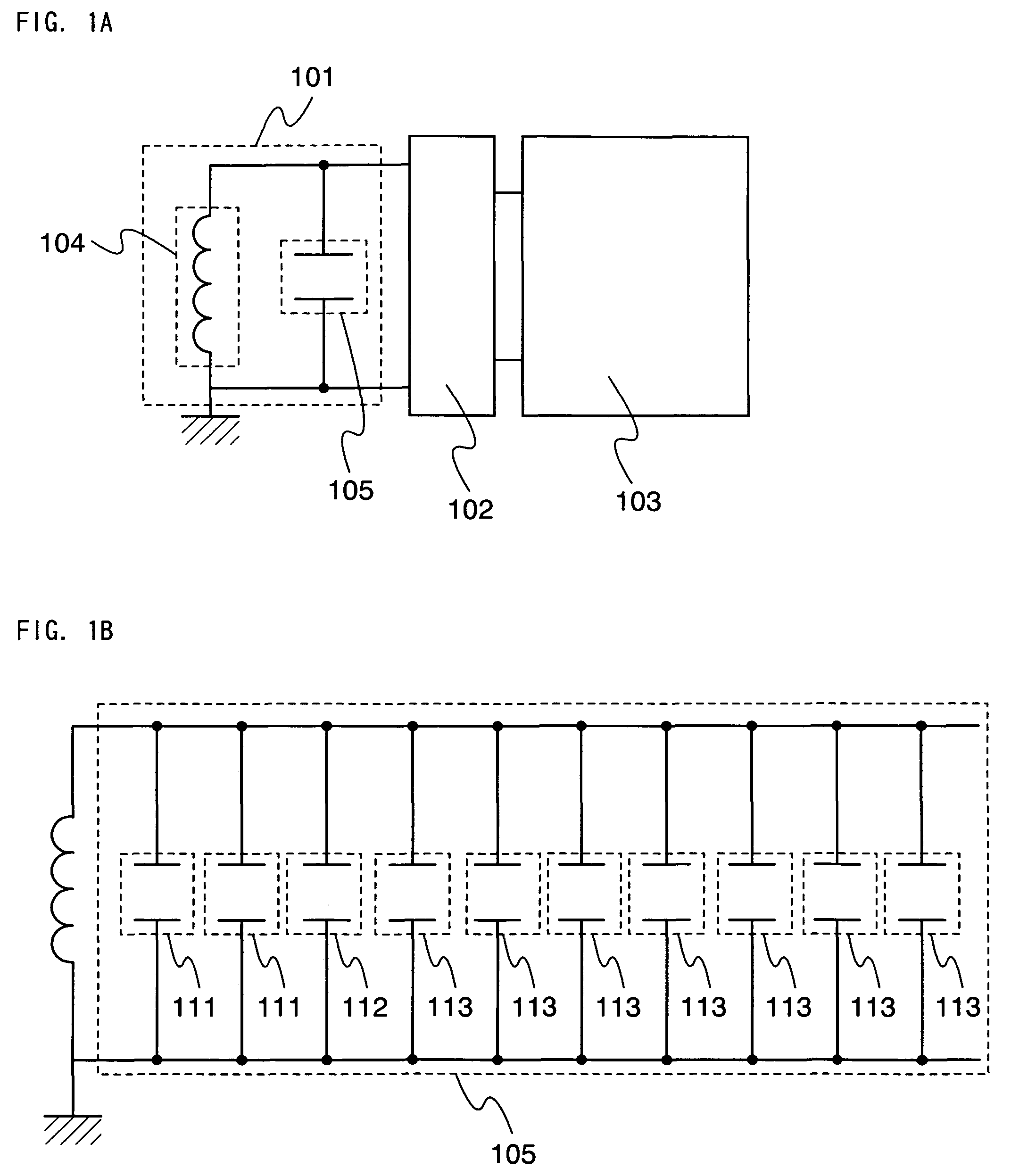

Semiconductor device including resonance circuit

InactiveUS7923796B2Easy to adjustEasy to getSolid-state devicesSemiconductor/solid-state device manufacturingCapacitancePower semiconductor device

It is an object of the present invention to provide a semiconductor device in which an arrangement area of capacitance can be reduced and resonance frequency can be easily adjusted. The semiconductor device includes an antenna and a resonance circuit including a capacitor connected to the antenna in parallel where the capacitor is formed by connecting x pieces of first capacitor (x is an arbitrary natural number), y pieces of second capacitor (y is an arbitrary natural number), and z pieces of third capacitor (z is an arbitrary natural number) in parallel; and the first capacitor, the second capacitor, and the third capacitor have different capacitance values from each other. It is preferable that each of the first capacitor, the second capacitor, and the third capacitor be a MIS capacitor. Further, at least one of the first capacitor, the second capacitor, and the third capacitor is preferably formed by connecting a plurality of capacitors in parallel.

Owner:SEMICON ENERGY LAB CO LTD

Manufacturing process of low electromagnetic interference power device terminal structure

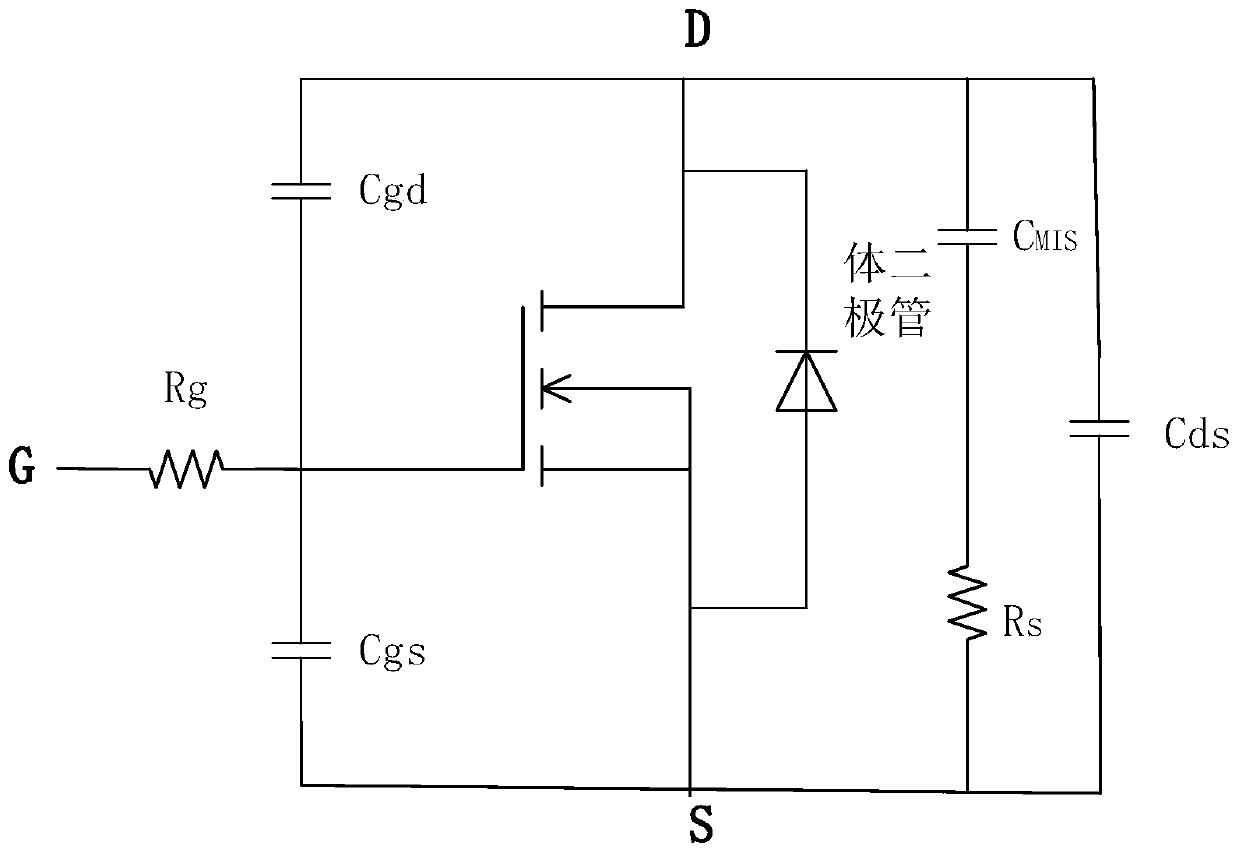

ActiveCN110854072AReduce noiseSemiconductor/solid-state device detailsSolid-state devicesCapacitanceMIS capacitor

The invention provides a manufacturing process of a low electromagnetic interference power device terminal structure. The terminal structure manufactured by the process comprises a metallized drain electrode, a first conductive type semiconductor substrate and a first conductive type semiconductor epitaxial layer, a second conductive type semiconductor main junction, a second conductive type semiconductor equipotential ring, a first conductive type cut-off ring, a second conductive type semiconductor field limiting ring, a first dielectric layer, a second dielectric layer, a third dielectric layer, a conductive field plate, a resistor and a metallized source electrode which are stacked from bottom to top. In the invention, an HK dielectric layer can be introduced between the field limitingring and the field plate. An MIS capacitor structure is formed by the semiconductor field limiting ring, the HK dielectric layer and the field plate and is connected in series with an adjacent polycrystalline silicon resistor so that an RC absorption network is formed between high potentials of the source electrode and the drain electrode, dv / dt and di / dt generated by a power device in a fast switch can be effectively inhibited, and an EMI noise is relieved.

Owner:四川民承电子有限公司

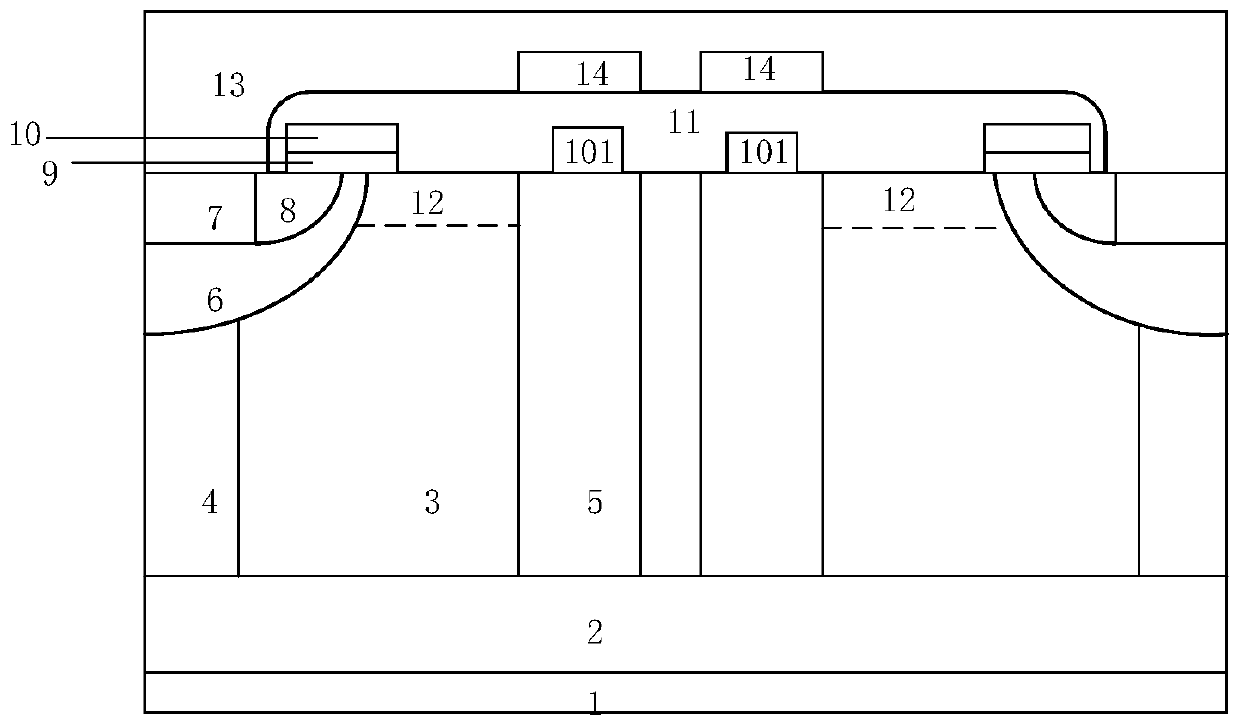

High-K dielectric groove lateral double-diffused metal oxide element semiconductor field effect transistor and manufacturing method thereof

ActiveCN108565286AUniform internal electric field distributionModulation of electric field distribution in the bodySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSemiconductor materials

The invention provides a high-K dielectric (HK) groove lateral double-diffused metal oxide element semiconductor field effect transistor (LDMOS) and a manufacturing method thereof. According to the device, a deep groove high dielectric constant dielectric layer is formed on the drain end, the lower end of the high-K dielectric groove layer goes deep into the epitaxial layer arranged on the substrate of the device and the upper end is connected with the drain electrode of the device. The HK dielectric groove and the element semiconductor material substrate form an MIS capacitor structure, and the charges of the substrate of the device can be auxiliarily exhausted when the device is turned off so that the LDMOS having the low resistance substrate is enabled to acquire high breakdown voltage.Besides, the electric field distribution in the device body can be effectively modulated by the uniform electric field of the HK dielectric groove in case of device reverse voltage withstanding so that the longitudinal high electric field of the drain end of the device can be reduced, the breakdown voltage of the device can be enhanced and the problem of saturation of the breakdown voltage of theLDMOS along with increasing of the length of the drift region can be solved.

Owner:XIDIAN UNIV

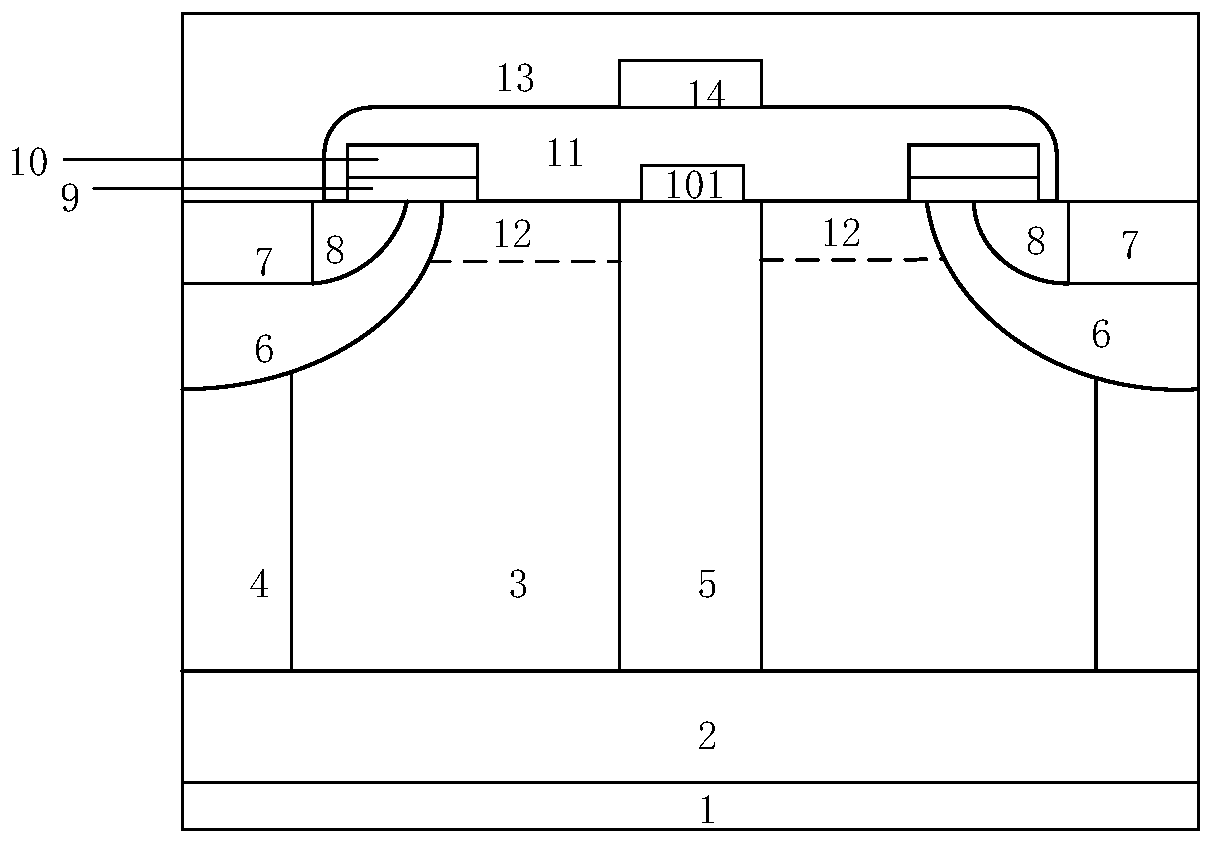

Integrated semiconductor metal-insulator-semiconductor capacitor

InactiveUS20060017084A1TransistorSolid-state devicesCapacitanceElectrical resistance and conductance

An integrated MIS capacitor has two substantially identical MIS capacitors. A first capacitor comprises a first region of a first conductivity type adjacent to a channel region of the first conductivity type in a semiconductor substrate. The semiconductor substrate has a second conductivity type. A gate electrode is insulated and spaced apart from the channel region of the first capacitor. The second capacitor is substantially identical to the first capacitor and is formed in the same semiconductor substrate. The gate electrode of the first capacitor is electrically connected to the first region of the second capacitor and the gate electrode of the second capacitor is electrically connected to the first region of the first capacitor. In this manner, the capacitors are connected in an anti-parallel configuration. A capacitor which has high capacitance densities, low process complexity, ambipolar operation, low voltage and temperature coefficient, low external parasitic resistance and capacitance and good matching characteristics for use in analog designs that can be integrated with existing semiconductor processes results.

Owner:SILICON STORAGE TECHNOLOGY

MiS capacitor structure and manufacturing method thereof

InactiveCN104851776AReduce process complexityReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMIS capacitor

The invention provides an MiS capacitor structure and a manufacturing method thereof. The manufacturing method comprises the steps of supplying a substrate with shallow trench isolations at two sides, defining an active region through N+ / P+ injection; depositing a shielding layer on the surface of the active region and patterning, exposing an active region between the shielding layer and the shallow trench isolation at one end; depositing a metal layer and an antireflection layer on the current structure; performing quick thermal annealing, thereby forming a leading-out end between the covered active region and the metal layer above the active region; performing spin coating of a photoresist layer and patterning, so as to etch the antireflection layer and the metal layer through utilizing the photoresist layer on a mask until the edge, the leading-out end and the shallow trench isolation are exposed; removing the photoresist layer and performing quick thermal annealing on the current structure; and depositining an interlayer medium layer above the current structure, and defining the positions of two contact holes in the current structure; wherein one contact hole is connected with the leading-out end, and the other contact hole penetrates through the antireflection layer and is connected with the metal layer. According to the MiS capacitor structure, process complexity and cost of the MiS capacitor are reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

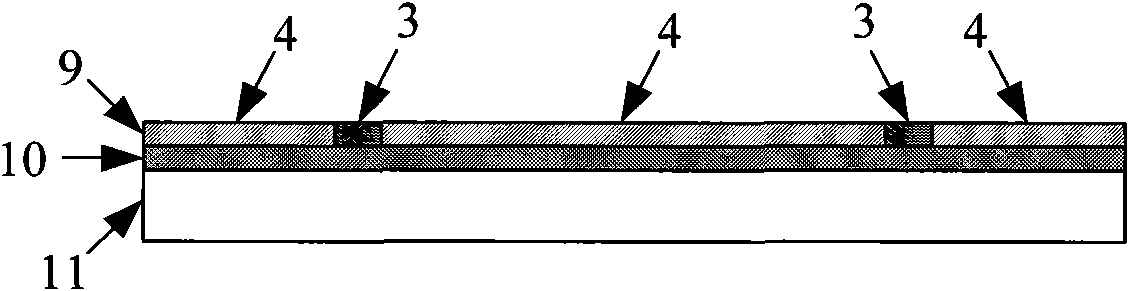

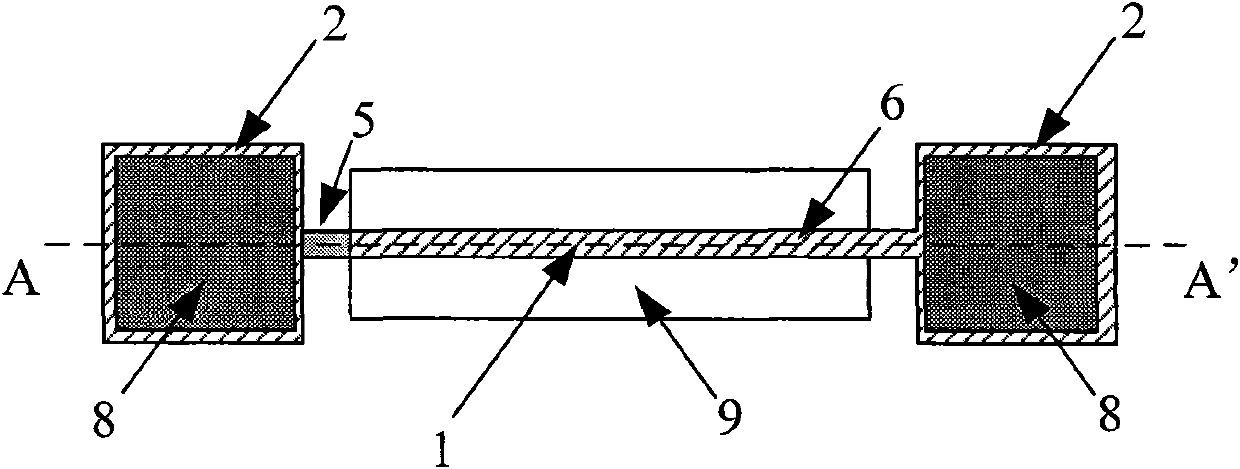

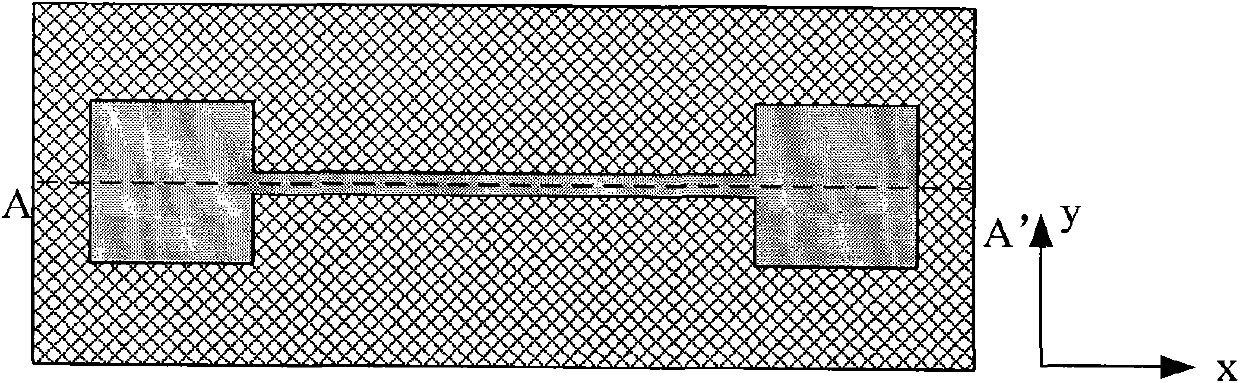

MIS capacitor lower piezoresistance structure adopting substrate grid and making method

InactiveCN102134052AAvoid stressReduce qualityTelevision system detailsImpedence networksCapacitanceMetal insulator

The invention relates to a metal insulator semiconductor (MIS) capacitor lower piezoresistance structure adopting a substrate grid and an automatic alignment processing technology for implementing the piezoresistance structure. The structure is used for detecting the displacement of a nano beam. According to the structure, the nano beam is made of top silicon of a silicon on insulator (SOI) chip,a silicon substrate is used as the grid, a silicon dioxide buried layer between the beam and the silicon substrate is removed by corroding to form a clearance, and the silicon substrate, the clearance and the nano beam form the MIS capacitor structure. A voltage is applied to the substrate grid so that a strong inversion layer is formed on the lower surface of the nano beam, and the inversion layer and the silicon above a space charge region are used as piezoresistors to realize piezoresistance detection of vibration of the nano beam. Automatic alignment of a light doped region on the beam and the substrate grid can be realized by combining a composite mask and corrosion of an anisotropic wet method.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

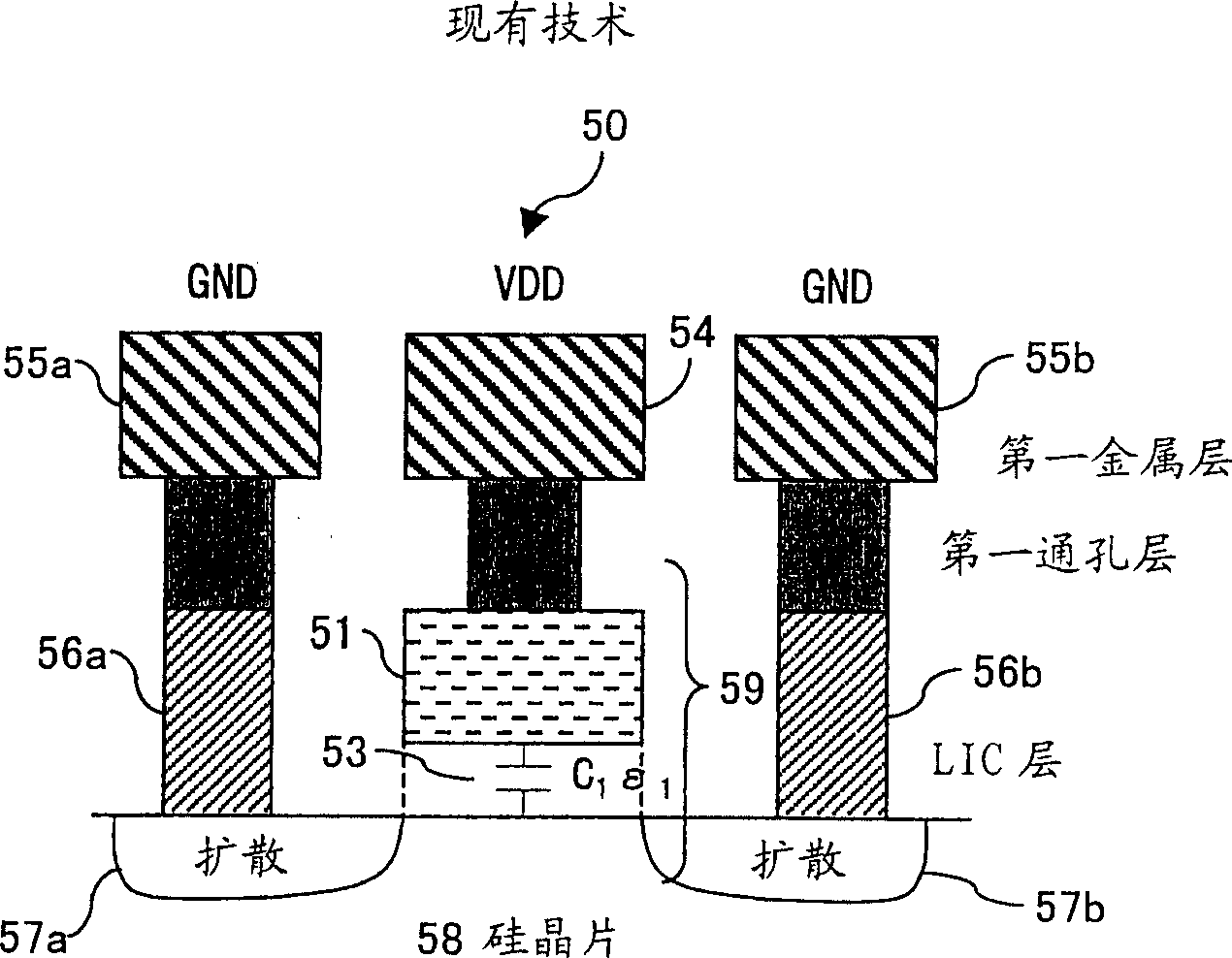

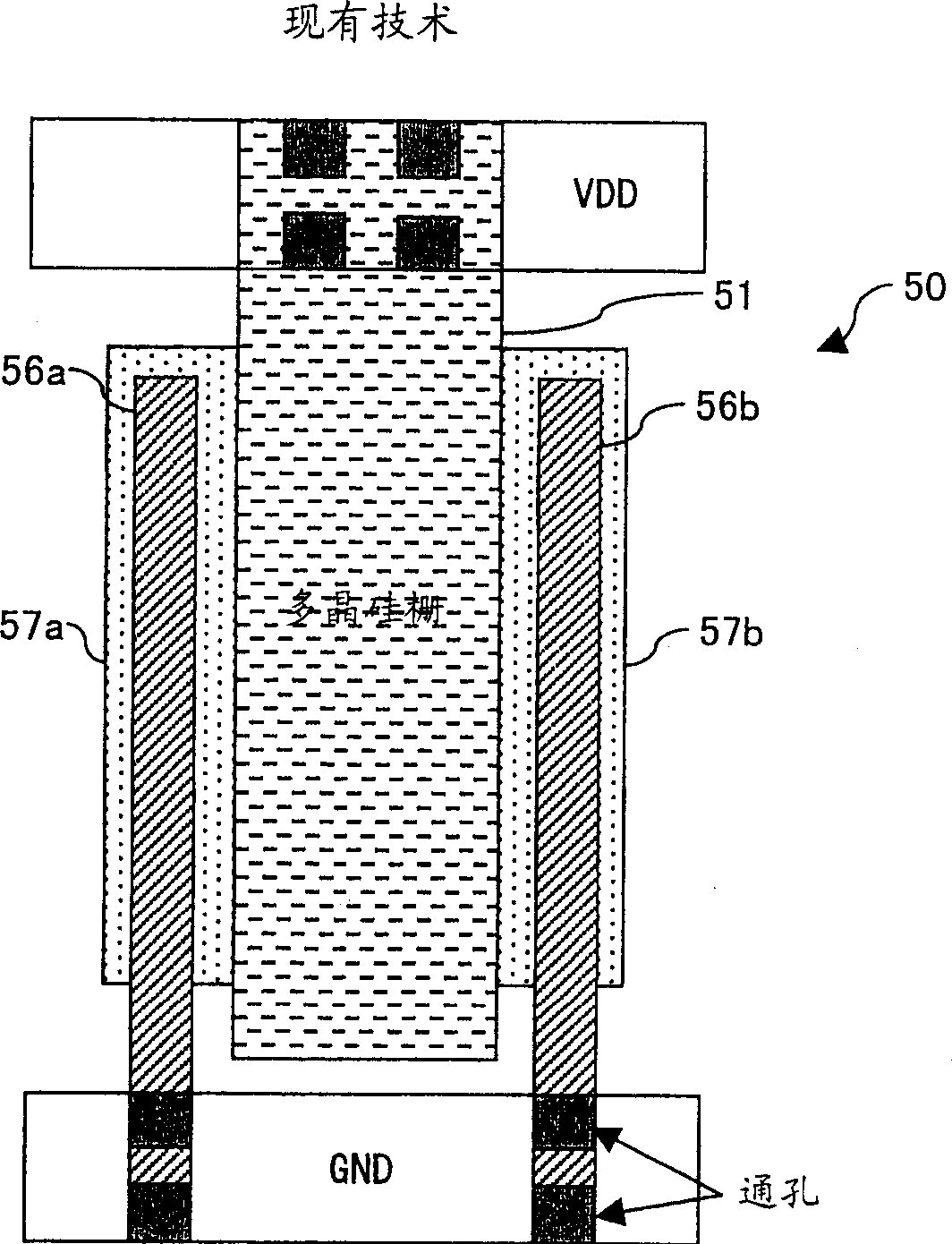

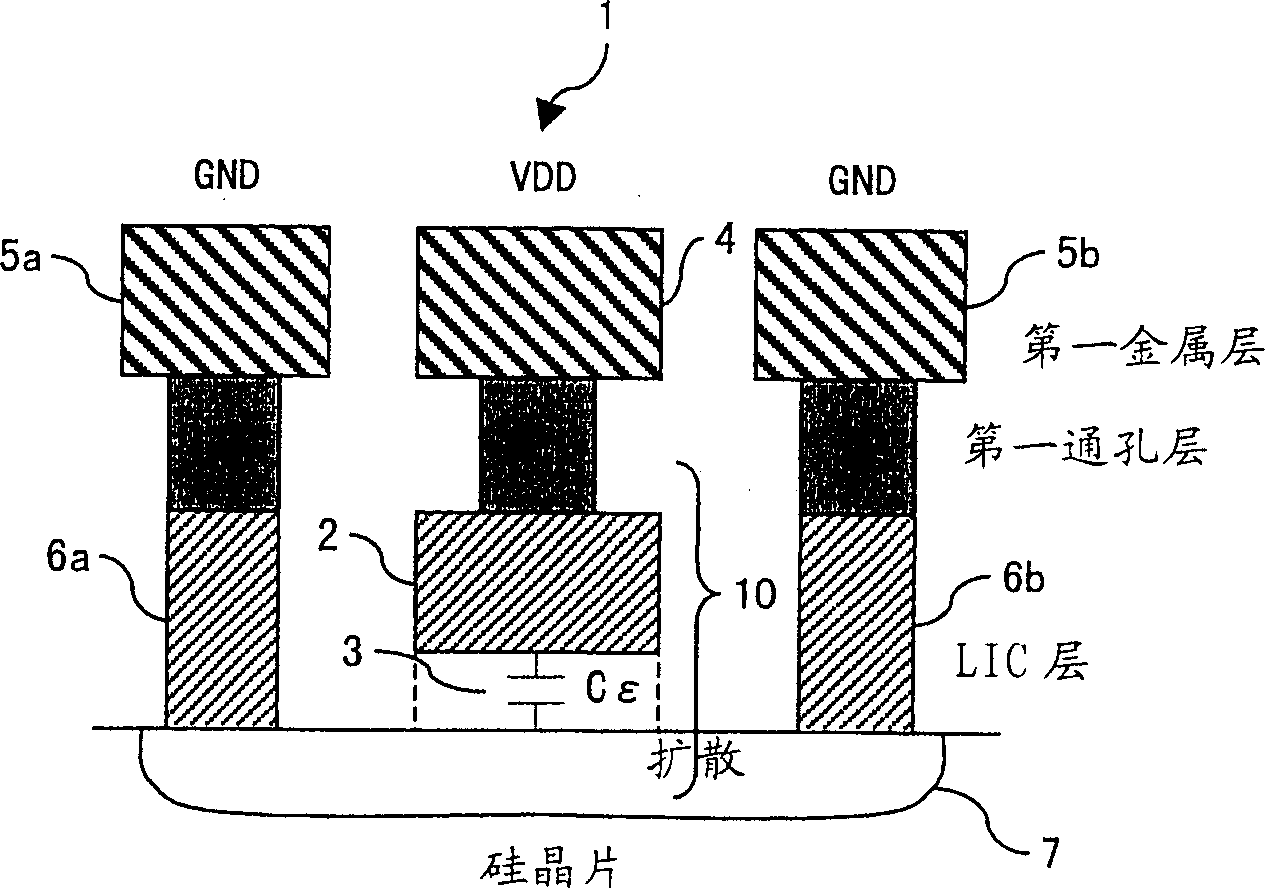

MIS capacitor and production method of MIS capacitor

InactiveCN1737990AReduce leakage currentNo need to change footprintSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringMIS capacitor

The present invention provides a MIS capacitor and a production method of MIS capacitor. A silicon wafer, with a diffusion area formed in a predetermined region on one side, comprises a lower electrode of a capacitor unit. A first metal layer is connected to a first power supply wiring (VDD) and comprises an upper electrode of the capacitor unit. Second metal layers are connected to a second power supply wiring (GND) and are also formed on the side where diffusion area is formed on silicon wafer. An oxide film is placed between the first metal layer and the surface of the silicon wafer where the diffusion area is formed.

Owner:FUJITSU LTD

Thin-layer capacitor and method of fabricating the same

ActiveUS11276530B2Short timeThin/thick film capacitorFixed capacitor dielectricDevice materialEngineering

An MIM capacitor or an MIS capacitor in semiconductor devices is formed of a thin dielectric layer having a total film thickness less than 100-nm and including a high-dielectric-constant amorphous insulating film, high-breakdown-voltage amorphous films such as of SiO2, and high-dielectric-constant amorphous buffer films between an upper electrode and a lower electrode. The thin high-dielectric-constant amorphous insulation film is formed of a material having a property resistant to fracture although having properties of a large leakage current and a low breakdown voltage, to enhance reliability of the thin dielectric layer and to reduce the footprint thereof in the semiconductor device.

Owner:MITSUBISHI ELECTRIC CORP

Anti-EMI super junction VDMOS device

ActiveCN111244179ADoes not affect static electrical parametersEMI mitigationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHemt circuits

The invention relates to an anti-EMI super-junction VDMOS device, and belongs to the technical field of power semiconductor devices. According to the anti-EMI super-junction VDMOS device provided by the invention, a high-K dielectric material column is introduced into a drift region, and an MIS capacitor is formed by the high-K dielectric material column, a first conductive type substrate which islongitudinally adjacent to the high-K dielectric material column and a polycrystalline silicon electrode. he resistor is arranged on the dielectric layer, and the resistor is in direct contact with the metallized source electrode, so that the resistor and the MIS capacitor which are connected in series are introduced between the drain electrode and the source electrode to form an RC absorption circuit, and effective alleviation of voltage and current overshoot is realized. Therefore, the structure of the invention effectively alleviates the electromagnetic interference problem of the device on the basis of ensuring the original basic electrical properties of the super-junction VDMOS.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

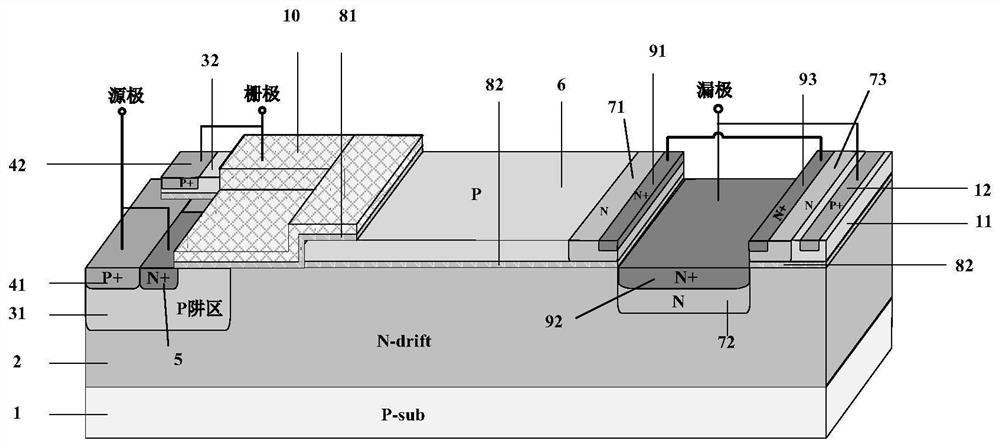

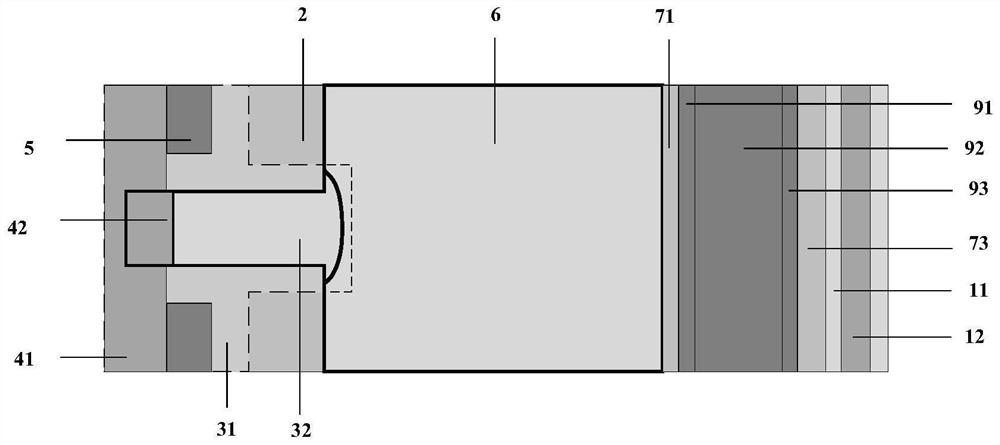

High-voltage low-resistance power LDMOS

The invention belongs to the technical field of power semiconductors, and particularly relates to a high-voltage low-resistance power LDMOS. The LDMOS is mainly characterized by being provided with a field plate structure with a protruding source end and an integrated diode on the inner side of a drain electrode, the length of a drift region is shortened, and the device area is not additionally increased. During forward conduction, an integrated diode is reversely biased, a field plate structure and an N-type drift region form an equivalent MIS capacitor, a continuous electron accumulation layer is generated on the surface of the drift region below a gate structure and the field plate structure, an accumulation type transport mode is formed, and the specific on-resistance of the device is greatly reduced; during reverse blocking, the integrated diode is positively biased, the field plate structure bears surface withstand voltage, the drift region is assisted to be depleted so as to improve the doping concentration of the drift region and reduce the specific on-resistance, and transverse electric field distribution is modulated so as to improve the withstand voltage of the device. Compared with a traditional LDMOS, the LDMOS provided by the invention has lower specific on-resistance while realizing high withstand voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

MIS capacitor and method of formation

InactiveUS20060244027A1Reduce leakageIncrease capacitanceTransistorSolid-state devicesCapacitanceOxide composite

Owner:ROUND ROCK RES LLC

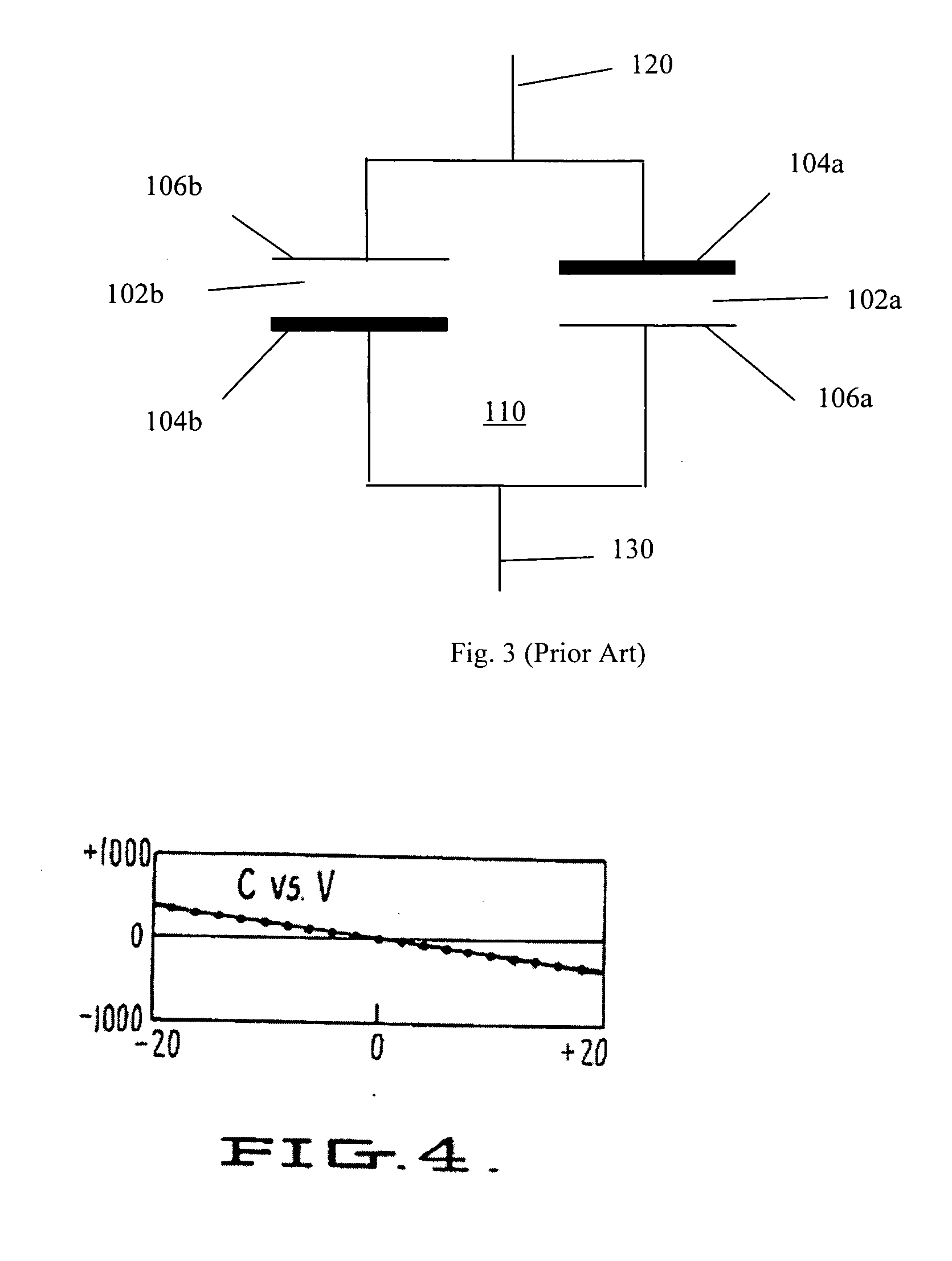

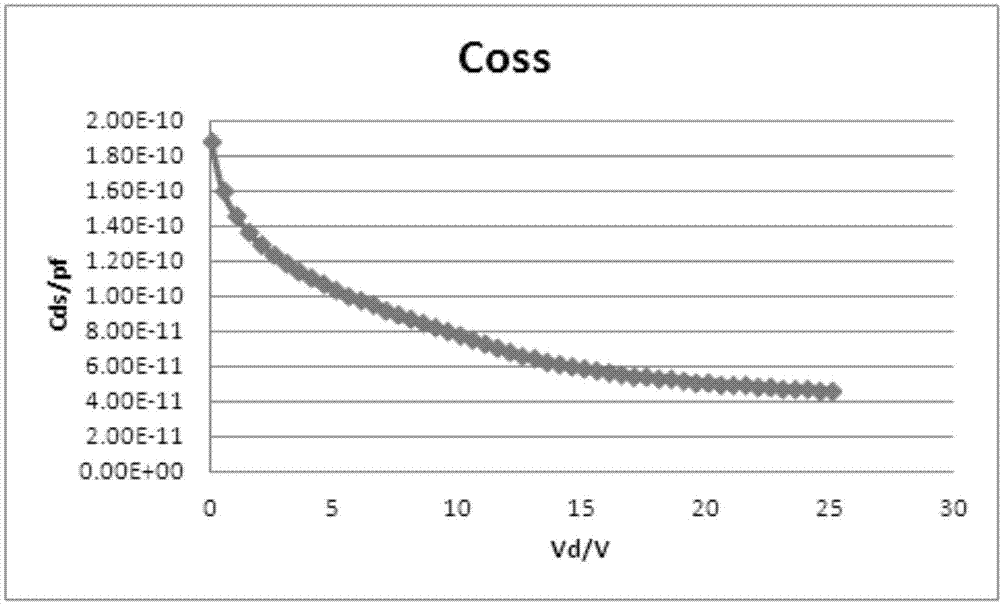

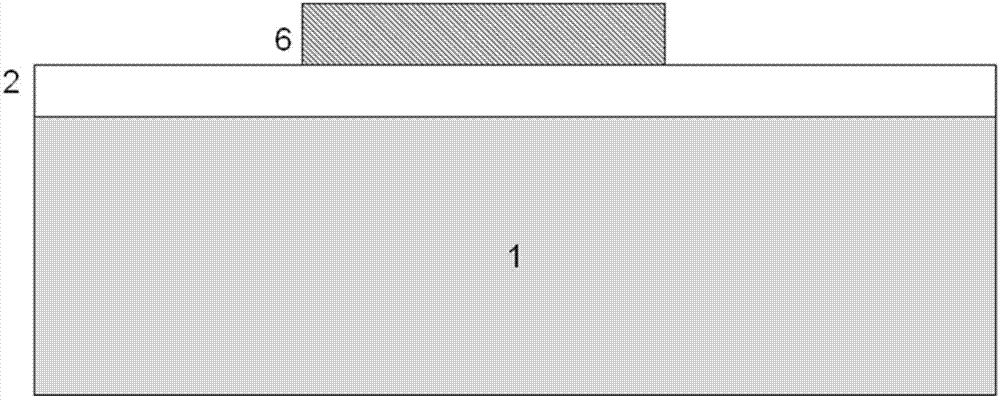

Structure of MIS capacitor with capacitance being variable and manufacturing method thereof

ActiveCN104299902AReduce non-linearityIncrease output powerSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceConcentration gradient

The invention discloses a manufacturing method of an MIS capacitor with the capacitance being variable, which comprises the steps of 1) growing an N-type lightly doped epitaxy on an N-type heavily doped substrate; 2) growing a sacrificial oxidation layer; 3) defining an N-type ion implantation region and vertically implanting N-type ions; 4) implanting the N-type ions by an oblique angle; 5) removing a photoresist and carrying out thermal annealing; 6) removing the sacrificial oxidation layer and further depositing an oxidation layer; and 7) depositing a metal layer. The invention further discloses a structure of the MIS capacitor. A transverse wave-shaped concentration gradient of the implanted ions is formed in an N-type lightly doped epitaxial layer of the MIS capacitor through the vertical N-type ion implantation and the angled N-type ion implantation and diffusion after implantation. The structure enables the capacitance of the MIS capacitor to be increased along with increase in impressed voltage, the capacitance forms complementation with output capacitance of an RFLDMOS, and the nonlinearity of the output capacitance along with voltage can be reduced through parallel connection and internal matching of the MIS capacitor and the output capacitance of the RFLDMOS.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP