High-voltage low-resistance power LDMOS

A power-resistance and high-voltage technology, applied in the field of power semiconductors, to achieve the effect of large breakdown voltage and small specific on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

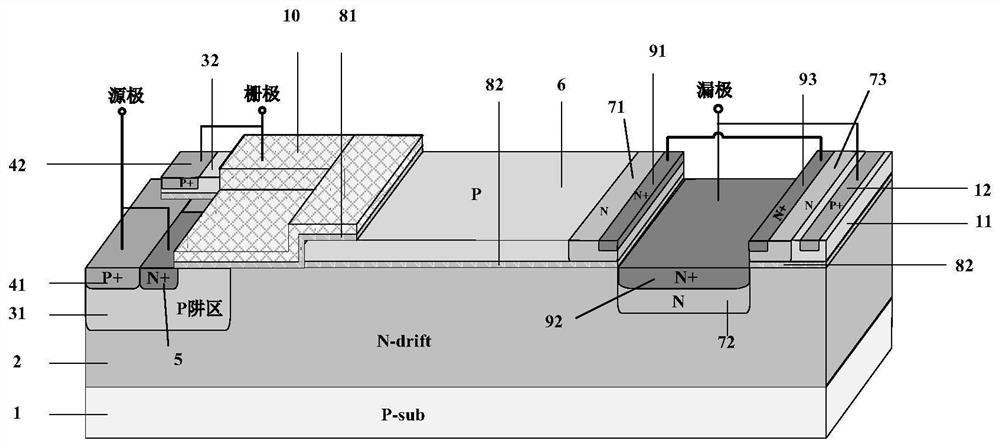

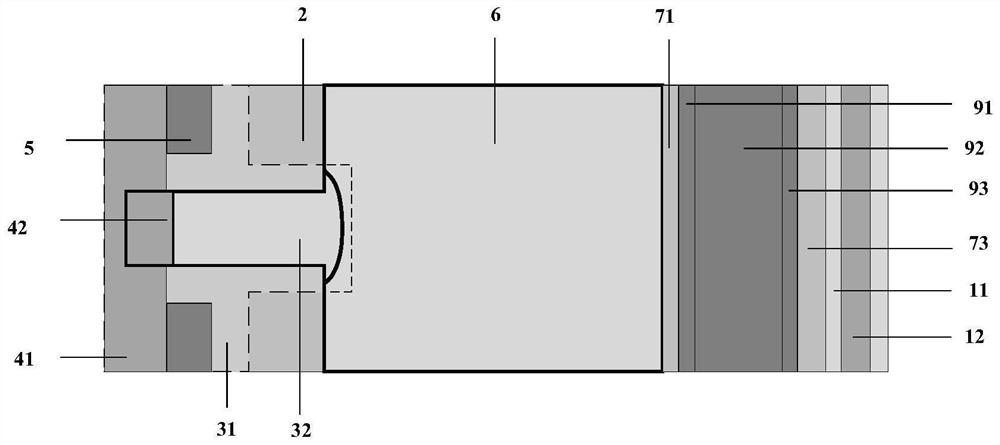

[0020] like figure 1 , 2 As shown, it is a high-voltage low-resistance power LDMOS in this example, which includes a P substrate 1, an N drift region 2, and a top-layer structure that are sequentially stacked from bottom to top along the vertical direction of the device. The top-layer structure includes a field plate structure and an integrated Diode structure;

[0021] Along the lateral direction of the device, the surface of the N drift region 2 includes a source structure, a gate structure, and a drain structure from one side to the other; the field plate structure and the integrated diode are respectively located on both sides of the drain structure, and the The field plate structure is located between the source structure and the drain structure;

[0022] The source structure includes a P well region 31, a P+ body contact region 41, and a first N+ heavily doped region 5; the P+ body contact region 41 and the first N+ heavily doped region 5 are in contact with each other...

Embodiment 2

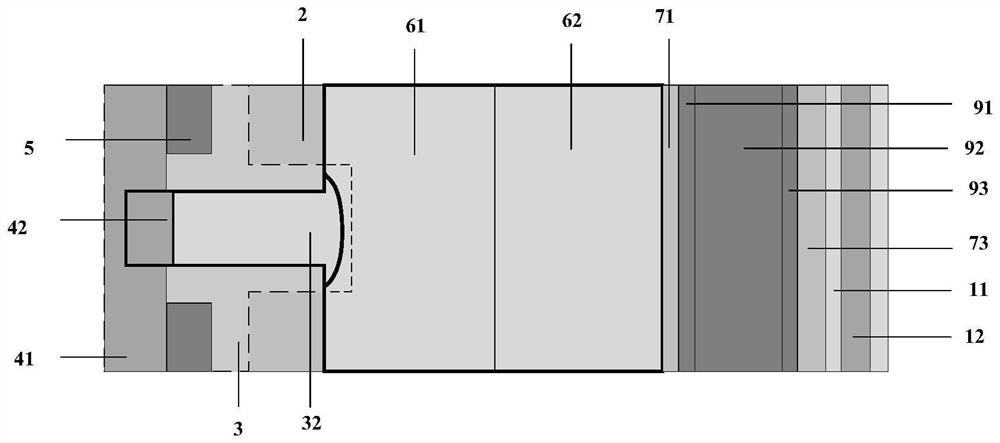

[0029] like image 3 As shown, the difference between this example and Example 1 is that in the field plate structure described in this example, the P-type region 6 includes a first P+ heavily doped region 42 from the source terminal to the drain terminal along the lateral direction of the device, a P well doped impurity region 32, P-type first-order doped region 61, P-type second-order doped region 62, N-doped region 71 and third N+ heavily doped region 91; wherein P-type first-order doped region 61 and P-type second-order doped region The doping concentration of the step-doped region 62 is from high to low in the direction from the source structure to the drain structure.

[0030] Compared with Embodiment 1, the field plate structure has a better effect on modulating the lateral electric field distribution of the device, and this embodiment can obtain a higher withstand voltage under the same device size.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More