MIS capacitor and production method of MIS capacitor

A capacitor and power supply technology, applied in the field of MIS capacitors, can solve the problems of increasing leakage current, increasing and reducing chip power consumption, and achieving the effect of increasing capacitance and controlling high-frequency noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The preferred embodiments are described in detail below with reference to the drawings.

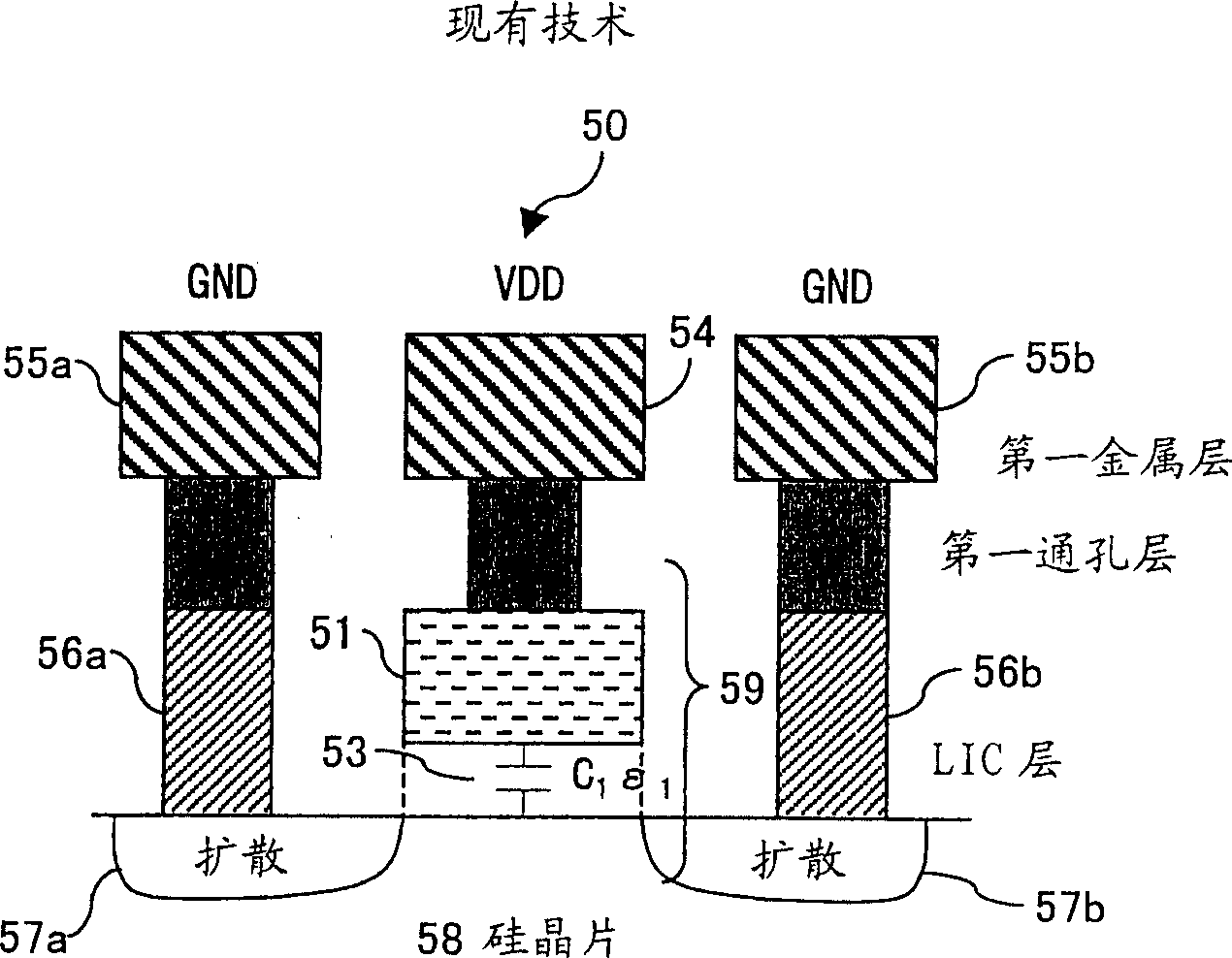

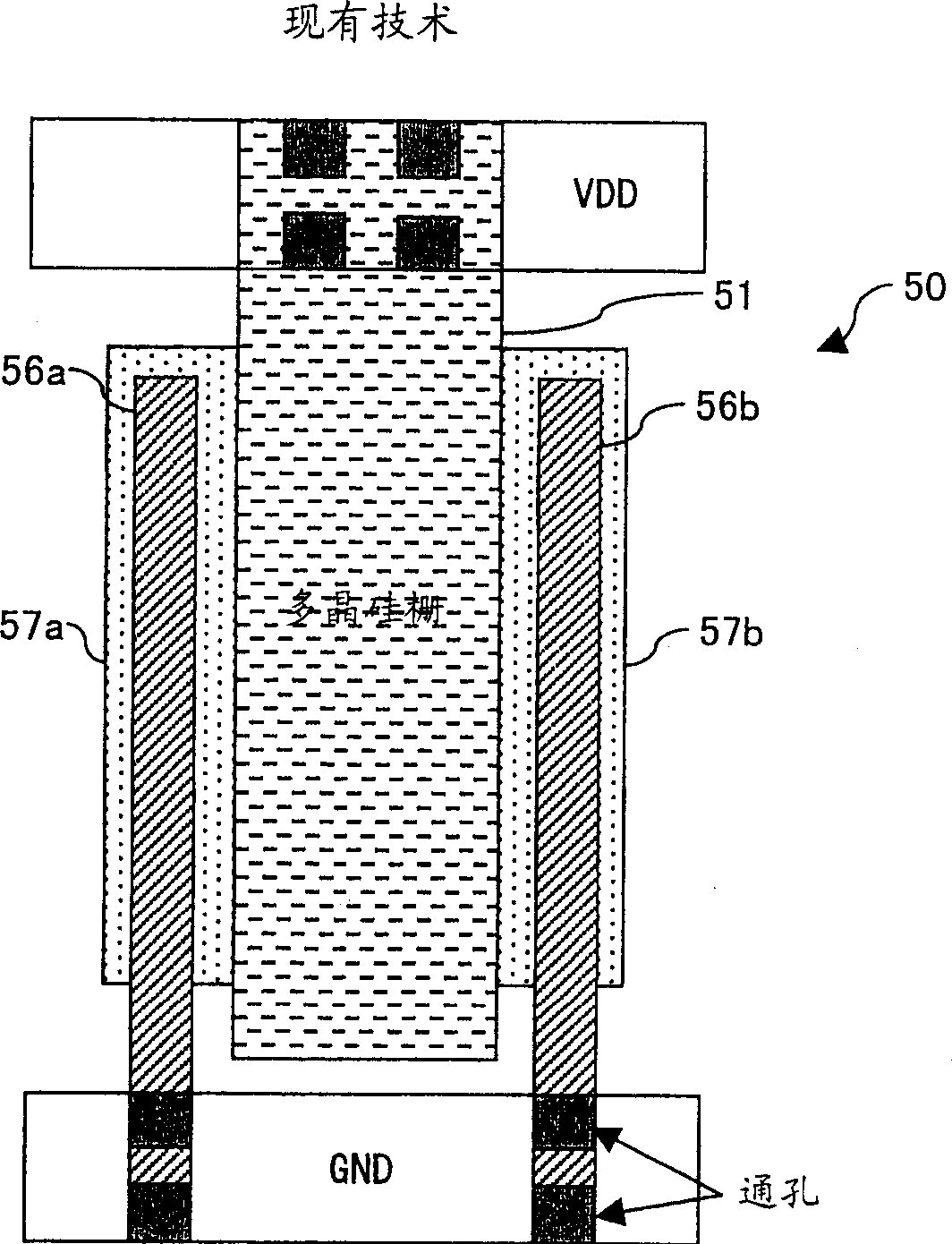

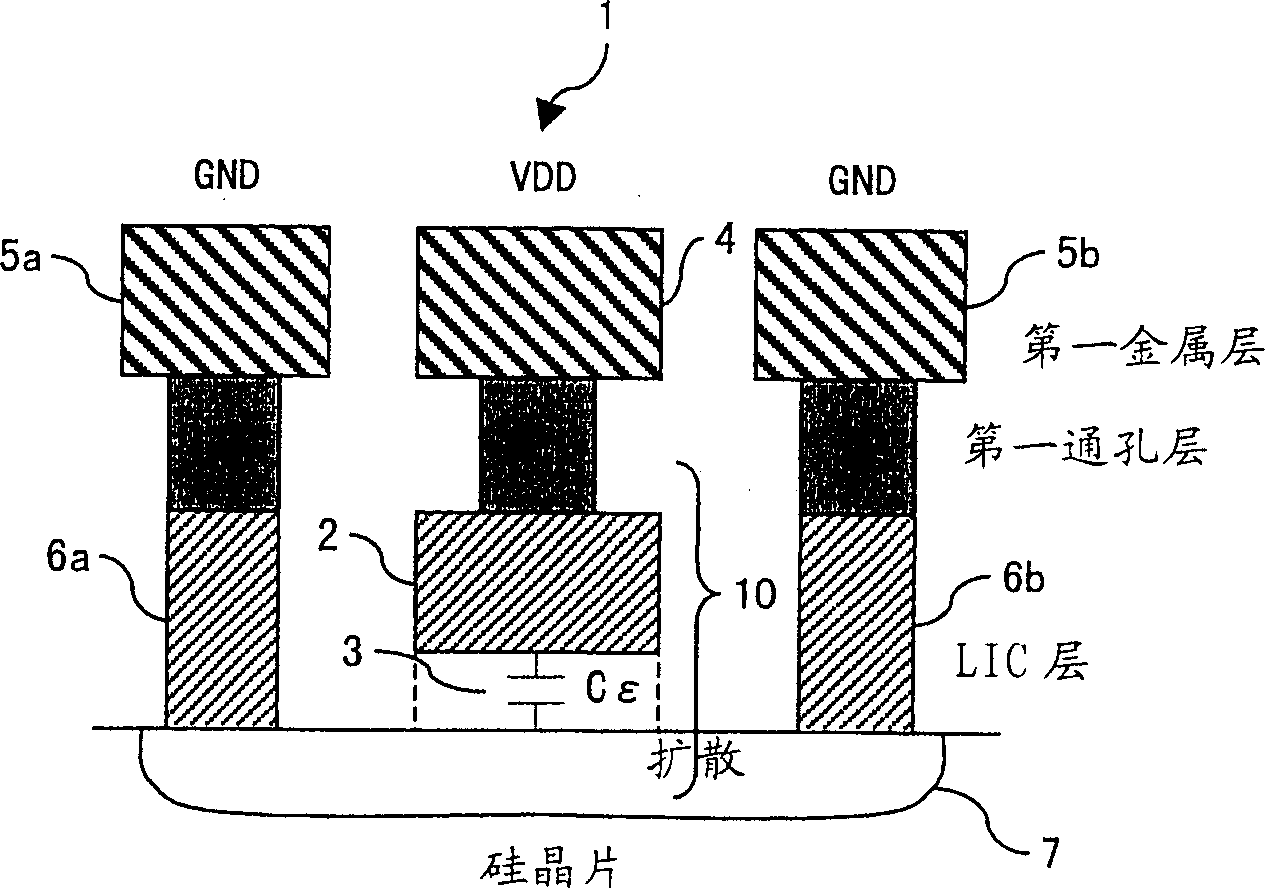

[0026] image 3 It is a cross-sectional view of the MIS (Metal-Insulator-Silicon) capacitor of this embodiment. Figure 4 The top view of the MIS (metal-insulator-silicon) capacitor of this embodiment is shown. On the silicon wafer 8, there are a local interconnection (LIC) layer 2 made of a material such as tungsten, and LIC layers 6 a and 6 b directly bonded on the silicon wafer 8. The LIC layer 2 is bonded on the silicon wafer 8 through an oxide film such as a field oxide film 3. The wiring layer 4 connected to the power supply wiring VDD is provided on the first via layer mounted on the LIC layer 2. The wiring layers 5a and 5b connected to the power wiring GND are respectively provided on the first via layer mounted on the LIC layers 6a and 6b. A diffusion region 7 is formed on the surface of the silicon wafer 8 connected to the field oxide film 3 between the LIC layer 2 and the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More