Static random access memory (SRAM) circuit device employing hierarchical bit lines and two-stage sensitive amplifier

A technology of sensitive amplifiers and hierarchical bit lines, which is applied in the direction of instruments, static memory, digital memory information, etc., can solve the problems of increasing the reading delay and increasing the buffer level, so as to reduce the circuit access delay, increase the speed, and improve the speed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be described in more detail below in conjunction with the accompanying drawings and embodiments.

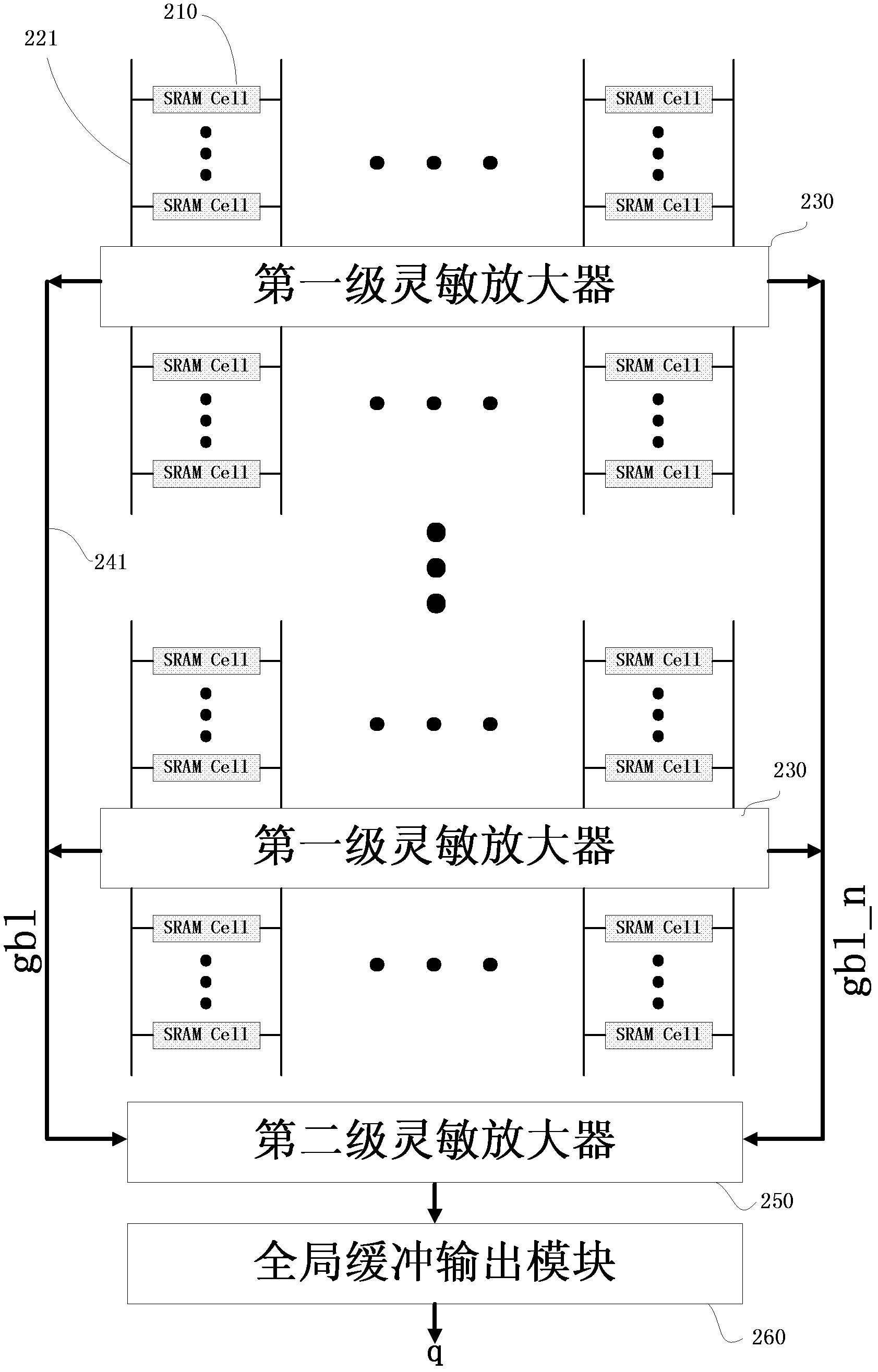

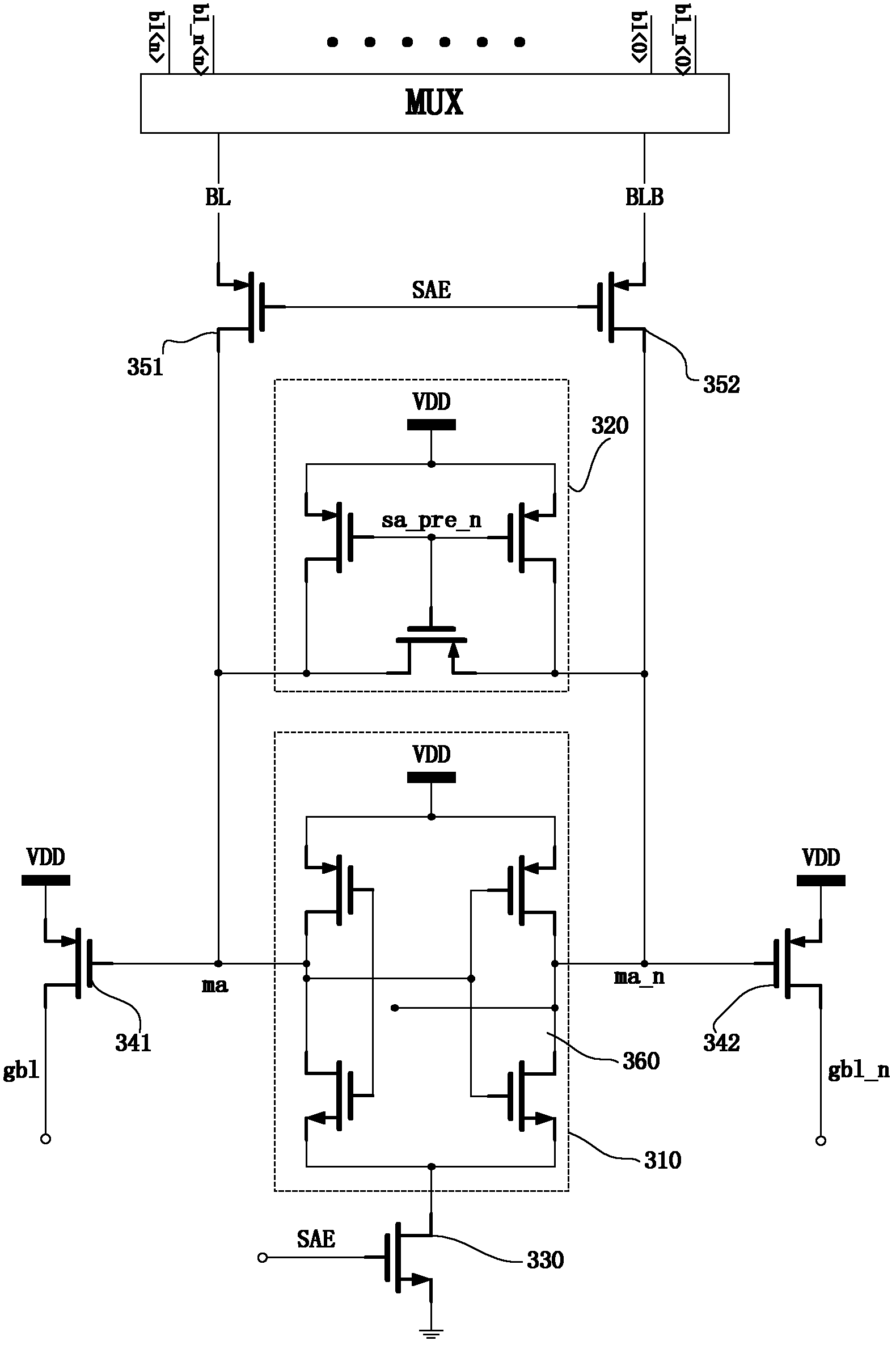

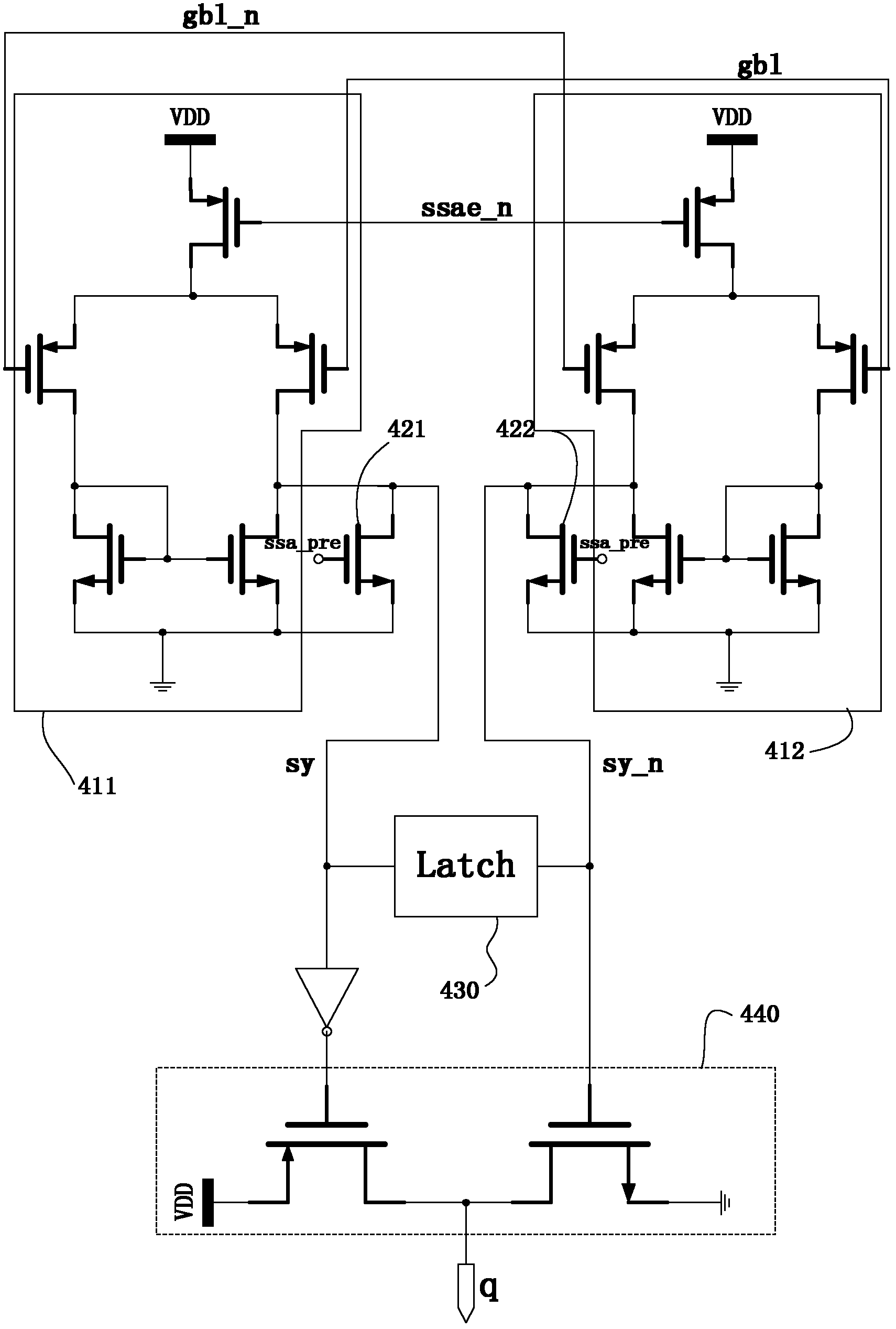

[0017] Such as figure 1 As shown, the SRAM circuit device adopting hierarchical bit lines and two-stage sense amplifiers, this embodiment includes more than one SRAM cell array, and each SRAM cell array includes sixty-four SRAM cells 210, and each SRAM cell array in each SRAM cell array Each SRAM cell 210 is connected with two local bit lines 221 corresponding to the SRAM cell array, and the two local bit lines 221 form a local bit line group, and more than one local bit line group is corresponding to a first The first-stage sense amplifiers 230 are electrically connected, and eight first-stage sense amplifiers 230 form a first-stage sense amplifier row, and the output ports of all first-stage sense amplifiers 230 of the same first-stage sense amplifier row are all the same as the corresponding two global The bit lines 241 are electrically conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More