Complementary metal oxide semiconductor (CMOS)-process-based Hall switch offset voltage elimination method and circuit

An offset voltage, Hall switch technology, applied in electronic switches, electrical components, pulse technology, etc., can solve the problem of affecting the output state of the Hall switch, cannot completely eliminate the effect of the Hall chip offset voltage, and does not consider the hysteresis comparator offset voltage and other problems to achieve the effect of eliminating offset voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with accompanying drawing:

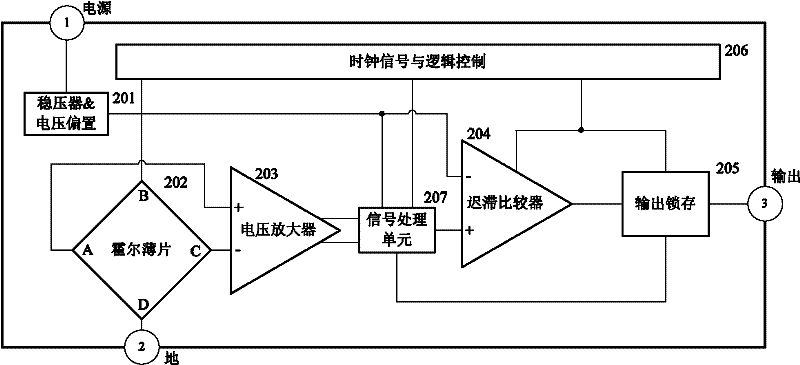

[0021] figure 2 An embodiment of the method for eliminating the offset voltage of the present invention is given, consisting of voltage regulator & voltage bias 201, Hall sheet 202, Hall voltage amplifier 203, signal processing unit 207, hysteresis comparator 204, output latch 205 and Clock signal and logic control 206 components.

[0022] The voltage regulator & voltage bias 201 provides stable voltage and current bias for other circuits, the Hall sheet 202 induces magnetic signals and converts them into voltage signals, and the voltage amplifier 203 amplifies the collected Hall voltage signals. After the signal processing unit 207, the offset voltage is eliminated, the processed voltage signal is compared with the set threshold voltage in the hysteresis comparator 204, and the corresponding voltage signal is output to the output latch 205, and the clock signal and logic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More