Time-interleaving analogue-to-digital converter capable of suppressing sampling time mismatching

An analog-to-digital converter and time-interleaving technology, which is applied in the field of structure design of time-interleaving analog-to-digital converters, can solve the problems of increasing the relative error of the signal bandwidth, increasing the on-resistance and parasitic capacitance of the signal path, and increasing the bandwidth mismatch.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the figures.

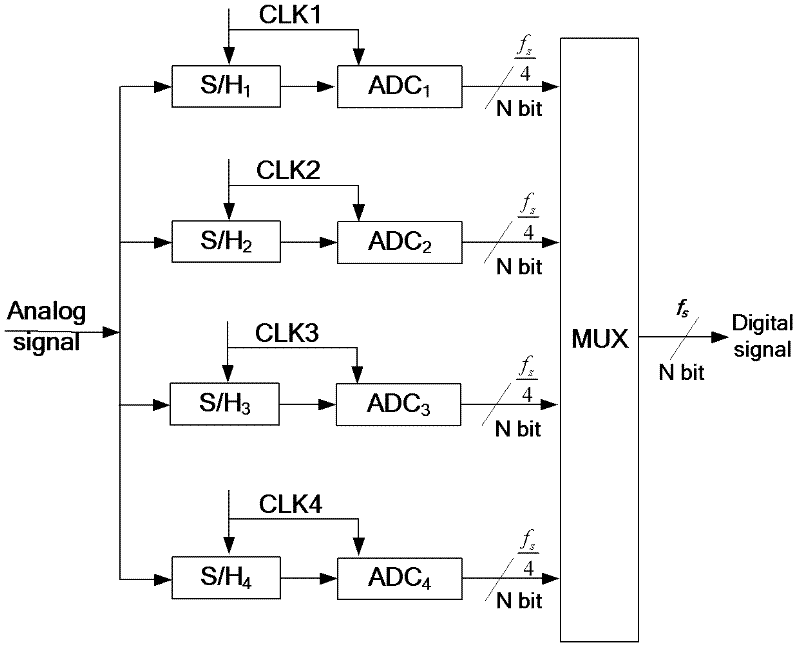

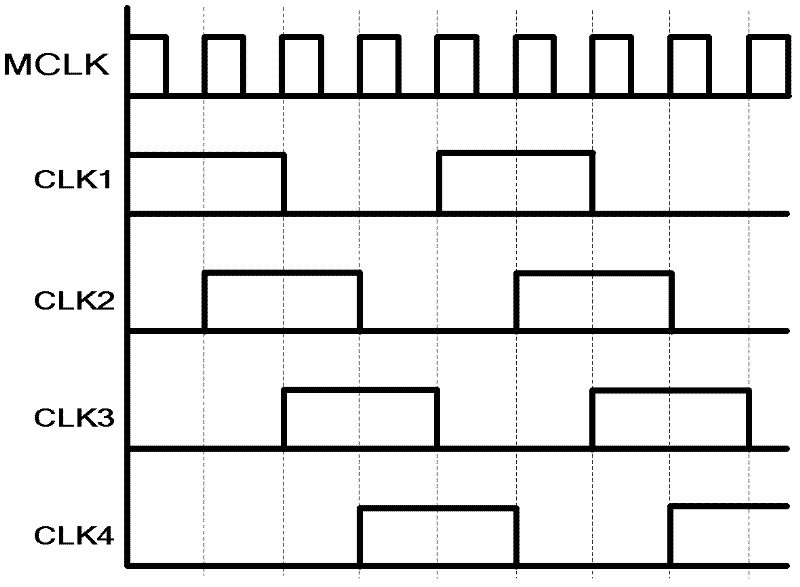

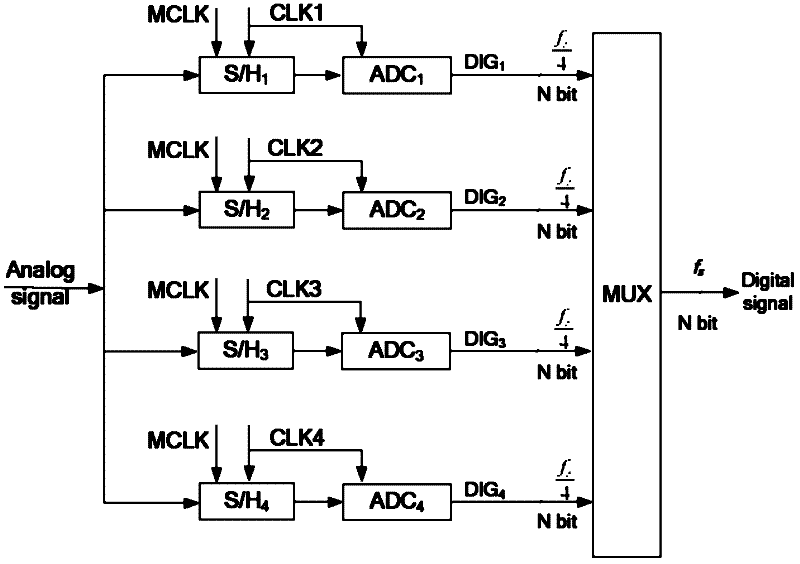

[0020] Such as image 3 Shown is the four-channel time interleaved analog-to-digital converter proposed by the present invention, and its timing diagram is as follows Figure 4 Shown. Figure 4 In, the duty cycle of each channel clock is 25%, and in each sampling clock phase, there is always only one channel sampling, so the input signal load is reduced and the input bandwidth is increased. Compared to traditional time-interleaved analog-to-digital converters (such as figure 1 Shown), image 3 The sampling and holding circuit of each channel is controlled by the channel clock CLKi (i means different channels, i=1, 2, 3, 4) and the master clock MCLK, and the sampling time of each channel is determined by MCLK. The specific working method takes channel one as an example, and the other channels work in the same manner.

[0021] The sample and hold circuit structure of channel one is as foll...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More