Self-alignment channel doping for restraining CMOS (Complementary Metal Oxide Semiconductor) short channel effect and preparation method thereof

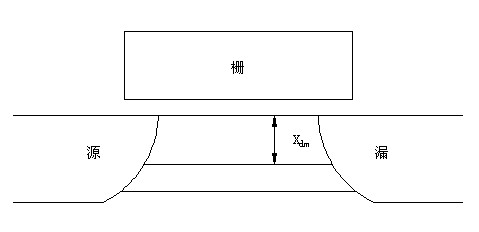

A short channel effect and channel doping technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of increasing source-substrate junction depth Xj, affecting source-substrate, and increasing source-drain parasitic resistance and other problems to achieve the effect of suppressing short channel effect and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

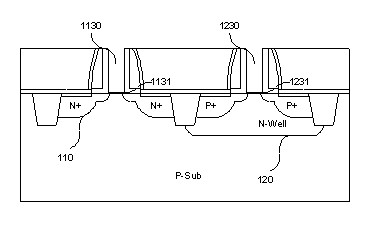

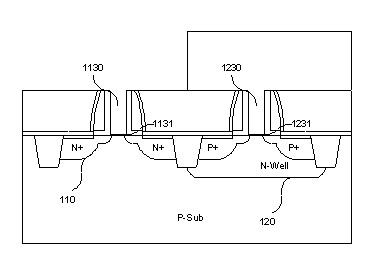

[0035] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings:

[0036] A self-aligned channel doping suppresses CMOS short channel effect and a preparation method thereof, wherein:

[0037] A back gate high dielectric constant CMOS structure including a first transistor 110 and a second transistor 120 is formed on a silicon substrate; wherein, the substrate is set as a P-type silicon substrate.

[0038] Further, the first transistor 110 is set as an NMOS tube, and the second transistor 120 is set as a PMOS tube.

[0039] figure 2 It is the structural schematic diagram of the self-aligned channel doping suppressing CMOS short channel effect and the preparation method of the present invention after step a, please refer to figure 2 , Step a: Remove the sample gate in the first transistor gate trench 1130 of the first transistor 110 device and the second transistor gate trench 1230 of the second transistor 120 devi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More