Device for debugging wafer-level test scheme under final test environment of automatic test device

A technology of automatic testing device and testing scheme, which is applied in the field of semiconductors, can solve the problems that probe cards are difficult to provide and takes a long time, and achieve the effects of convenient development and debugging, simple structure, and short debugging time period

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the technical means, creative features, objectives and effects achieved by the present invention easy to understand, the present invention will be further elaborated below.

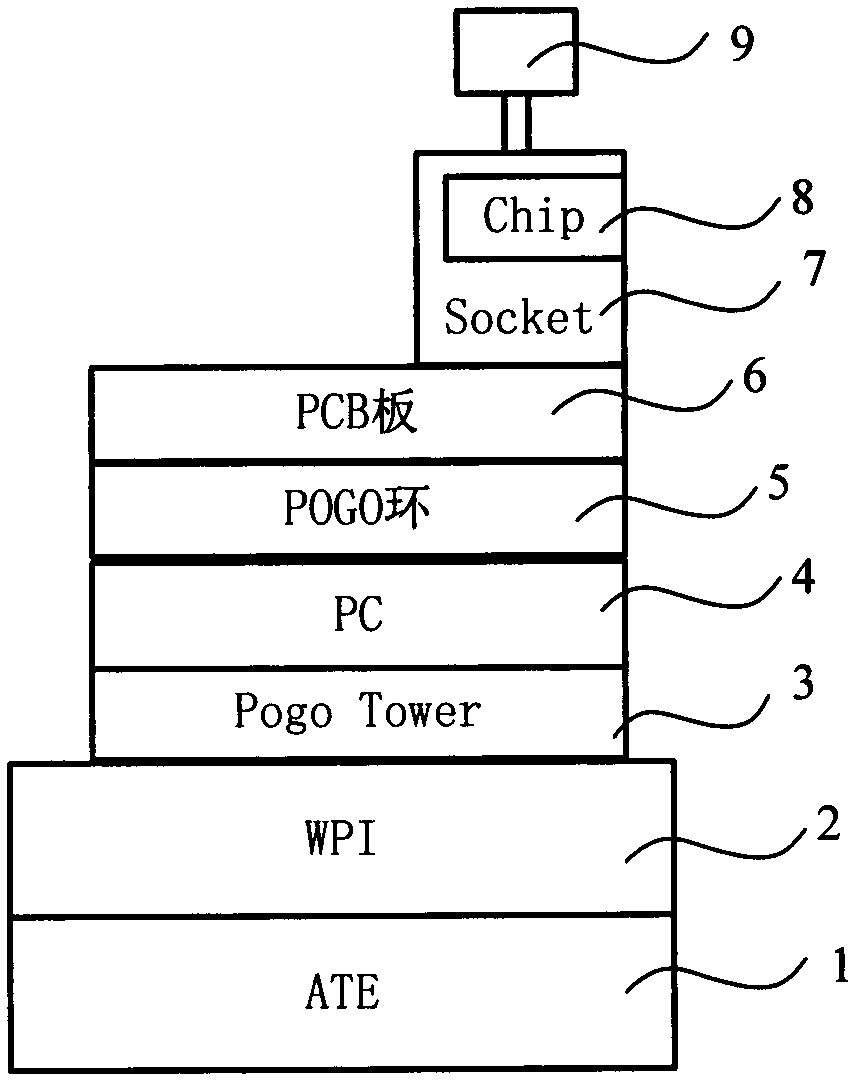

[0037] Figure 1 to Figure 7 A schematic structural view of the testing device of the present invention is shown. The test device consists of the following parts from bottom to top:

[0038] Automatic Test Equipment (ATE) 1,

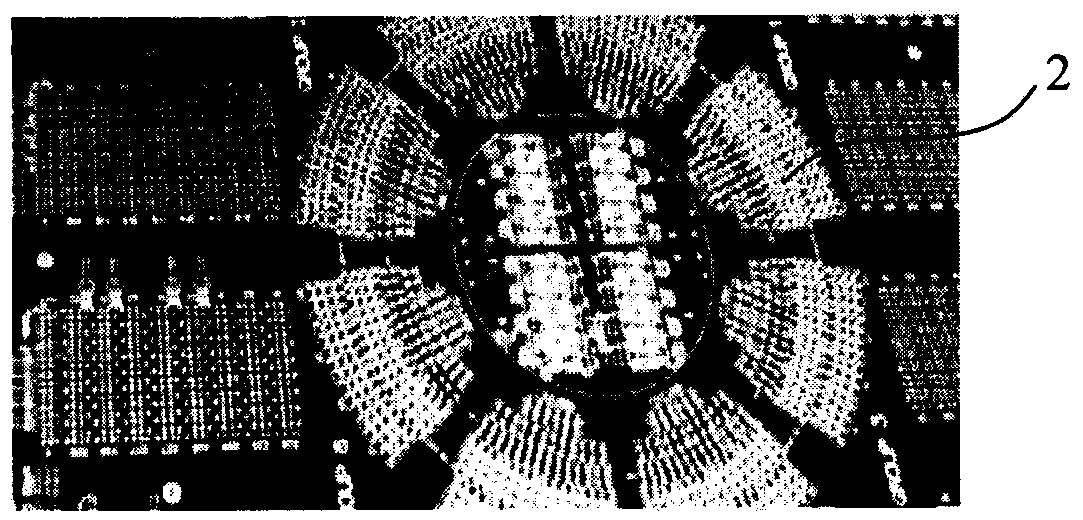

[0039] Chip test board 2 (Wafer Prober Interface, hereinafter referred to as WPI board); installed on the ATE1, figure 2 for the schematic diagram.

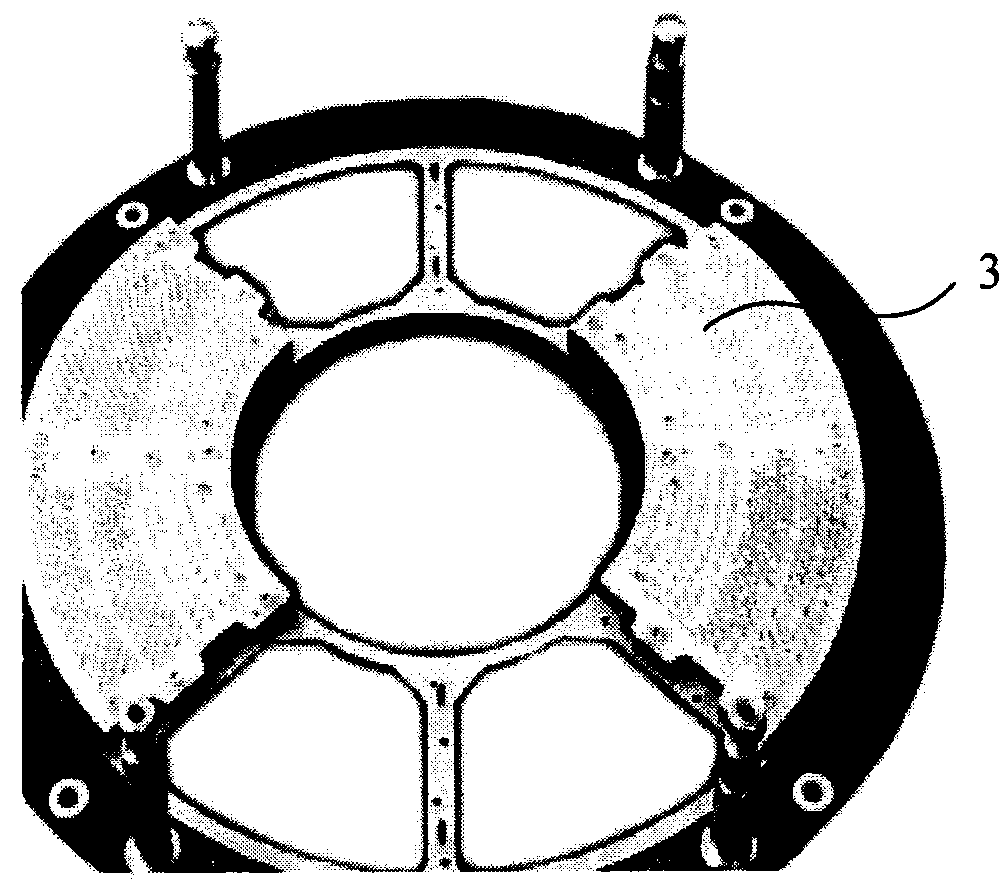

[0040] Test spring pin ring 3 (hereinafter referred to as Pogo Tower), installed on the WPI board 2; image 3 for the schematic diagram.

[0041] Probe Card 4 (Probe Card, referred to as PC), installed on the Pogo Tower3, fixed with screws; Figure 4 for the schematic diagram.

[0042] Probe ring 5 (hereinafter referred to as Pogo ring), for debugging, align through the screw mounting holes of probe card...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com