Manufacturing method of NMOS (N-channel metal oxide semiconductor) transistor

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as insufficient suppression of hot carrier injection effects, improve HCI effects, improve interface quality, and prevent accumulation of charges Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

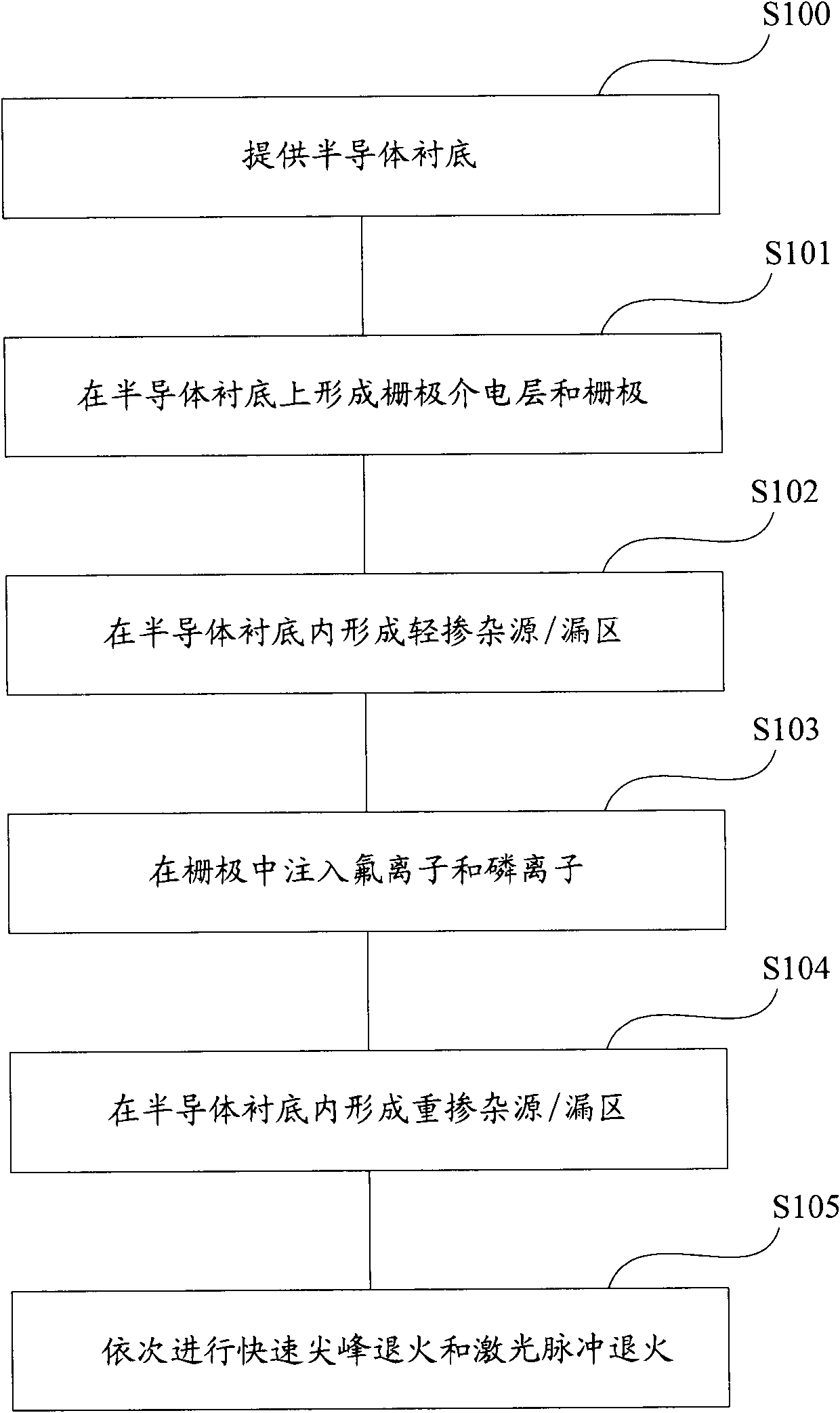

[0028] Such as figure 1 As shown, the manufacturing method of the NMOS transistor in this embodiment includes the following steps:

[0029] S100, providing a semiconductor substrate;

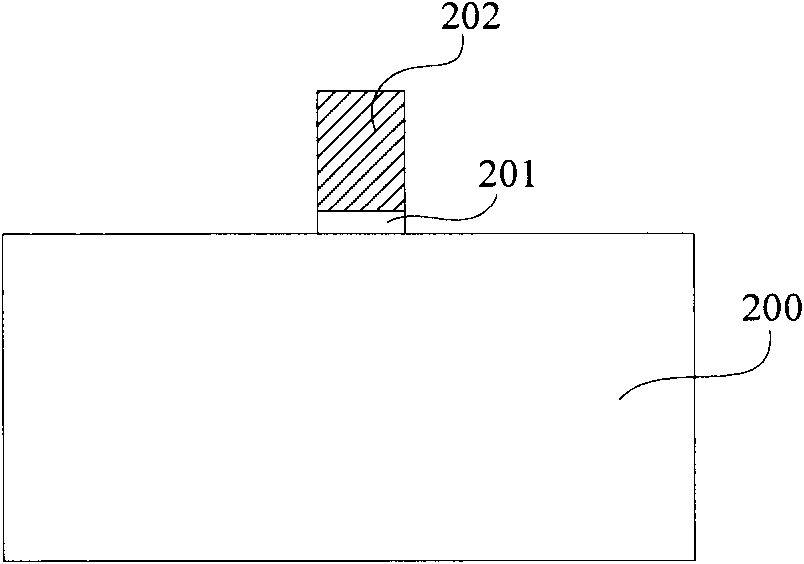

[0030] S101, forming a gate dielectric layer and a gate on the gate dielectric layer on the semiconductor substrate;

[0031] S102, performing lightly doped ion implantation in the semiconductor substrate on both sides of the gate to form lightly doped source / drain regions;

[0032] S103, implanting fluorine ions and phosphorus ions into the gate;

[0033] S104, performing heavily doped ion implantation in the semiconductor substrate on both sides of the gate to form heavily doped source / drain regions;

[0034] S105, performing rapid spike annealing and laser pulse annealing in sequence.

[0035] refer to figure 2 , first execute step S100 to provide a semiconductor substrate 200 . Wherein, the semiconductor substrate 200 is silicon formed with semiconductor devices, silicon-on-insulator ...

Embodiment 2

[0057] Such as Figure 10 As shown, the manufacturing method of the NMOS transistor in this embodiment includes the following steps:

[0058] S300, providing a semiconductor substrate;

[0059] S301, forming a gate dielectric layer and a gate on the gate dielectric layer on the semiconductor substrate;

[0060] S302, performing lightly doped ion implantation in the semiconductor substrate on both sides of the gate to form lightly doped source / drain regions;

[0061] S303, performing heavily doped ion implantation in the semiconductor substrate on both sides of the gate to form heavily doped source / drain regions;

[0062] S304, implanting fluorine ions and phosphorus ions into the grid;

[0063] S305, performing rapid spike annealing and laser pulse annealing in sequence.

[0064] The difference between this embodiment and Embodiment 1 lies in the steps of "implanting heavily doped ions into the semiconductor substrate on both sides of the gate to form heavily doped source / ...

Embodiment 3

[0067] Such as Figure 11 As shown, the manufacturing method of the NMOS transistor in this embodiment includes the following steps:

[0068] S400, providing a semiconductor substrate;

[0069] S401, forming a gate dielectric layer and a gate on the gate dielectric layer on the semiconductor substrate;

[0070] S402, implanting fluorine ions and phosphorus ions into the grid;

[0071] S403, performing lightly doped ion implantation in the semiconductor substrate on both sides of the gate to form lightly doped source / drain regions;

[0072] S404, performing heavily doped ion implantation in the semiconductor substrate on both sides of the gate to form heavily doped source / drain regions;

[0073] S405, performing rapid spike annealing and laser pulse annealing in sequence.

[0074] The difference between this embodiment and Embodiment 1 is only in the steps of "implanting lightly doped ions into the semiconductor substrate on both sides of the gate to form lightly doped sour...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More