Double-embedding structure and formation method thereof

A dual damascene structure and graphics technology, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve problems such as difficult process control, affecting device performance, difficult electromigration and stress migration, etc., and achieves easy process Controlling, increasing feature size, reducing the effect of potential for electromigration and stress migration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

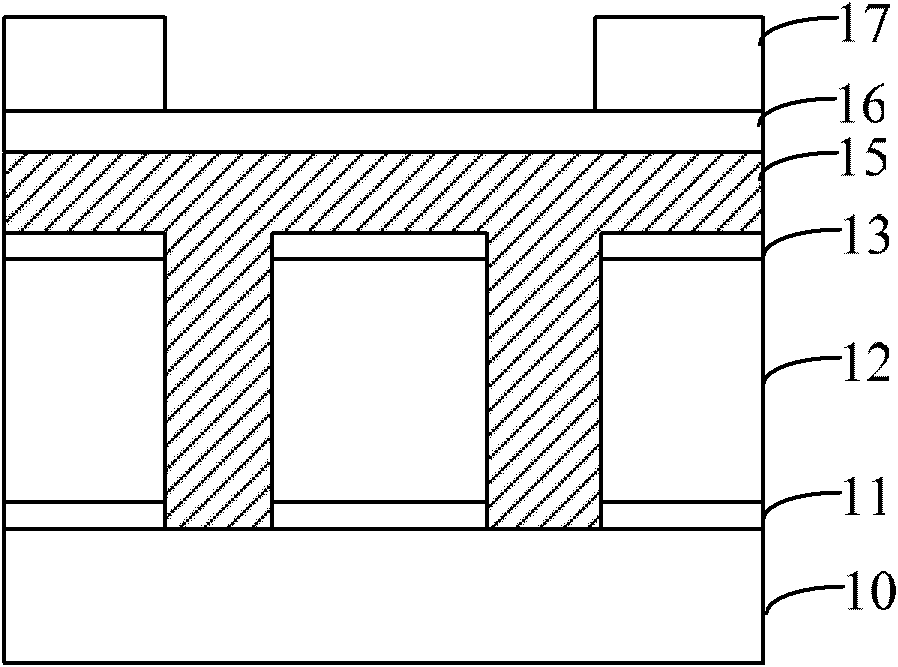

[0061] According to the method for forming a dual damascene structure according to a specific embodiment of the present invention, the etched dielectric layer below the formed trench (that is, the etched dielectric layer between the trench and the substrate) has a layer between the top surface and the bottom surface. The slope, due to the existence of the slope, can reduce the possibility of electromigration and stress migration; moreover, due to the existence of the slope, it is equivalent to increasing the characteristic size of the through hole, which can further reduce the generation of electromigration and stress migration possibility.

[0062] Moreover, in a specific embodiment, the method for forming a dual damascene structure uses the first step of etching and the second step of etching to form a trench, so that the etched dielectric layer under the trench has a layer between the top surface and the bottom surface. The height of the through hole is not reduced, that is...

PUM

| Property | Measurement | Unit |

|---|---|---|

| angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More