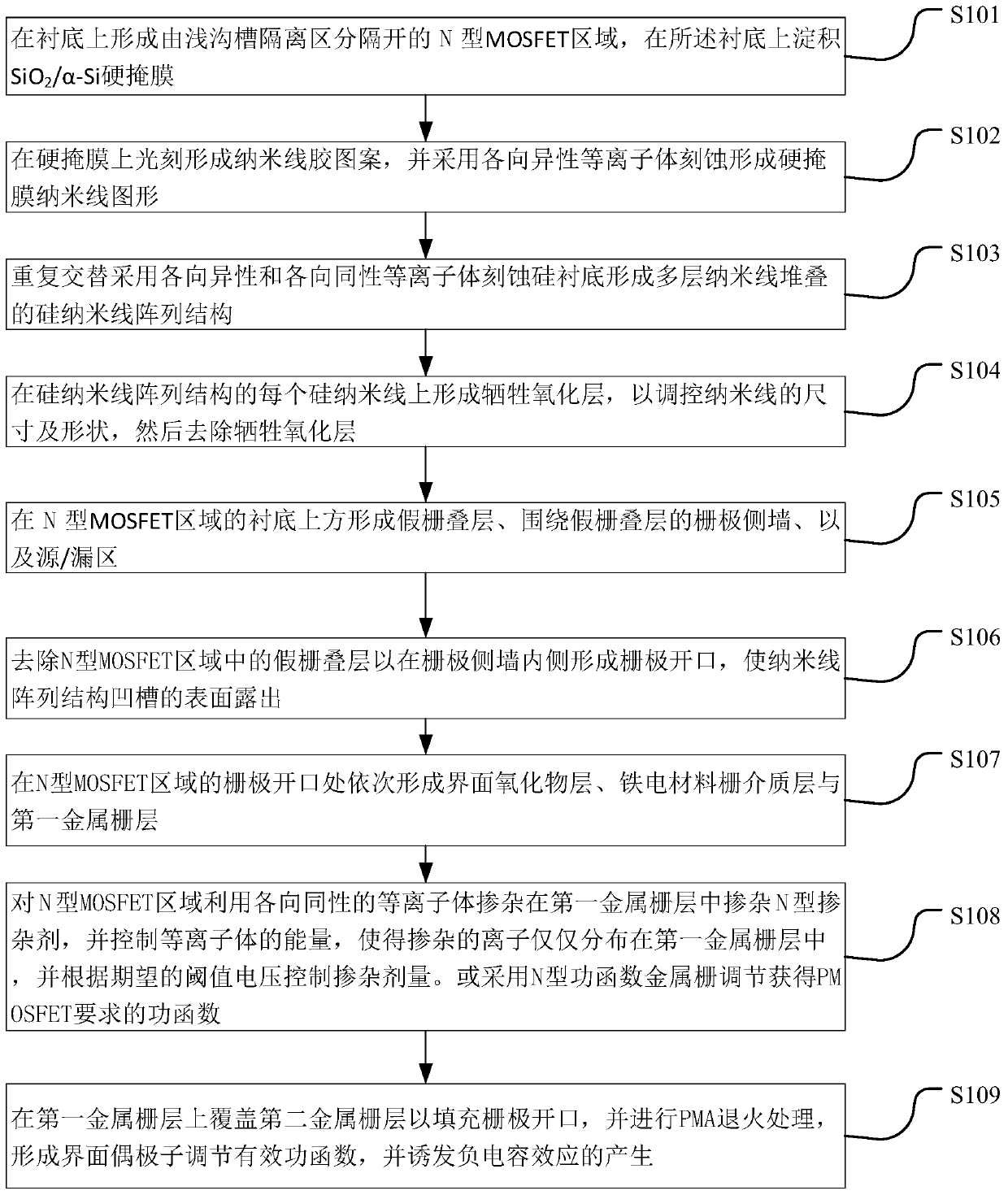

Fabrication method of field-effect transistor and field-effect transistor

A technology of field effect transistors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to achieve the effects of good industrialization prospects, low cost, and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

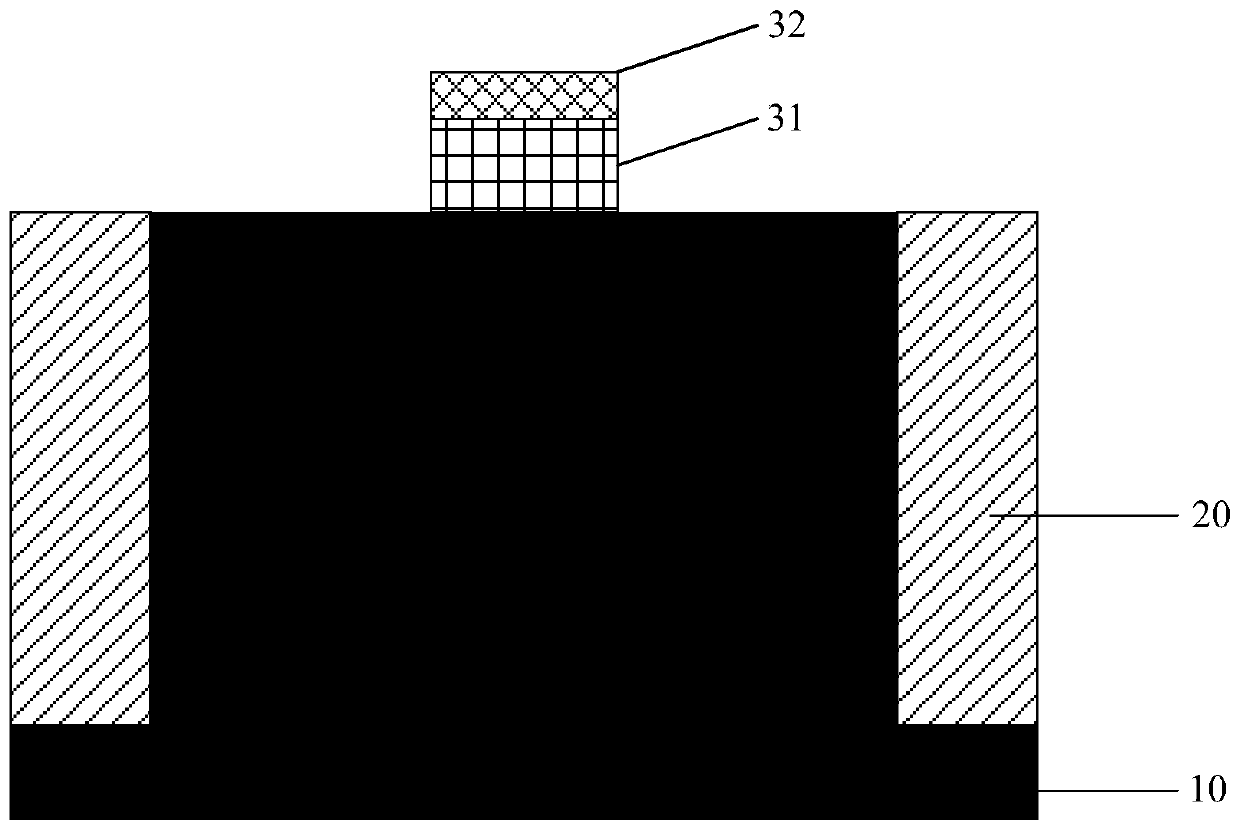

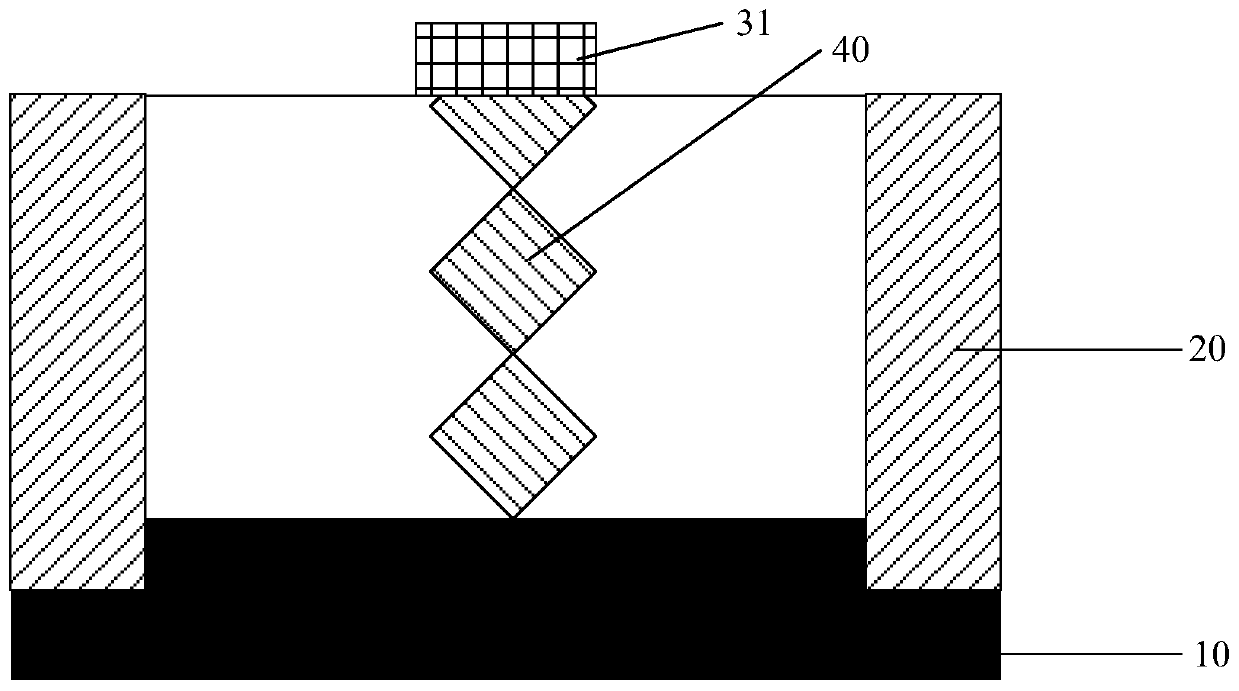

[0064] The present disclosure is to provide a ferroelectric material negative capacitance nanowire array ring gate NMOSFET structure and its manufacturing method, and fabricate a silicon nanowire array structure 40 in the N-type MOSFET region, wherein the silicon nanowire array structure 40 can be adopted by a silicon substrate 10 Anisotropic plasma etching and isotropic plasma etching are alternately etched, and at the same time, it is easier to realize the reduction of nanowire size by controlling the etching parameters, and obtain the desired nanowire size and cross-sectional shape; and through Nanowire sacrificial oxidation, using oxidation stress to further obtain the desired nanowire size and circular cross-sectional shape, to obtain the best gate control characteristics, while removing the surface damage of the nanowire, and retaining the electronic properties of the Si nanowire ring gate NMOSFET Good mobility. Moreover, because the nanowire ring-gate structure greatly ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More