Two-stage FPGA (field programmable gate array) pipeline configuration circuit

A technology for configuring circuits and pipelines. It is applied in the direction of program control devices, machine execution devices, program loading/starting, etc. It can solve the problems of configuring data path control signal regulations, no pipeline architecture concept, and scattered functions of each module, so as to shorten the FPGA. Download and readback time, increase user download and readback clock frequency, and strong data processing capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

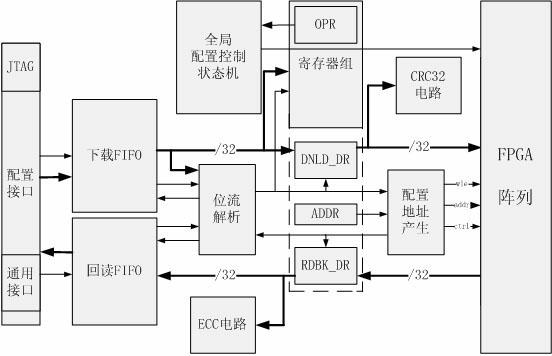

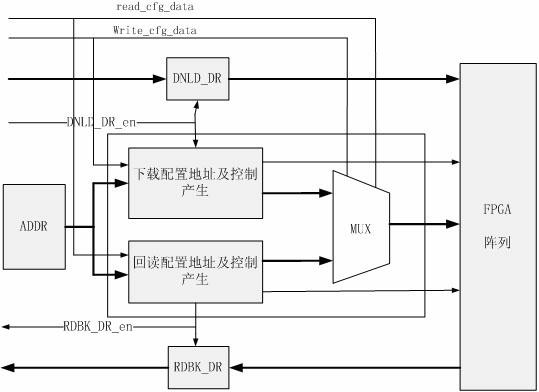

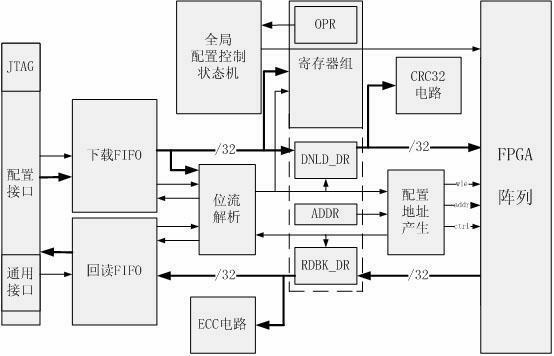

[0020] The configuration circuit of FPGA must not only be able to input configuration data from the user interface into the programming point of the storage array, but also be able to read the content of the programming point and output it from the user interface. The function of the download data channel is to write data into the internal programming point, and the function of the readback data channel is to read the data from the internal programming point.

[0021] The detailed operation procedures of the two data channels are described below.

[0022] Download data channel:

[0023] 1. The user writes the configuration bit stream into the download FIFO through the configuration interface.

[0024] 2. The bit stream analysis module detects the read-empty flag of the download FIFO, and reads the data in the download FIFO if it is not empty.

[0025] 3. The bit stream analysis module parses out the register address, read and write operations, and the number of downloaded da...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More