Heterogeneous design method for optimizing embedded STT- RAM (Spin-Torque Transfer Random Access Memory) performances and hardware consumption

A technology of STT-RAM and design method, applied in the manufacture/processing of electromagnetic devices, static memory, instruments, etc., can solve the problems of packaging and system integration cost, slow access speed, complex flash memory programming control, etc., to achieve effective Conducive to miniaturization and portable design, reduced packaging and board-level hardware consumption, and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

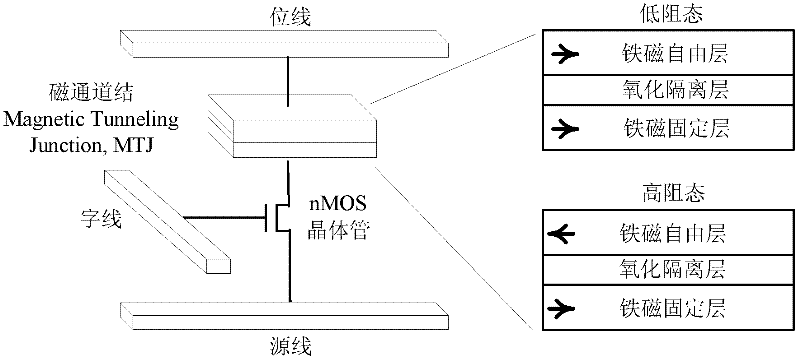

[0026] figure 1 Shown is the memory cell structure of STT-RAM. Usually, each STT-RAM memory cell is composed of a magnetic channel junction (Magnetic Tunneling Junction, MTJ) and a control nMOS transistor. The magnetic channel junction is composed of upper and lower ferromagnetic layers and an oxide layer in the middle. The direction of the magnetic field in one of the ferromagnetic layers can be changed under the action of an electric current, which is called the free layer. The direction of the magnetic field in the ferromagnetic layer of the other layer is fixed, which is called the pinned layer. On the level of STT-RAM storage unit, the present invention proposes two heterogeneous design methods.

[0027] 1. By reducing the area of the magnetic channel junction free layer, the write delay and energy consumption of the magnetic channe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com