Quasi-cyclic low-density parity check code decoder based on FPGA (field-programmable gate array) and decoding method

A decoder and decoding technology, applied in the field of communication, can solve the problems of different occupancy and failure to achieve complete parallel work of processing units, so as to improve the total decoding throughput, shorten the working clock cycle, and improve the utilization rate of BRAM resources Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

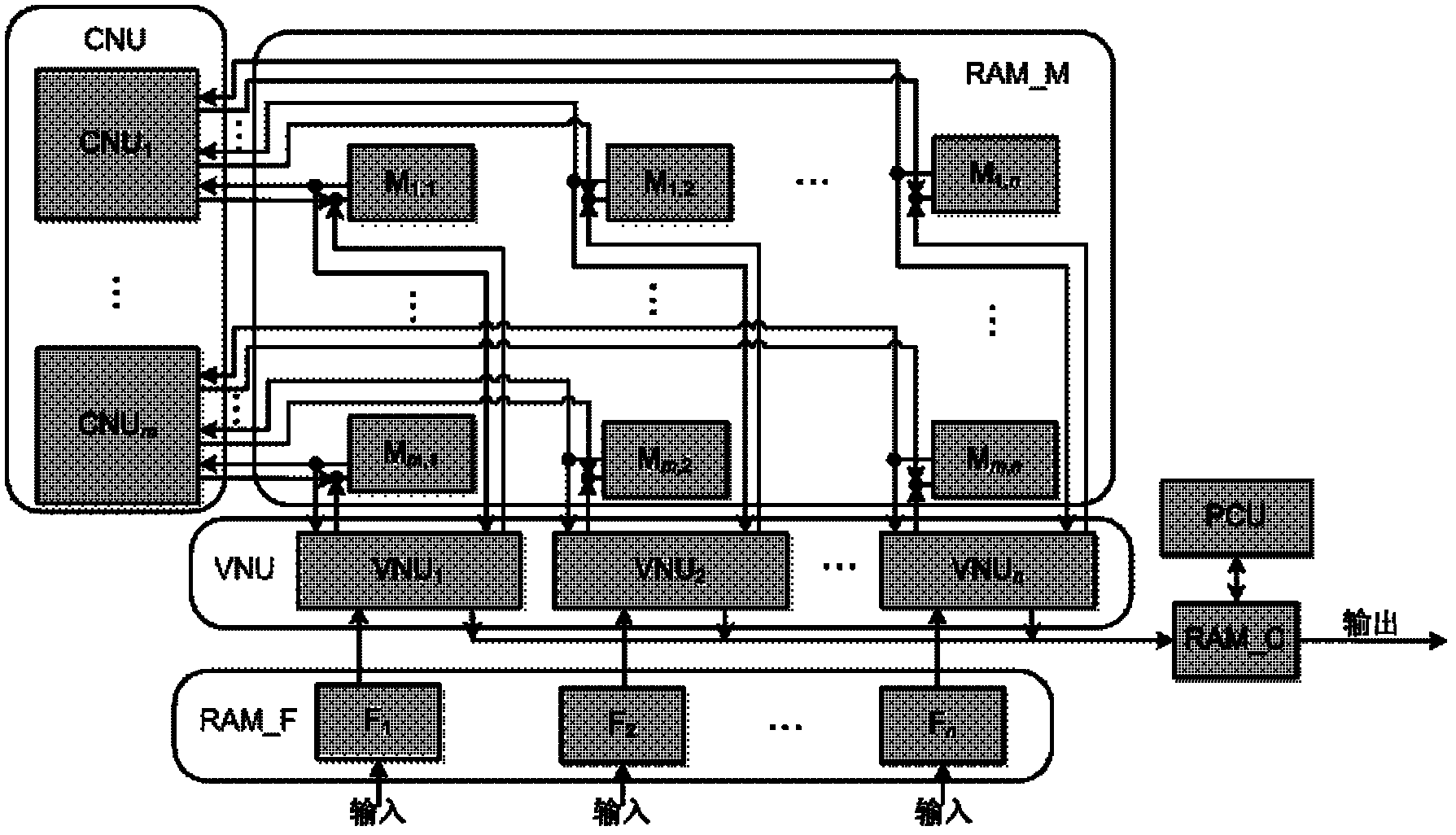

[0040] refer to Figure 5 , the low-storage high-speed decoder structure provided by the present invention mainly includes 6 parts, which are variable node calculation module VNU, check node calculation module CNU, check equation calculation module PCU, channel initial information storage block RAM_F, iterative external information Storage block RAM_M and decoding code word storage block RAM_C. Among them, the variable node calculation module VNU is used to complete the update calculation of the information outside the variable node of the decoding, and it includes n variable node calculation units VNU j , 1≤j≤n, n is the number of column blocks of the base matrix; the check node calculation module CNU is used to complete the update calculation of the information outside the check node for decoding, and it includes m check node calculation units CNU i , 1≤i≤m, m is the number of row blocks of the base matrix; the verification equation calculation module PCU is used to verify ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More